JP7364355B2 - 電圧検出回路 - Google Patents

電圧検出回路 Download PDFInfo

- Publication number

- JP7364355B2 JP7364355B2 JP2019085629A JP2019085629A JP7364355B2 JP 7364355 B2 JP7364355 B2 JP 7364355B2 JP 2019085629 A JP2019085629 A JP 2019085629A JP 2019085629 A JP2019085629 A JP 2019085629A JP 7364355 B2 JP7364355 B2 JP 7364355B2

- Authority

- JP

- Japan

- Prior art keywords

- voltage

- current mirror

- circuit

- resistor

- mirror circuit

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 238000001514 detection method Methods 0.000 title claims description 74

- 238000002955 isolation Methods 0.000 claims description 5

- 238000000926 separation method Methods 0.000 claims description 3

- 238000010586 diagram Methods 0.000 description 10

- 230000015556 catabolic process Effects 0.000 description 4

- 230000000694 effects Effects 0.000 description 2

- 239000002131 composite material Substances 0.000 description 1

- 230000007423 decrease Effects 0.000 description 1

- 230000003247 decreasing effect Effects 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000000630 rising effect Effects 0.000 description 1

- 239000004065 semiconductor Substances 0.000 description 1

Images

Landscapes

- Measurement Of Current Or Voltage (AREA)

- Power Sources (AREA)

- Control Of Electrical Variables (AREA)

Description

まず、電圧検出回路における消費電力の課題について説明する。

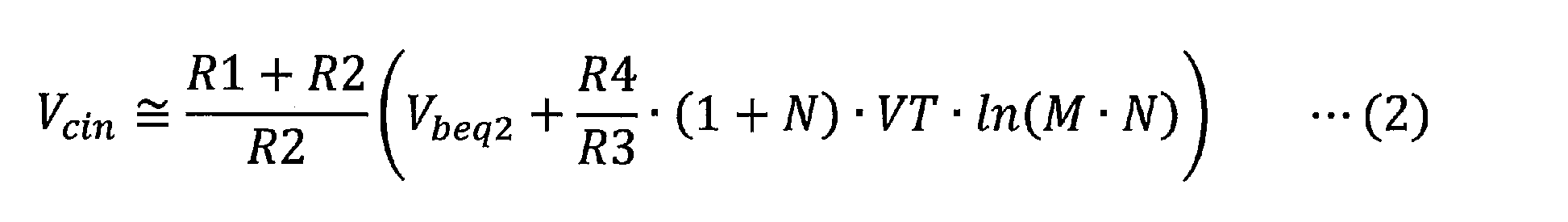

図1は、第1の実施形態の電圧検出回路の構成を示す図である。本実施形態の電圧検出回路は、UVLO回路を構成するものである。電圧検出回路は、バンドギャップ回路を構成する第1のトランジスタQ1及び第2のトランジスタQ2を有する。第1及び第2のトランジスタQ1、Q2は、NPN型のトランジスタにより構成され、互いにベースが接続されている。第1のトランジスタQ1と第2のトランジスタQ2のエミッタ面積比は、例えばM:1となっている。一例として、M=4程度に設定する。第1のトランジスタQ1のコレクタには、PMOS型のトランジスタ(MOSFET)M1、M2による第1カレントミラー回路11(第1カレントミラー回路の入力部の一方)が接続される。また、第2のトランジスタQ2のコレクタには、PMOS型のトランジスタ(MOSFET)M3、M4による第2カレントミラー回路12(第2カレントミラー回路の入力部の一方)が接続される。

図3は、第2の実施形態の電圧検出回路の構成を示す図である。第2の実施形態は、図1に示した第1の実施形態における一部の構成を変更した例である。ここでは、第1の実施形態と異なる部分を中心に説明し、同様の構成及び動作については説明を省略する。

M1、M2、M3、M4、M5:トランジスタ(PMOS型)

M6、M7、M8、M9、M10、M11:トランジスタ(NMOS型)

R1、R2、R3、R4、R5:抵抗

VIN:入力端(電圧入力端)

OUT_UVLO:出力端(検出出力端)

11:第1カレントミラー回路

12:第2カレントミラー回路

13:第3カレントミラー回路

Claims (5)

- 電圧入力端に印加された入力電圧を分圧する第1の抵抗及び第2の抵抗と、

前記第1の抵抗と前記第2の抵抗との間に互いにベースが接続され、バンドギャップ回路を構成する第1のトランジスタ及び第2のトランジスタと、を有し、

前記第1のトランジスタのコレクタに第1カレントミラー回路の入力部の一方が接続され、前記第1カレントミラー回路の入力部の他方が前記電圧入力端に接続され、

前記第2のトランジスタのコレクタに第2カレントミラー回路の入力部の一方が接続され、前記第2カレントミラー回路の入力部の他方が前記電圧入力端に接続され、

前記第1カレントミラー回路の出力部に第3カレントミラー回路の入力部の一方が接続され、前記第3カレントミラー回路の入力部の他方が接地され、

前記第1のトランジスタのエミッタが第3の抵抗及び第4の抵抗を介して接地され、前記第2のトランジスタのエミッタが前記第3の抵抗と前記第4の抵抗の接続ノードに接続されて前記第4の抵抗を介して接地された差動入力回路部と、

前記第2カレントミラー回路の第1出力部と前記第3カレントミラー回路の第1出力部とが互いに接続された接続ノードに設けられる検出出力端と、を有し、

前記入力電圧の変化に伴い、前記第2カレントミラー回路及び前記第3カレントミラー回路の第1出力部の電圧が変化することによって、前記入力電圧が所定の電圧値以上、又は所定の電圧値以下になったことを検出する電圧検出回路であって、

前記第2カレントミラー回路の第1出力部に並列に設けられた第2カレントミラー回路の第2出力部と、

前記第3カレントミラー回路の第1出力部に並列に設けられた第3カレントミラー回路の第2出力部と、

前記第1の抵抗と前記第2の抵抗との間に設けられ、前記第1の抵抗及び前記第2の抵抗に流れる電流を制限することにより、前記第1及び第2のトランジスタのベース電圧を所定値以下にクランプするクランプ回路を構成する電流制限素子と、

前記第2カレントミラー回路の第2出力部と前記第3カレントミラー回路の第2出力部とが互いに接続された接続ノードにゲートが接続され、ソースが接地され、ドレインが第5の抵抗を介して前記電圧入力端に接続された第1のMOSFETを有し、前記入力電圧の変化に伴う前記第2カレントミラー回路及び前記第3カレントミラー回路の第2出力部の電圧の変化によって、前記クランプ回路の動作を制御するクランプ制御素子と、を有する、

電圧検出回路。 - 請求項1に記載の電圧検出回路であって、

前記電流制限素子は、前記第1の抵抗にドレインが接続され、ソースが前記第1のトランジスタ及び前記第2のトランジスタのベースと前記第2の抵抗とに接続され、ゲートが前記第1のMOSFETのドレインと前記第5の抵抗とに接続された第2のMOSFETを有し、

前記第1のMOSFETは、前記入力電圧の変化に応じて前記第2のMOSFETのゲート電圧を制御し、前記第2のMOSFETは、ゲート電圧に応じてドレイン電流が変化し、前記第1の抵抗及び前記第2の抵抗に流れる電流を制限するものであり、前記検出出力端の出力電圧が反転する第1の電圧値よりも大きい第2の電圧値以上の電圧において前記クランプ回路を動作させる、

電圧検出回路。 - 請求項1又は2に記載の電圧検出回路であって、

前記第3カレントミラー回路の第1出力部及び第2出力部は、それぞれMOSFETにより構成され、2つのMOSFETのゲート幅の比は、1:N(N>1)である、

電圧検出回路。 - 請求項1に記載の電圧検出回路であって、

前記電圧入力端と前記第1カレントミラー回路及び前記第2カレントミラー回路の入力部の他方との間に設けられ、前記第1カレントミラー回路の入力部の他方及び前記第2カレントミラー回路の入力部の他方である電源入力部を分離する電源分離素子を、さらに有する、

電圧検出回路。 - 請求項4に記載の電圧検出回路であって、

前記クランプ制御素子は、前記第2カレントミラー回路の第2出力部と前記第3カレントミラー回路の第2出力部との接続ノードにゲートが接続され、ソースが接地され、ドレインが第5の抵抗を介して前記電圧入力端に接続された第1のMOSFETを有し、

前記電流制限素子は、前記第1の抵抗にドレインが接続され、ソースが前記第1及び第2のトランジスタのベースと前記第2の抵抗とに接続され、ゲートが前記第1のMOSFETのドレインと前記第5の抵抗とに接続された第2のMOSFETを有し、

前記電源分離素子は、前記電圧入力端にドレインが接続され、ソースが前記第1カレントミラー回路及び前記第2カレントミラー回路の入力部の他方に接続され、ゲートが前記第2のMOSFETのゲートと共に前記第1のMOSFETのドレイン及び前記第5の抵抗に接続された第3のMOSFETを有する、

電圧検出回路。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2019085629A JP7364355B2 (ja) | 2019-04-26 | 2019-04-26 | 電圧検出回路 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2019085629A JP7364355B2 (ja) | 2019-04-26 | 2019-04-26 | 電圧検出回路 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2020180932A JP2020180932A (ja) | 2020-11-05 |

| JP7364355B2 true JP7364355B2 (ja) | 2023-10-18 |

Family

ID=73023958

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2019085629A Active JP7364355B2 (ja) | 2019-04-26 | 2019-04-26 | 電圧検出回路 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP7364355B2 (ja) |

Families Citing this family (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN115328265B (zh) * | 2021-05-11 | 2024-04-12 | 圣邦微电子(北京)股份有限公司 | 一种使用子带隙电压的低压uvlo电路及方法 |

| US20250379500A1 (en) * | 2024-06-07 | 2025-12-11 | Qualcomm Incorporated | Adaptive drive control for switching regulators |

Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2000065872A (ja) | 1998-08-20 | 2000-03-03 | Fuji Electric Co Ltd | 電圧検出回路 |

| JP2007133533A (ja) | 2005-11-09 | 2007-05-31 | Nec Electronics Corp | 基準電圧生成回路 |

| WO2012083781A1 (en) | 2010-12-22 | 2012-06-28 | Csmc Technologies Fab1 Co., Ltd | Voltage comparator |

| CN105021862A (zh) | 2014-12-09 | 2015-11-04 | 北京中电华大电子设计有限责任公司 | 超低功耗电压检测电路 |

| CN106855586A (zh) | 2016-12-20 | 2017-06-16 | 宁波芯路通讯科技有限公司 | 低压检测电路 |

-

2019

- 2019-04-26 JP JP2019085629A patent/JP7364355B2/ja active Active

Patent Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2000065872A (ja) | 1998-08-20 | 2000-03-03 | Fuji Electric Co Ltd | 電圧検出回路 |

| JP2007133533A (ja) | 2005-11-09 | 2007-05-31 | Nec Electronics Corp | 基準電圧生成回路 |

| WO2012083781A1 (en) | 2010-12-22 | 2012-06-28 | Csmc Technologies Fab1 Co., Ltd | Voltage comparator |

| CN105021862A (zh) | 2014-12-09 | 2015-11-04 | 北京中电华大电子设计有限责任公司 | 超低功耗电压检测电路 |

| CN106855586A (zh) | 2016-12-20 | 2017-06-16 | 宁波芯路通讯科技有限公司 | 低压检测电路 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP2020180932A (ja) | 2020-11-05 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| TWI489239B (zh) | 電壓調節器 | |

| JP5516320B2 (ja) | レギュレータ用半導体集積回路 | |

| CN100543632C (zh) | 采用cmos技术中电流模式技术的精确电压/电流参考电路 | |

| US7602162B2 (en) | Voltage regulator with over-current protection | |

| TWI437403B (zh) | Voltage regulator | |

| US8269478B2 (en) | Two-terminal voltage regulator with current-balancing current mirror | |

| TW201107920A (en) | Voltage regulator | |

| TWI818034B (zh) | 逆流防止電路以及電源電路 | |

| US20110050197A1 (en) | Reference current or voltage generation circuit | |

| US20230246640A1 (en) | Wide voltage gate driver using low gate oxide transistors | |

| US6954058B2 (en) | Constant current supply device | |

| JP7364355B2 (ja) | 電圧検出回路 | |

| US7816897B2 (en) | Current limiting circuit | |

| JPH06324092A (ja) | ヒステリシス回路及びそれを備えた電源供給システム | |

| TWI672572B (zh) | 電壓調節器 | |

| JP2009296714A (ja) | 低電圧検出回路および電源制御用半導体集積回路 | |

| JP2002074967A (ja) | 降圧電源回路 | |

| US10175714B2 (en) | Enable signal generation circuit | |

| CN116301171B (zh) | 一种零温度系数的低压欠压锁定电路及方法 | |

| KR102658159B1 (ko) | 과열 보호 회로 및 이것을 구비한 반도체 장치 | |

| JP4167122B2 (ja) | 基準電圧発生回路 | |

| US20250038514A1 (en) | Short-Circuit Protection Having Wide Common Mode Voltage | |

| US20190288501A1 (en) | Semiconductor integrated circuit | |

| JP2021096554A (ja) | 定電流回路 | |

| JP4249599B2 (ja) | 基準電圧回路 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20220408 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20230228 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20230404 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20230512 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20230627 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20230714 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20230905 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20231005 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 7364355 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |