KR20140082012A - 태양 전지 및 이의 제조 방법 - Google Patents

태양 전지 및 이의 제조 방법 Download PDFInfo

- Publication number

- KR20140082012A KR20140082012A KR1020120150835A KR20120150835A KR20140082012A KR 20140082012 A KR20140082012 A KR 20140082012A KR 1020120150835 A KR1020120150835 A KR 1020120150835A KR 20120150835 A KR20120150835 A KR 20120150835A KR 20140082012 A KR20140082012 A KR 20140082012A

- Authority

- KR

- South Korea

- Prior art keywords

- layer

- photoelectric conversion

- conversion portion

- electrode

- band gap

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Ceased

Links

- 238000004519 manufacturing process Methods 0.000 title 1

- 238000000034 method Methods 0.000 title 1

- 238000006243 chemical reaction Methods 0.000 abstract 10

- 239000004065 semiconductor Substances 0.000 abstract 2

- 239000013078 crystal Substances 0.000 abstract 1

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10F—INORGANIC SEMICONDUCTOR DEVICES SENSITIVE TO INFRARED RADIATION, LIGHT, ELECTROMAGNETIC RADIATION OF SHORTER WAVELENGTH OR CORPUSCULAR RADIATION

- H10F10/00—Individual photovoltaic cells, e.g. solar cells

- H10F10/10—Individual photovoltaic cells, e.g. solar cells having potential barriers

- H10F10/19—Photovoltaic cells having multiple potential barriers of different types, e.g. tandem cells having both PN and PIN junctions

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10F—INORGANIC SEMICONDUCTOR DEVICES SENSITIVE TO INFRARED RADIATION, LIGHT, ELECTROMAGNETIC RADIATION OF SHORTER WAVELENGTH OR CORPUSCULAR RADIATION

- H10F10/00—Individual photovoltaic cells, e.g. solar cells

- H10F10/10—Individual photovoltaic cells, e.g. solar cells having potential barriers

- H10F10/14—Photovoltaic cells having only PN homojunction potential barriers

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10F—INORGANIC SEMICONDUCTOR DEVICES SENSITIVE TO INFRARED RADIATION, LIGHT, ELECTROMAGNETIC RADIATION OF SHORTER WAVELENGTH OR CORPUSCULAR RADIATION

- H10F10/00—Individual photovoltaic cells, e.g. solar cells

- H10F10/10—Individual photovoltaic cells, e.g. solar cells having potential barriers

- H10F10/14—Photovoltaic cells having only PN homojunction potential barriers

- H10F10/142—Photovoltaic cells having only PN homojunction potential barriers comprising multiple PN homojunctions, e.g. tandem cells

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10F—INORGANIC SEMICONDUCTOR DEVICES SENSITIVE TO INFRARED RADIATION, LIGHT, ELECTROMAGNETIC RADIATION OF SHORTER WAVELENGTH OR CORPUSCULAR RADIATION

- H10F19/00—Integrated devices, or assemblies of multiple devices, comprising at least one photovoltaic cell covered by group H10F10/00, e.g. photovoltaic modules

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10F—INORGANIC SEMICONDUCTOR DEVICES SENSITIVE TO INFRARED RADIATION, LIGHT, ELECTROMAGNETIC RADIATION OF SHORTER WAVELENGTH OR CORPUSCULAR RADIATION

- H10F71/00—Manufacture or treatment of devices covered by this subclass

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10F—INORGANIC SEMICONDUCTOR DEVICES SENSITIVE TO INFRARED RADIATION, LIGHT, ELECTROMAGNETIC RADIATION OF SHORTER WAVELENGTH OR CORPUSCULAR RADIATION

- H10F71/00—Manufacture or treatment of devices covered by this subclass

- H10F71/10—Manufacture or treatment of devices covered by this subclass the devices comprising amorphous semiconductor material

- H10F71/103—Manufacture or treatment of devices covered by this subclass the devices comprising amorphous semiconductor material including only Group IV materials

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10F—INORGANIC SEMICONDUCTOR DEVICES SENSITIVE TO INFRARED RADIATION, LIGHT, ELECTROMAGNETIC RADIATION OF SHORTER WAVELENGTH OR CORPUSCULAR RADIATION

- H10F71/00—Manufacture or treatment of devices covered by this subclass

- H10F71/121—The active layers comprising only Group IV materials

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y02—TECHNOLOGIES OR APPLICATIONS FOR MITIGATION OR ADAPTATION AGAINST CLIMATE CHANGE

- Y02E—REDUCTION OF GREENHOUSE GAS [GHG] EMISSIONS, RELATED TO ENERGY GENERATION, TRANSMISSION OR DISTRIBUTION

- Y02E10/00—Energy generation through renewable energy sources

- Y02E10/50—Photovoltaic [PV] energy

- Y02E10/544—Solar cells from Group III-V materials

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y02—TECHNOLOGIES OR APPLICATIONS FOR MITIGATION OR ADAPTATION AGAINST CLIMATE CHANGE

- Y02E—REDUCTION OF GREENHOUSE GAS [GHG] EMISSIONS, RELATED TO ENERGY GENERATION, TRANSMISSION OR DISTRIBUTION

- Y02E10/00—Energy generation through renewable energy sources

- Y02E10/50—Photovoltaic [PV] energy

- Y02E10/547—Monocrystalline silicon PV cells

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y02—TECHNOLOGIES OR APPLICATIONS FOR MITIGATION OR ADAPTATION AGAINST CLIMATE CHANGE

- Y02P—CLIMATE CHANGE MITIGATION TECHNOLOGIES IN THE PRODUCTION OR PROCESSING OF GOODS

- Y02P70/00—Climate change mitigation technologies in the production process for final industrial or consumer products

- Y02P70/50—Manufacturing or production processes characterised by the final manufactured product

Landscapes

- Photovoltaic Devices (AREA)

Abstract

Description

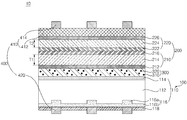

도 2는 도 1의 태양 전지의 전면을 도시한 평면도이다.

도 3는 결정질 실리콘 기반의 제1 광전 변환부만을 포함하는 태양 전지의 일례의 회로이다.

도 4은 결정질 실리콘 기반의 제1 광전 변환부와 비정질 실리콘 기반의 제2 변환 부분을 포함하는 제2 광전 변환부를 포함하는 태양 전지의 일례의 회로이다.

도 5는 본 발명의 실시예로서, 결정질 실리콘 기반의 제1 광전 변환부와 비정질 실리콘 기반의 제1 및 제2 변환 부분을 포함하는 제2 광전 변환부를 포함하는 태양 전지의 일례의 회로이다.

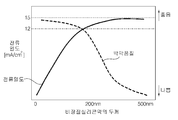

도 6는 비정질 실리콘 박막의 두께에 따른 전류 밀도 및 박막 품질의 경향을 보여주는 그래프이다.

도 7은 본 발명의 다른 실시예에 따른 태양 전지의 부분 단면도이다.

도 8은 본 발명의 또 다른 실시예에 따른 태양 전지의 부분 단면도이다.

도 9는 본 발명의 또 다른 실시예에 따른 태양 전지의 부분 단면도이다.

100: 제1 광전 변환부

200: 제2 광전 변환부

300: 접합층

Claims (39)

- 결정질 반도체를 기반으로 하는 제1 광전 변환부;

상기 제1 광전 변환부 위에 형성되며, 비정질 반도체를 기반으로 하는 복수의 변환 부분을 포함하는 제2 광전부;

상기 제1 광전 변환부와 상기 제2 광전 변환부 사이에 상기 제1 광전 변환부와 상기 제2 광전 변환부를 연결하는 접합층; 및

상기 제1 및 제2 광전 변환부에 전기적으로 연결되는 전극;

을 포함하는 태양 전지. - 제1항에 있어서,

상기 접합층은 비정질 매트릭스에 미세 결정 반도체가 석출된 형태를 가지는 태양 전지. - 제2항에 있어서,

상기 비정질 매트릭스가 비정질 실리콘 산화물 및 비정질 실리콘 탄화물 중 적어도 하나를 포함하는 태양 전지. - 제2항에 있어서,

상기 접합층에서 상기 미세 결정 반도체의 부피 분율이 5% 내지 30%인 태양 전지. - 제2항에 있어서,

상기 제1 광전 변환부는, 제1 도전형을 가지는 베이스 영역과, 상기 제1 도전형과 반대되는 제2 도전형을 가지는 에미터층을 포함하고,

상기 접합층은 상기 에미터층 위에 위치하며 상기 제1 도전형을 가지는 태양 전지. - 제2항에 있어서,

상기 접합층의 굴절률이 1.6~1.9인 태양 전지. - 제1항에 있어서,

상기 제1 광전 변환부는, 제1 도전형을 가지는 베이스 영역을 구비하는 반도체 기판과, 상기 반도체 기판에 형성되며 상기 제1 도전형과 반대되는 제2 도전형을 가지는 포함하는 에미터층을 포함하는 태양 전지. - 제1항에 있어서,

상기 제1 광전 변환부가 다결정 또는 단결정 실리콘을 포함하고,

상기 제1 광전 변환부의 밴드 갭이 1.0eV 내지 1.2eV인 태양 전지. - 제1항에 있어서,

상기 제2 광전 변환부의 상기 복수의 변환 부분은 상기 제1 광전 변환부의 밴드 갭보다 큰 밴드 갭을 가지고, 상기 제1 광전 변환부로부터 멀어질수록 밴드 갭이 더 커지는 태양 전지. - 제1항에 있어서,

상기 제1 광전 변환부의 전류 밀도에 대한 상기 복수의 변환 부분 각각의 전류 밀도의 비율이 0.8 내지 1.2인 태양 전지. - 제1항에 있어서,

상기 복수의 변환 부분은, 상기 제1 광전 변환부 위에 형성되며 제1 밴드 갭을 가지는 제1 변환 부분과, 상기 제1 변환 부분 위에 형성되며 상기 제1 밴드 갭보다 큰 제2 밴드 갭을 가지는 제2 변환 부분을 포함하는 태양 전지. - 제11항에 있어서,

상기 제1 변환 부분의 제1 진성층은 게르마늄을 포함하는 비정질 실리콘층을 포함하고,

상기 제1 변환 부분의 제2 진성층은 도핑되지 않은 비정질 실리콘층을 포함하는 태양 전지. - 제12항에 있어서,

상기 제1 진성층에서 상기 게르마늄의 원자 함량비가 15% 내지 40%인 태양 전지. - 제11항에 있어서,

상기 제1 밴드 갭이 1.2eV 내지 1.6eV이고,

상기 제2 밴드 갭이 1.6eV 내지 1.9eV인 태양 전지. - 제11항에 있어서,

상기 제1 광전 변환 부분의 제1 진성층보다 상기 제2 광전 변환 부분의 제2 진성층의 두께가 얇은 두꺼운 태양 전지. - 제15항에 있어서,

상기 제1 진성층의 두께가 100nm 내지 350nm이고,

상기 제2 진성층의 두께가 50nm 내지 300nm인 태양 전지. - 제11항에 있어서,

상기 제1 변환 부분은, 상기 제1 광전 변환부 위에 차례로 형성되는 제1 하부층, 제1 진성층 및 제1 상부층을 포함하여 pin 또는 nip 접합 구조를 형성하고,

상기 제2 변환 부분은, 상기 제1 변환 부분 위에 차례로 형성되는 제2 하부층, 제2 진성층 및 제2 상부층을 포함하여 pin 또는 nip 접합 구조를 형성하고,

상기 제1 상부층 및 상기 제2 상부층 중 적어도 하나에 탄소 및 산소 중 적어도 하나가 포함되는 태양 전지. - 제11항에 있어서,

상기 복수의 변환 부분은, 상기 제2 변환 부분 위에 형성되며 상기 제2 밴드 갭보다 큰 제3 밴드 갭을 가지는 제3 변환 부분을 더 포함하는 태양 전지. - 제18항에 있어서,

상기 제1 변환 부분의 제1 진성층은 게르마늄을 포함하는 비정질 실리콘층을 포함하고,

상기 제2 변환 부분의 제2 진성층은 게르마늄을 상기 제1 진성층보다 작게 함유하는 비정질 실리콘층을 포함하며,

상기 제3 변환 부분의 제3 진성층은 도핑되지 않은 비정질 실리콘층을 포함하는 태양 전지. - 제19항에 있어서,

상기 제1 진성층에서 상기 게르마늄의 원자 함량비가 25% 내지 50%이고,

상기 제2 진성층에서 상기 게르마늄의 원자 함량비가 10% 내지 35%인 태양 전지. - 제18항에 있어서,

상기 제1 밴드 갭이 1.2eV 내지 1.45eV이고,

상기 제2 밴드 갭이 1.4eV 내지 1.6eV이며,

상기 제3 밴드 갭이 1.6eV 내지 1.9eV인 태양 전지. - 제18항에 있어서,

상기 제1 광전 변환 부분의 제1 진성층보다 상기 제2 광전 변환 부분의 제2 진성층의 두께가 얇고, 상기 제2 진성층보다 상기 제3 광전 변환 부분의 제3 진성층의 두께가 얇은 태양 전지. - 제22항에 있어서,

상기 제1 진성층의 두께가 100nm 내지 350nm의 두께를 가지고,

상기 제2 진성층의 두께가 50nm 내지 300nm이며,

상기 제3 진성층의 두께가 50nm 내지 300nm인 태양 전지. - 제18항에 있어서,

상기 제1 변환 부분은, 상기 제1 광전 변환부 위에 차례로 형성되는 제1 하부층, 제1 진성층 및 제1 상부층을 포함하여 pin 또는 nip 접합 구조를 형성하고,

상기 제2 변환 부분은, 상기 제1 변환 부분 위에 차례로 형성되는 제2 하부층, 제2 진성층 및 제2 상부층을 포함하여 pin 또는 nip 접합 구조를 형성하며,

상기 제3 변환 부분은, 상기 제2 변환 부분 위에 차례로 형성되는 제3 하부층, 제3 진성층 및 제3 상부층을 포함하여 pin 또는 nip 접합 구조를 형성하며,

상기 제1 상부층, 상기 제2 상부층 및 상기 제3 상부층 중 적어도 하나에 탄소 및 산소 중 적어도 하나가 포함되는 태양 전지. - 제1항에 있어서,

상기 전극은, 상기 제2 광전 변환부에 연결되는 제1 전극과, 상기 제1 광전 변환부에 연결되는 제2 전극을 포함하는 태양 전지. - 제25항에 있어서,

상기 제1 전극은, 상기 제2 광전 변환부 위에 형성되는 투명 전극층과, 상기 투명 전극층 위에 형성되며 패턴을 가지는 금속 전극을 포함하는 태양 전지. - 제26항에 있어서,

상기 제1 전극의 상기 금속 전극은 서로 평행하게 형성되는 복수의 핑거 전극을 포함하는 태양 전지. - 제27항에 있어서,

상기 제1 전극의 상기 금속 전극은 상기 복수의 핑거 전극을 연결하는 버스바 전극을 더 포함하는 태양 전지. - 제25항에 있어서,

상기 제2 전극은 패턴을 가지면서 형성되고,

상기 제2 전극이 형성되지 않은 부분에는 패시베이션 막이 형성되는 태양 전지. - 제29항에 있어서,

상기 제2 전극은 서로 평행하게 형성되는 복수의 핑거 전극을 포함하는 태양 전지. - 제30항에 있어서,

상기 제2 전극은 상기 복수의 핑거 전극을 연결하는 버스바 전극을 더 포함하는 태양 전지. - 제25항에 있어서,

상기 제2 전극은 상기 제1 광전 변환부의 일면에 전체적으로 형성되는 태양 전지. - 제25항에 있어서,

상기 제1 광전 변환부의 일면에 형성되는 패시베이션 막을 더 포함하고,

상기 제1 전극은 상기 패시베이션 막을 관통하여 상기 제1 광전 변환부에 점 컨택되는 제1 부분과, 상기 제1 부분에 연결되며 상기 패시베이션 막 위에 전체적으로 형성되는 제2 부분을 포함하는 태양 전지. - 결정질 반도체를 포함하는 반도체 기판을 준비하는 단계;

상기 반도체 기판에 불순물을 도핑하여 에미터층을 형성하여 제1 광전 변환부를 형성하는 단계;

상기 에미터층 상에 접합층을 형성하는 단계;

상기 접합층 위에 비정질 반도체를 포함하는 제2 광전 변환부를 형성하는 단계; 및

상기 제2 광전 변환부에 연결되는 제1 전극과 상기 반도체 기판에 연결되는 제2 전극을 형성하는 단계

를 포함하고,

상기 제2 광전 변환부을 형성하는 단계는, 상기 접합층 위에 상기 반도체 기판보다 큰 제1 밴드 갭을 가지는 제1 변환 부분을 형성하는 단계와, 상기 제1 변환 부분 위에 상기 제1 밴드 갭보다 큰 제2 밴드 갭을 가지는 제2 변환 부분을 형성하는 단계를 포함하는 태양 전지의 제조 방법. - 제34항에 있어서,

상기 에미터층은 열 확산법 또는 이온 주입법에 의하여 형성되는 태양 전지의 제조 방법. - 제34항에 있어서,

상기 접합층, 상기 제1 변환 부분 및 상기 제2 변환 부분 중 적어도 하나는 증착에 의하여 형성되는 태양 전지의 제조 방법. - 제34항에 있어서,

상기 제1 전극 및 상기 제2 전극 중 적어도 하나는 도금, 인쇄, 증착, 스퍼터, 또는 레이저 소성 컨택에 의하여 형성되는 태양 전지의 제조 방법. - 제34항에 있어서,

상기 제1 광전 변환부의 제1 진성층의 두께보다 상기 제2 광전 변환부의 제2 진성층의 두께가 두꺼운 태양 전지의 제조 방법. - 제34항에 있어서,

상기 제2 광전 변환부을 형성하는 단계는, 상기 제2 변환 부분을 형성한 다음에 상기 제2 광전 변환 부분 위에 상기 제2 밴드 갭보다 큰 제3 밴드 갭을 가지는 제3 변환 부분을 더 형성하는 태양 전지의 제조 방법.

Priority Applications (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020120150835A KR20140082012A (ko) | 2012-12-21 | 2012-12-21 | 태양 전지 및 이의 제조 방법 |

| US14/078,702 US20140174517A1 (en) | 2012-12-21 | 2013-11-13 | Solar cell and method of manufacturing the same |

| EP13005773.0A EP2747153A3 (en) | 2012-12-21 | 2013-12-11 | Solar cell and method of manufacturing the same |

| CN201310710850.6A CN103887357A (zh) | 2012-12-21 | 2013-12-20 | 太阳能电池及其制造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020120150835A KR20140082012A (ko) | 2012-12-21 | 2012-12-21 | 태양 전지 및 이의 제조 방법 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| KR20140082012A true KR20140082012A (ko) | 2014-07-02 |

Family

ID=49765263

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020120150835A Ceased KR20140082012A (ko) | 2012-12-21 | 2012-12-21 | 태양 전지 및 이의 제조 방법 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US20140174517A1 (ko) |

| EP (1) | EP2747153A3 (ko) |

| KR (1) | KR20140082012A (ko) |

| CN (1) | CN103887357A (ko) |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20200061479A (ko) * | 2018-11-23 | 2020-06-03 | 충남대학교산학협력단 | 전하선택 박막을 포함하는 실리콘 태양전지 및 이의 제조방법 |

| KR20210151460A (ko) * | 2020-06-05 | 2021-12-14 | 한국과학기술연구원 | 탠덤 태양전지 및 그 제조방법 |

Families Citing this family (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| EP3331029B1 (en) * | 2016-12-02 | 2021-09-01 | LG Electronics Inc. | Tandem solar cell and method of manufacturing the same |

| KR102805661B1 (ko) * | 2020-03-04 | 2025-05-13 | 트리나 솔라 컴패니 리미티드 | 태양 전지 및 이의 제조 방법 |

Family Cites Families (18)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4496788A (en) * | 1982-12-29 | 1985-01-29 | Osaka Transformer Co., Ltd. | Photovoltaic device |

| US4586988A (en) * | 1983-08-19 | 1986-05-06 | Energy Conversion Devices, Inc. | Method of forming an electrically conductive member |

| US5230753A (en) * | 1991-12-03 | 1993-07-27 | Princeton University | Photostable amorphous silicon-germanium alloys |

| US6316715B1 (en) * | 2000-03-15 | 2001-11-13 | The Boeing Company | Multijunction photovoltaic cell with thin 1st (top) subcell and thick 2nd subcell of same or similar semiconductor material |

| US20080135083A1 (en) * | 2006-12-08 | 2008-06-12 | Higher Way Electronic Co., Ltd. | Cascade solar cell with amorphous silicon-based solar cell |

| KR101087351B1 (ko) * | 2006-12-25 | 2011-11-25 | 샤프 가부시키가이샤 | 광전변환 장치 및 그 제조 방법 |

| US20080173349A1 (en) * | 2007-01-22 | 2008-07-24 | United Solar Ovonic Llc | Solar cells for stratospheric and outer space use |

| KR101608953B1 (ko) * | 2007-11-09 | 2016-04-04 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 광전 변환 장치 및 그 제조 방법 |

| JP5315008B2 (ja) * | 2007-11-16 | 2013-10-16 | 株式会社半導体エネルギー研究所 | 光電変換装置 |

| JP5248995B2 (ja) * | 2007-11-30 | 2013-07-31 | 株式会社半導体エネルギー研究所 | 光電変換装置の製造方法 |

| EP2105972A3 (en) * | 2008-03-28 | 2015-06-10 | Semiconductor Energy Laboratory Co, Ltd. | Photoelectric conversion device and method for manufacturing the same |

| KR100895977B1 (ko) * | 2008-04-10 | 2009-05-07 | 키스코홀딩스주식회사 | 실리콘 박막 태양전지 및 제조방법 |

| US20090272430A1 (en) * | 2008-04-30 | 2009-11-05 | Emcore Solar Power, Inc. | Refractive Index Matching in Inverted Metamorphic Multijunction Solar Cells |

| KR100876613B1 (ko) * | 2008-05-27 | 2008-12-31 | 한국철강 주식회사 | 탄뎀 박막 실리콘 태양전지 및 그 제조방법 |

| US20140007928A1 (en) * | 2012-07-06 | 2014-01-09 | Zena Technologies, Inc. | Multi-junction photovoltaic devices |

| WO2010140522A1 (en) * | 2009-06-05 | 2010-12-09 | Semiconductor Energy Laboratory Co., Ltd. | Photoelectric conversion device and manufacturing method thereof |

| KR100990111B1 (ko) * | 2009-08-19 | 2010-10-29 | 엘지전자 주식회사 | 태양전지 |

| WO2011087878A2 (en) * | 2010-01-18 | 2011-07-21 | Applied Materials, Inc. | Manufacture of thin film solar cells with high conversion efficiency |

-

2012

- 2012-12-21 KR KR1020120150835A patent/KR20140082012A/ko not_active Ceased

-

2013

- 2013-11-13 US US14/078,702 patent/US20140174517A1/en not_active Abandoned

- 2013-12-11 EP EP13005773.0A patent/EP2747153A3/en not_active Withdrawn

- 2013-12-20 CN CN201310710850.6A patent/CN103887357A/zh active Pending

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20200061479A (ko) * | 2018-11-23 | 2020-06-03 | 충남대학교산학협력단 | 전하선택 박막을 포함하는 실리콘 태양전지 및 이의 제조방법 |

| KR20210151460A (ko) * | 2020-06-05 | 2021-12-14 | 한국과학기술연구원 | 탠덤 태양전지 및 그 제조방법 |

Also Published As

| Publication number | Publication date |

|---|---|

| EP2747153A3 (en) | 2017-12-13 |

| CN103887357A (zh) | 2014-06-25 |

| EP2747153A2 (en) | 2014-06-25 |

| US20140174517A1 (en) | 2014-06-26 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6059173B2 (ja) | 太陽電池 | |

| KR101622091B1 (ko) | 태양 전지 및 이의 제조 방법 | |

| CN101611497B (zh) | 太阳电池 | |

| KR101631450B1 (ko) | 태양 전지 | |

| US20110056544A1 (en) | Solar cell | |

| JP5424800B2 (ja) | デュアルドーピングを備えたヘテロ接合光電池及びその製造方法 | |

| US20100132774A1 (en) | Thin Film Silicon Solar Cell Device With Amorphous Window Layer | |

| TWI455338B (zh) | 超晶格結構的太陽能電池 | |

| KR20140082012A (ko) | 태양 전지 및 이의 제조 방법 | |

| KR102053139B1 (ko) | 태양 전지 | |

| KR102286289B1 (ko) | 태양 전지 | |

| KR101889774B1 (ko) | 태양 전지 | |

| US20150083203A1 (en) | Thin film solar cell | |

| KR20160111622A (ko) | 태양 전지 | |

| KR20160111623A (ko) | 태양 전지 | |

| KR101961370B1 (ko) | 태양 전지 | |

| US20250221085A1 (en) | Solar cell and photovoltaic module | |

| JP2020505786A (ja) | シングル型、タンデム型ならびにヘテロ接合型太陽電池装置およびその形成方法 | |

| US8691616B2 (en) | Method for manufacturing thin film solar cell | |

| WO2025106021A1 (en) | Carrier-selective contact layer, photovoltaic devices incorporating the layer, and manufacturing methods therefor | |

| CN119855290A (zh) | 一种太阳能电池、太阳能电池组件 | |

| KR20130129656A (ko) | 태양 전지 및 이의 제조 방법 | |

| KR20120073926A (ko) | 태양전지 및 그 제조방법 | |

| KR20100033897A (ko) | 광기전력 변환소자 및 제조방법 | |

| KR20120088023A (ko) | 태양 전지 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| PA0109 | Patent application |

Patent event code: PA01091R01D Comment text: Patent Application Patent event date: 20121221 |

|

| PG1501 | Laying open of application | ||

| A201 | Request for examination | ||

| PA0201 | Request for examination |

Patent event code: PA02012R01D Patent event date: 20171017 Comment text: Request for Examination of Application Patent event code: PA02011R01I Patent event date: 20121221 Comment text: Patent Application |

|

| E902 | Notification of reason for refusal | ||

| PE0902 | Notice of grounds for rejection |

Comment text: Notification of reason for refusal Patent event date: 20190418 Patent event code: PE09021S01D |

|

| E601 | Decision to refuse application | ||

| PE0601 | Decision on rejection of patent |

Patent event date: 20190705 Comment text: Decision to Refuse Application Patent event code: PE06012S01D Patent event date: 20190418 Comment text: Notification of reason for refusal Patent event code: PE06011S01I |