KR20200041966A - 전압 인가 장치 및 출력 전압 파형의 형성 방법 - Google Patents

전압 인가 장치 및 출력 전압 파형의 형성 방법 Download PDFInfo

- Publication number

- KR20200041966A KR20200041966A KR1020207007981A KR20207007981A KR20200041966A KR 20200041966 A KR20200041966 A KR 20200041966A KR 1020207007981 A KR1020207007981 A KR 1020207007981A KR 20207007981 A KR20207007981 A KR 20207007981A KR 20200041966 A KR20200041966 A KR 20200041966A

- Authority

- KR

- South Korea

- Prior art keywords

- voltage

- transient

- time

- output

- waveform

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- G—PHYSICS

- G01—MEASURING; TESTING

- G01R—MEASURING ELECTRIC VARIABLES; MEASURING MAGNETIC VARIABLES

- G01R31/00—Arrangements for testing electric properties; Arrangements for locating electric faults; Arrangements for electrical testing characterised by what is being tested not provided for elsewhere

- G01R31/28—Testing of electronic circuits, e.g. by signal tracer

- G01R31/317—Testing of digital circuits

- G01R31/3181—Functional testing

- G01R31/3183—Generation of test inputs, e.g. test vectors, patterns or sequences

-

- G—PHYSICS

- G01—MEASURING; TESTING

- G01R—MEASURING ELECTRIC VARIABLES; MEASURING MAGNETIC VARIABLES

- G01R31/00—Arrangements for testing electric properties; Arrangements for locating electric faults; Arrangements for electrical testing characterised by what is being tested not provided for elsewhere

- G01R31/28—Testing of electronic circuits, e.g. by signal tracer

- G01R31/30—Marginal testing, e.g. by varying supply voltage

- G01R31/3004—Current or voltage test

-

- G—PHYSICS

- G01—MEASURING; TESTING

- G01R—MEASURING ELECTRIC VARIABLES; MEASURING MAGNETIC VARIABLES

- G01R31/00—Arrangements for testing electric properties; Arrangements for locating electric faults; Arrangements for electrical testing characterised by what is being tested not provided for elsewhere

- G01R31/28—Testing of electronic circuits, e.g. by signal tracer

- G01R31/317—Testing of digital circuits

- G01R31/31721—Power aspects, e.g. power supplies for test circuits, power saving during test

-

- G—PHYSICS

- G01—MEASURING; TESTING

- G01R—MEASURING ELECTRIC VARIABLES; MEASURING MAGNETIC VARIABLES

- G01R31/00—Arrangements for testing electric properties; Arrangements for locating electric faults; Arrangements for electrical testing characterised by what is being tested not provided for elsewhere

- G01R31/28—Testing of electronic circuits, e.g. by signal tracer

- G01R31/317—Testing of digital circuits

- G01R31/3181—Functional testing

- G01R31/319—Tester hardware, i.e. output processing circuits

- G01R31/31917—Stimuli generation or application of test patterns to the device under test [DUT]

- G01R31/31924—Voltage or current aspects, e.g. driver, receiver

Landscapes

- Engineering & Computer Science (AREA)

- General Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- General Physics & Mathematics (AREA)

- Testing Or Measuring Of Semiconductors Or The Like (AREA)

- Tests Of Electronic Circuits (AREA)

- Testing Of Individual Semiconductor Devices (AREA)

- Electrical Discharge Machining, Electrochemical Machining, And Combined Machining (AREA)

- Electronic Switches (AREA)

Abstract

Description

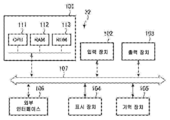

도 2는 도 1의 검사 장치에서의 제어부의 하드웨어 구성을 나타내는 단면도이다.

도 3은 본 발명의 일실시형태에 관한 디바이스 전원을 나타내는 블록도이다.

도 4는 출력 전압의 라이징 파형을 형성하는 방법을 나타내는 플로우차트이다.

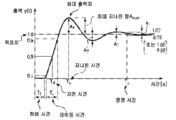

도 5는 도 4의 출력 전압의 라이징 파형을 형성하는 방법에 의해 형성된 출력 전압의 과도 전압 파형의 일례를 모식적으로 나타내는 도면이다.

도 6은 일반적인 2차 지연계의 스텝 응답 출력의 곡선을 나타내는 도면이다.

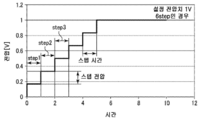

도 7은 0.5 V, 0.2 V, 0.15 V, 0.1 V, 0.05 V의 전압을 각각 출력한 경우의 2차 지연계의 스텝 응답을 나타내는 도면이다.

도 8은 1 V의 전압을 출력한 경우와, 스텝 전압을 0.5 V→0.2 V→0.15 V→0.1 V→0.05 V로 한 스텝형의 과도 전압 파형을 출력한 경우의 2차 지연계의 스텝 응답을 나타내는 도면이다.

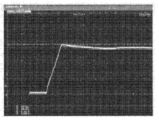

도 9는 DPS로부터 1 V의 전압을 출력하고, DUT 단부에 큰 오버슈트가 생기는 조건에 있어서, 실제로 DPS로부터 출력되는 과도 전압 파형을, 스텝 전압을 0.5 V→0.2 V→0.15 V→0.1 V→0.05 V로 변화시킨 5 스텝으로 하고, 각 스텝의 스텝 시간을, 라이징 시간 Tr의 종점으로부터 지나친 점 Tp의 사이에 대응하는 시간이 되도록 설정하여 출력한 과도 전압 파형을 나타내는 도면이다.

도 10은 도 9의 과도 전압 파형이 출력되었을 때에, 실제 DUT 단부에서의 응답 파형을 나타내는 사진이다.

Claims (8)

- 기판 상에 형성된 복수의 피검사 디바이스에 대하여 전기적 특성을 검사하는 테스터에 있어서, 상기 피검사 디바이스에 전압을 인가하는 전압 인가 장치로서,

상기 전압 인가 장치는, 설정 전압치를 포함하는 미리 정해진 설정 조건이 주어졌을 때에, 상기 미리 정해진 설정 조건에 적합한, 복수의 과도 스텝을 갖는 스텝형의 과도 전압 파형이 형성되도록, 과도 전압 설정 파라미터로서, 과도 스텝수, 스텝 시간, 스텝 전압을 설정하는 전압 설정부를 가지며,

상기 전압 설정부에서 설정된 상기 과도 전압 설정 파라미터에 기초하여, 상기 스텝형의 과도 전압 파형을 갖는 출력 전압을 출력하고,

상기 디바이스의 전원으로부터 출력된 출력 전압을, 상기 전압 인가 장치에 접속된 상기 피검사 디바이스에 스텝 입력했을 때의 응답이, 설정 전압에 대하여 오버슈트가 생기는 2차 이상의 고차 지연계이며,

상기 전압 설정부에 설정된 상기 각 과도 스텝의 상기 스텝 시간의 종점이, 상기 고차 지연계의 스텝 응답 곡선에서의 라이징 시간의 종점으로부터 지나친 시간까지의 사이의 시간이 되도록 설정되는 것인 전압 인가 장치. - 제1항에 있어서, 디지털 아날로그 컨버터와, 출력 회로를 더 가지며, 상기 전압 설정부에서 설정된 상기 과도 전압 설정 파라미터를 포함하는 신호가, 상기 디지털 아날로그 컨버터 및 상기 출력 회로를 거쳐, 상기 스텝형의 과도 전압 파형을 갖는 출력 전압으로서 출력되는 것인 전압 인가 장치.

- 제1항 또는 제2항에 있어서, 상기 과도 전압 파형은, 상기 과도 스텝의 상기 스텝 전압이, 상기 과도 스텝이 진행됨에 따라서 작아지도록 형성되는 것인 전압 인가 장치.

- 제1항 내지 제3항 중 어느 한 항에 있어서, 상기 전압 설정부는, 설정 전압치를 포함하는 복수의 설정 조건에 대응하여, 상기 과도 전압 설정 파라미터로서, 상기 과도 스텝수, 상기 스텝 시간, 상기 스텝 전압이 복수 기억된 데이터베이스로부터, 상기 미리 정해진 설정 조건에 적합한 상기 과도 스텝수, 상기 스텝 시간, 상기 스텝 전압을 취득하는 것인 전압 인가 장치.

- 제1항 내지 제4항 중 어느 한 항에 있어서, 디바이스 전원(DPS), 파라메트릭 측정 유닛(PMU) 및 각종 드라이버 중 어느 하나인 것인 전압 인가 장치.

- 기판 상에 형성된 복수의 피검사 디바이스에 대하여 전기적 특성을 검사하는 테스터에 있어서, 상기 피검사 디바이스에 전압을 인가하는 전압 인가 장치로부터 출력하는 출력 전압 파형의 형성 방법으로서,

설정 전압치를 포함하는 조건이 주어졌을 때에, 상기 조건에 적합한 복수의 과도 스텝을 갖는 스텝형의 과도 전압 파형이 형성되도록, 과도 전압 설정 파라미터로서, 과도 스텝수, 스텝 시간, 스텝 전압을 설정하는 단계와,

상기 과도 전압 설정 파라미터에 기초하여, 상기 스텝형의 과도 전압 파형을 갖는 출력 전압을 형성하는 단계

를 포함하며,

상기 전압 인가 장치로부터 출력된 출력 전압을, 상기 전압 인가 장치에 접속된 상기 피검사 디바이스에 스텝 입력했을 때의 응답이, 설정 전압에 대하여 오버슈트가 생기는 2차 이상의 고차 지연계이며,

상기 각 과도 스텝의 상기 스텝 시간의 종점이, 상기 고차 지연계의 스텝 응답 곡선에서의 라이징 시간의 종점으로부터 지나친 시간까지의 사이의 시간이 되도록 설정되는 것인 출력 전압 파형의 형성 방법. - 제6항에 있어서, 상기 과도 전압 파형은, 상기 과도 스텝의 상기 스텝 전압이, 상기 과도 스텝이 진행됨에 따라서 작아지도록 형성되는 것인 출력 전압 파형의 형성 방법.

- 제6항 또는 제7항에 있어서, 설정 전압치를 포함하는 복수의 설정 조건에 대응하여, 상기 과도 전압 설정 파라미터로서, 상기 과도 스텝수, 상기 스텝 시간, 상기 스텝 전압이 복수 기억된 데이터베이스로부터, 미리 정해진 설정 조건에 적합한 상기 과도 스텝수, 상기 스텝 시간, 상기 스텝 전압을 취득하는 것인 출력 전압 파형의 형성 방법.

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2017174700A JP6986910B2 (ja) | 2017-09-12 | 2017-09-12 | 電圧印加装置および出力電圧波形の形成方法 |

| JPJP-P-2017-174700 | 2017-09-12 | ||

| PCT/JP2018/027949 WO2019054059A1 (ja) | 2017-09-12 | 2018-07-25 | 電圧印加装置および出力電圧波形の形成方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR20200041966A true KR20200041966A (ko) | 2020-04-22 |

| KR102320086B1 KR102320086B1 (ko) | 2021-11-02 |

Family

ID=65723982

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020207007981A Active KR102320086B1 (ko) | 2017-09-12 | 2018-07-25 | 전압 인가 장치 및 출력 전압 파형의 형성 방법 |

Country Status (6)

| Country | Link |

|---|---|

| US (1) | US11293978B2 (ko) |

| JP (1) | JP6986910B2 (ko) |

| KR (1) | KR102320086B1 (ko) |

| CN (1) | CN111051904B (ko) |

| TW (1) | TWI770267B (ko) |

| WO (1) | WO2019054059A1 (ko) |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US11187745B2 (en) | 2019-10-30 | 2021-11-30 | Teradyne, Inc. | Stabilizing a voltage at a device under test |

Citations (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0317581A (ja) | 1989-06-14 | 1991-01-25 | Opt:Kk | 移動体追跡装置 |

| JP2004272447A (ja) * | 2003-03-06 | 2004-09-30 | Seiko Epson Corp | 電源回路 |

| JP2004297983A (ja) * | 2003-03-28 | 2004-10-21 | Tdk Corp | スイッチング電源の出力制御方法、出力制御回路およびスイッチング電源 |

| JP2006133109A (ja) * | 2004-11-08 | 2006-05-25 | Fujitsu Ltd | 半導体試験装置 |

| JP2008109747A (ja) * | 2006-10-24 | 2008-05-08 | Fuji Electric Device Technology Co Ltd | ソフトスタート回路 |

| JP2010044013A (ja) * | 2008-08-18 | 2010-02-25 | Fujitsu Microelectronics Ltd | 半導体装置の試験方法 |

| KR20130072950A (ko) * | 2011-12-22 | 2013-07-02 | 엘지이노텍 주식회사 | 역률 보상 회로 및 이를 포함하는 전압 공급 장치 |

| CN106712486A (zh) * | 2017-03-09 | 2017-05-24 | 中国人民解放军海军航空工程学院 | 一种高压开关电源自适应软启动系统及方法 |

Family Cites Families (24)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4308491A (en) * | 1980-05-05 | 1981-12-29 | Square D Company | Automatic fault protection system for power recovery control |

| JPH0317581U (ko) | 1989-06-30 | 1991-02-21 | ||

| JPH09178820A (ja) * | 1995-12-25 | 1997-07-11 | Advantest Corp | Dc電圧印加装置 |

| JP2001121697A (ja) * | 1999-10-28 | 2001-05-08 | Seiko Epson Corp | 駆動素子を動作させるための駆動波形の生成 |

| US6556034B1 (en) * | 2000-11-22 | 2003-04-29 | Teradyne, Inc. | High speed and high accuracy DUT power supply with active boost circuitry |

| US8225152B2 (en) * | 2002-05-09 | 2012-07-17 | Agilent Technologies, Inc. | Method and apparatus for generating electronic test and data structure |

| JP2004015342A (ja) * | 2002-06-05 | 2004-01-15 | Ntt Docomo Inc | 呼受付制御方法及びその方法が適用される通信システム |

| WO2004025499A1 (en) * | 2002-09-11 | 2004-03-25 | The Research Foundation Of State University Of New York | Jerk limited time delay filter |

| US6775160B2 (en) * | 2002-09-27 | 2004-08-10 | The Aerospace Corporation | Dynamic DC source and load energy recycling power system |

| KR100471726B1 (ko) * | 2003-07-11 | 2005-03-14 | 학교법인 성균관대학 | 전송선로에서 고조파와 상태천이도를 이용한 고장 검출 방법 |

| US7072166B2 (en) * | 2003-09-12 | 2006-07-04 | Axcelis Technologies, Inc. | Clamping and de-clamping semiconductor wafers on a J-R electrostatic chuck having a micromachined surface by using force delay in applying a single-phase square wave AC clamping voltage |

| JP4581865B2 (ja) * | 2005-06-24 | 2010-11-17 | 横河電機株式会社 | 電圧印加装置 |

| US7889019B2 (en) * | 2006-10-13 | 2011-02-15 | Andrew Roman Gizara | Pulse width modulation sequence generating a near critical damped step response |

| JP5171010B2 (ja) * | 2006-10-27 | 2013-03-27 | 東京エレクトロン株式会社 | 電源装置およびそれを用いたマイクロ波発生装置およびコンピュータプログラム |

| US7719336B2 (en) * | 2006-10-31 | 2010-05-18 | Andrew Roman Gizara | Pulse width modulation sequence maintaining maximally flat voltage during current transients |

| WO2010029597A1 (ja) * | 2008-09-10 | 2010-03-18 | 株式会社アドバンテスト | 試験装置および回路システム |

| JP5623175B2 (ja) * | 2010-07-30 | 2014-11-12 | キヤノン株式会社 | 高電圧発生装置並びに画像形成装置、高電圧発生装置の電圧制御方法 |

| CN102508140B (zh) * | 2011-10-10 | 2013-07-17 | 保定天威集团有限公司 | 一种通过数字电路实现脉冲校验的方法 |

| JP2013104859A (ja) * | 2011-11-17 | 2013-05-30 | Hioki Ee Corp | 電圧出力装置および抵抗測定装置 |

| US9709605B2 (en) * | 2012-12-12 | 2017-07-18 | Tektronix, Inc. | Scrolling measurement display ticker for test and measurement instruments |

| CN103091628B (zh) * | 2013-01-14 | 2016-04-20 | 河北省电力公司电力科学研究院 | 一种测量微型断路器上电后延迟动作时间的方法 |

| KR102123989B1 (ko) * | 2013-12-17 | 2020-06-26 | 삼성전자주식회사 | 테스터 및 이를 구비하는 반도체 소자 검사 장치 |

| CN104750152A (zh) * | 2015-03-11 | 2015-07-01 | 上海华虹宏力半导体制造有限公司 | 一种电压调整器 |

| KR102328101B1 (ko) * | 2015-07-07 | 2021-11-17 | 삼성전자주식회사 | 프로브 카드, 프로브 카드용 단열 커버 어셈블리, 및 이를 갖는 반도체 디바이스의 검사 장치 |

-

2017

- 2017-09-12 JP JP2017174700A patent/JP6986910B2/ja active Active

-

2018

- 2018-07-25 WO PCT/JP2018/027949 patent/WO2019054059A1/ja not_active Ceased

- 2018-07-25 KR KR1020207007981A patent/KR102320086B1/ko active Active

- 2018-07-25 CN CN201880057271.7A patent/CN111051904B/zh active Active

- 2018-07-25 US US16/645,609 patent/US11293978B2/en active Active

- 2018-09-07 TW TW107131423A patent/TWI770267B/zh active

Patent Citations (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0317581A (ja) | 1989-06-14 | 1991-01-25 | Opt:Kk | 移動体追跡装置 |

| JP2004272447A (ja) * | 2003-03-06 | 2004-09-30 | Seiko Epson Corp | 電源回路 |

| JP2004297983A (ja) * | 2003-03-28 | 2004-10-21 | Tdk Corp | スイッチング電源の出力制御方法、出力制御回路およびスイッチング電源 |

| JP2006133109A (ja) * | 2004-11-08 | 2006-05-25 | Fujitsu Ltd | 半導体試験装置 |

| JP2008109747A (ja) * | 2006-10-24 | 2008-05-08 | Fuji Electric Device Technology Co Ltd | ソフトスタート回路 |

| JP2010044013A (ja) * | 2008-08-18 | 2010-02-25 | Fujitsu Microelectronics Ltd | 半導体装置の試験方法 |

| KR20130072950A (ko) * | 2011-12-22 | 2013-07-02 | 엘지이노텍 주식회사 | 역률 보상 회로 및 이를 포함하는 전압 공급 장치 |

| CN106712486A (zh) * | 2017-03-09 | 2017-05-24 | 中国人民解放军海军航空工程学院 | 一种高压开关电源自适应软启动系统及方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP6986910B2 (ja) | 2021-12-22 |

| WO2019054059A1 (ja) | 2019-03-21 |

| TWI770267B (zh) | 2022-07-11 |

| CN111051904B (zh) | 2022-04-01 |

| TW201932861A (zh) | 2019-08-16 |

| US20200278392A1 (en) | 2020-09-03 |

| JP2019050331A (ja) | 2019-03-28 |

| KR102320086B1 (ko) | 2021-11-02 |

| US11293978B2 (en) | 2022-04-05 |

| CN111051904A (zh) | 2020-04-21 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN101996912B (zh) | 集成电路晶圆级测试方法、半导体装置测试系统及其方法 | |

| US7612620B2 (en) | System and method for conditioning differential clock signals and integrated circuit load board using same | |

| EP1440328B1 (en) | Method and apparatus for calibration and validation of high performance dut power supplies | |

| US11162990B2 (en) | Calibration arrangement and method for deriving a resistance of a resistor | |

| CN111025016A (zh) | 开尔文结构的电阻测试方法 | |

| KR20180137945A (ko) | 피시험 디바이스를 테스트하기 위한 프로세서 기반의 계측 방법 및 이를 이용한 계측 장치 | |

| KR20170038050A (ko) | 디바이스의 검사 방법, 프로브 카드, 인터포저 및 검사 장치 | |

| TWI396855B (zh) | 被測試元件、測試裝置及測試方法 | |

| KR101254280B1 (ko) | 시험 장치 및 제조 방법 | |

| US8471599B2 (en) | Adjustable voltage comparing circuit and adjustable voltage examining device | |

| KR102320086B1 (ko) | 전압 인가 장치 및 출력 전압 파형의 형성 방법 | |

| JP2002544489A (ja) | 伝送路損失補償を備えたドライバ | |

| KR102468913B1 (ko) | 자동 테스트 장비(ate)와 피시험디바이스(dut) 사이를 인터페이싱하는 장치 | |

| US20240219459A1 (en) | Method for measuring quiescent current in a switching voltage regulator | |

| JPWO2005064586A1 (ja) | 表示装置の駆動装置、表示装置、駆動装置または表示装置の検査方法 | |

| KR101762383B1 (ko) | 반도체 시험 장치에 있어서의 전기 길이 측정 방법 | |

| CN109872765B (zh) | 一种防止高压烧焊垫的测试方法 | |

| JP2013130428A (ja) | 半導体デバイスの検査装置 | |

| US20110001509A1 (en) | Semiconductor integrated circuit device and method for testing the same | |

| JP2013130427A (ja) | 半導体デバイスの検査装置 | |

| JP2001281303A (ja) | 半導体集積回路試験装置、半導体集積回路試験装置の校正方法及び記録媒体 | |

| KR100916763B1 (ko) | 반도체 디바이스 테스트 시스템 | |

| EP4575533A1 (en) | Auto tuning for tester dut power supply | |

| JP2010165819A (ja) | 半導体集積回路の試験装置、試験方法 | |

| JP4840730B2 (ja) | デバイステスタ、タイミング校正方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| PA0105 | International application |

St.27 status event code: A-0-1-A10-A15-nap-PA0105 |

|

| PA0201 | Request for examination |

St.27 status event code: A-1-2-D10-D11-exm-PA0201 |

|

| PG1501 | Laying open of application |

St.27 status event code: A-1-1-Q10-Q12-nap-PG1501 |

|

| D13-X000 | Search requested |

St.27 status event code: A-1-2-D10-D13-srh-X000 |

|

| D14-X000 | Search report completed |

St.27 status event code: A-1-2-D10-D14-srh-X000 |

|

| E902 | Notification of reason for refusal | ||

| PE0902 | Notice of grounds for rejection |

St.27 status event code: A-1-2-D10-D21-exm-PE0902 |

|

| E13-X000 | Pre-grant limitation requested |

St.27 status event code: A-2-3-E10-E13-lim-X000 |

|

| P11-X000 | Amendment of application requested |

St.27 status event code: A-2-2-P10-P11-nap-X000 |

|

| P13-X000 | Application amended |

St.27 status event code: A-2-2-P10-P13-nap-X000 |

|

| E701 | Decision to grant or registration of patent right | ||

| PE0701 | Decision of registration |

St.27 status event code: A-1-2-D10-D22-exm-PE0701 |

|

| GRNT | Written decision to grant | ||

| PR0701 | Registration of establishment |

St.27 status event code: A-2-4-F10-F11-exm-PR0701 |

|

| PR1002 | Payment of registration fee |

St.27 status event code: A-2-2-U10-U12-oth-PR1002 Fee payment year number: 1 |

|

| PG1601 | Publication of registration |

St.27 status event code: A-4-4-Q10-Q13-nap-PG1601 |

|

| PR1001 | Payment of annual fee |

St.27 status event code: A-4-4-U10-U11-oth-PR1001 Fee payment year number: 4 |

|

| PR1001 | Payment of annual fee |

St.27 status event code: A-4-4-U10-U11-oth-PR1001 Fee payment year number: 5 |

|

| U11 | Full renewal or maintenance fee paid |

Free format text: ST27 STATUS EVENT CODE: A-4-4-U10-U11-OTH-PR1001 (AS PROVIDED BY THE NATIONAL OFFICE) Year of fee payment: 5 |