RU2024110C1 - Интегральная микросхема - Google Patents

Интегральная микросхемаInfo

- Publication number

- RU2024110C1 RU2024110C1 SU914926788A SU4926788A RU2024110C1 RU 2024110 C1 RU2024110 C1 RU 2024110C1 SU 914926788 A SU914926788 A SU 914926788A SU 4926788 A SU4926788 A SU 4926788A RU 2024110 C1 RU2024110 C1 RU 2024110C1

- Authority

- RU

- Russia

- Prior art keywords

- crystal

- contact pads

- chip

- holder

- integrated circuit

- Prior art date

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W70/00—Package substrates; Interposers; Redistribution layers [RDL]

- H10W70/60—Insulating or insulated package substrates; Interposers; Redistribution layers

- H10W70/62—Insulating or insulated package substrates; Interposers; Redistribution layers characterised by their interconnections

- H10W70/65—Shapes or dispositions of interconnections

- H10W70/654—Top-view layouts

- H10W70/656—Fan-in layouts

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/851—Dispositions of multiple connectors or interconnections

- H10W72/874—On different surfaces

- H10W72/884—Die-attach connectors and bond wires

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W74/00—Encapsulations, e.g. protective coatings

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W90/00—Package configurations

- H10W90/701—Package configurations characterised by the relative positions of pads or connectors relative to package parts

- H10W90/731—Package configurations characterised by the relative positions of pads or connectors relative to package parts of die-attach connectors

- H10W90/734—Package configurations characterised by the relative positions of pads or connectors relative to package parts of die-attach connectors between a chip and a stacked insulating package substrate, interposer or RDL

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W90/00—Package configurations

- H10W90/701—Package configurations characterised by the relative positions of pads or connectors relative to package parts

- H10W90/751—Package configurations characterised by the relative positions of pads or connectors relative to package parts of bond wires

- H10W90/754—Package configurations characterised by the relative positions of pads or connectors relative to package parts of bond wires between a chip and a stacked insulating package substrate, interposer or RDL

Landscapes

- Semiconductor Integrated Circuits (AREA)

Abstract

Изобретение относится к радиоэлектронике. Сущность изобретения: в интегральной микросхеме, содержащей защитную оболочку из диэлектрического материала, кристалл с интегральной схемой, расположенной на кристаллодержателе с внутренними контактными площадками и внешними выводами входа-выхода, расположенными на противоположных плоскостях кристаллодержателя и соединенными посредством проводниковой разводки, размещенной на одной плоскости с внутренними контактными площадками, соединенными с контактными площадками кристалла проволочными перемычками, проводниковая разводка частично расположена в области, расположенной под кристаллом, и в этой области изолирована от кристалла диэлектрическим слоем. 1 з.п.ф-лы, 5 ил.

Description

Изобретение относится к радиоэлектронике и может быть использовано при создании и производстве миниатюризованных интегральных микросхем (ИМС) и радиоэлектронной аппаратуры на их основе, преимущественно электронных модулей (э.м.), изготавливаемых способом поверхностного монтажа.

Известна ИМС, в которой полупроводниковый кристалл устанавливают на металлическую выводную рамку, контактные площадки кристалла соединяют проволочными перемычками с внутренними траверсами выводной рамки, а защиту от внешних воздействий выполняют полимерным материалом путем трансферного прессования [1].

К недостаткам такой конструкции относятся ограничения по количеству выводов, сложность изготовления многовыводных рамок и ограниченная мощность рассеивания, недостаточные миниатюризация и быстродействие ИМС.

Известна ИМС, содержащая корпус из пластмассы, размещенный в корпусе кристаллодержатель из теплопроводного материала, на одной из сторон которого размещены полупроводниковый кристалл и контактные площадки, а на другой - контактные площадки с присоединенными к ним внешними выводами входа-выхода. Контактные площадки противоположных сторон кристаллодержателя соединены между собой. Контактные площадки, расположенные на внутренней стороне кристаллодержателя, соединены с контактными площадками кристалла проволочными перемычками [2].

Известная конструкция имеет уменьшенные габариты, простую выводную рамку и повышенную мощность рассеивания.

Однако в данной конструкции не в полной мере использована возможность миниатюризации и повышения быстродействия ИМС.

Целью изобретения является уменьшение габаритов ИМС и повышение ее быстродействия.

Для этого в ИМС, содержащей защитную диэлектрическую оболочку, кристалл, расположенный на кристаллодержателе с внутренними контактными площадками и внешними контактными площадками - выводами, расположенными соответственно на внутренней, обращенной к кристаллу, и внешней, наружной, поверхностях кристаллодержателя и соединенными между собой через межслойные переходы проводниковой разводкой, расположенной на внутренней плоскости кристаллодержателя, причем внутренние контактные площадки кристаллодержателя соединены с контактными площадками кристалла, согласно изобретению проводниковая разводка, расположенная на внутренней поверхности кристаллодержателя, частично размещена в области, находящейся под кристаллом и перекрываемой этим кристаллом, и изолирована от него диэлектрическим слоем.

Уменьшение габаритов может быть достигнуто также и за счет того, что защитная оболочка из диэлектрического материала расположена только со стороны полупроводникового кристалла.

Сопоставительный с прототипом анализ показывает, что предлагаемая конструкция содержит новые отличительные признаки. В ней проводниковая разводка, соединяющая внутренние контактные площади кристаллодержателя с внешними контактными площадками входа-выхода, частично размещена в зоне, находящейся под кристаллом, и закрыта дополнительным диэлектрическим слоем. Это позволяет разместить на поверхности кристаллодержателя полупроводниковый кристалл и внутренние контактные площадки в непосредственной близости от краев кристалла, а соединительную разводку осуществлять под нижней поверхностью кристалла. Благодаря отмеченным признакам появляется возможность существенного уменьшения площади кристаллодержателя и ИМС в целом, что позволяет повысить быстродействие ИМС.

Технических решений, содержащих признаки, сходные с признаками, отличающими заявленное решение от прототипа, не обнаружено, на основании чего следует сделать вывод о соответствии заявленного устройства критерию "существенные отличия".

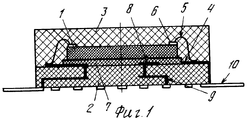

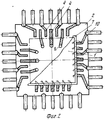

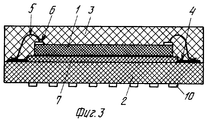

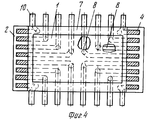

На фиг.1 представлена ИМС в разрезе; на фиг.2 - та же, ИМС вид сверху с разрезом кристалла и указанием зоны его размещения; на фиг.3 - ИМС, у которой выводы кристалла размещены по узким сторонам, а внешние выводы входа-выхода - по ее широким сторонам, разрез; на фиг.4 - та же ИМС, вид сверху без защитной оболочки; на фиг.5 - та же ИМС, вид снизу.

ИМС содержит полупроводниковый кристалл 1, установленный на кристаллодержатель 2, защитную оболочку 3, внутренние контактные площадки 4, соединенные проволочными перемычками 5 с контактными площадками 6 кристалла, под которым размещен диэлектрический слой 7, ниже которого проходит проводниковая разводка 8, соединенная через межслойные переходы 9 с внешними контактными площадками-выводами 10.

Кристаллодержатель 2 выполняют в виде тонкой многослойной керамической пластины, на верхней поверхности которой за пределами кристалла создают металлизированные площадки для приварки проволочных перемычек 5, соединяющих контактные площадки кристалла 6 с внешними выводами входа-выхода 10, а в пределах площади кристалла размещают дополнительный диэлектрический слой 7, на который устанавливают кристалл 1, причем, если необходима установка кристалла с помощью эвтектической пайки, диэлектрический слой 7 покрывают металлизацией, если достаточна установка кристалла на клей, то указанную металлизацию не делают.

Уменьшение габаритов в предложенном решении достигается за счет более эффективного использования площади верхней поверхности кристаллодержателя, благодаря размещению проводниковой разводки под нижней поверхностью кристалла. При этом в зависимости от конкретного кристалла, используемого в схеме, разводка может быть только под кристаллом или под кристаллом и вне его. В обоих случаях достигается положительный эффект - уменьшение габаритов ИМС и повышение ее быстродействия. Так, микросхема серии 565РУ7, выполненная в металлокерамическом корпусе и имеющая габариты 21х7,5х3 мм, при реализации с использованием предложенного решения может иметь размеры 10х5х2 мм.

ИМС может быть выполнена как с внешними металлическими выводами, так и без них. Ее покрывают защитной оболочкой только со стороны кристалла, что также позволяет уменьшить габариты ИМС.

Claims (2)

1. ИНТЕГРАЛЬНАЯ МИКРОСХЕМА, содержащая защитную оболочку из диэлектрического материала, полупроводниковый кристалл, расположенный на кристаллодержателе, снабженном внутренними контактными площадками и внешними контактными площадками - выводами входа-выхода, размещенными соответственно на внутренней, обращенной к кристаллу, и внешней, обращенной наружу, поверхностях кристаллодержателя, и соединенными между собой через межслойные переходы и проводниковую разводку, расположенную на одной плоскости с внутренними контактными площадками кристаллодержателя, которые соединены с контактными площадками кристалла проволочными перемычками, отличающаяся тем, что, с целью уменьшения габаритов и повышения быстродействия, проводниковая разводка частично размещена в области, расположенной под кристаллом, и в этой области изолирована от кристалла диэлектрическим слоем.

2. Микросхема по п.1, отличающаяся тем, что, с целью уменьшения габаритов, защитная оболочка из диэлектрического материала расположена только со стороны полупроводникового кристалла.

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| SU914926788A RU2024110C1 (ru) | 1991-04-10 | 1991-04-10 | Интегральная микросхема |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| SU914926788A RU2024110C1 (ru) | 1991-04-10 | 1991-04-10 | Интегральная микросхема |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| RU2024110C1 true RU2024110C1 (ru) | 1994-11-30 |

Family

ID=21569358

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| SU914926788A RU2024110C1 (ru) | 1991-04-10 | 1991-04-10 | Интегральная микросхема |

Country Status (1)

| Country | Link |

|---|---|

| RU (1) | RU2024110C1 (ru) |

Cited By (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| RU2164720C2 (ru) * | 1995-04-25 | 2001-03-27 | Сименс Акциенгезелльшафт | Покрытие кристалла интегральной схемы |

| RU2165660C2 (ru) * | 1996-09-23 | 2001-04-20 | Сименс Акциенгезелльшафт | Модуль микросхемы и способ изготовления модуля микросхемы |

| RU2172539C2 (ru) * | 1996-02-09 | 2001-08-20 | Сименс Акциенгезелльшафт | Разъединяемый соединительный мостик (разрушаемая перемычка) и соединяемый разрыв проводника (восстанавливаемая перемычка), а также способ изготовления и активирования разрушаемой перемычки и восстанавливаемой перемычки |

| RU2189071C2 (ru) * | 1996-08-23 | 2002-09-10 | Сименс Акциенгезелльшафт | Полупроводниковая схема, в частности, для применения в интегральном модуле |

| RU2193231C2 (ru) * | 1996-09-30 | 2002-11-20 | Сименс Акциенгезелльшафт | Модуль микросхемы для имплантации в корпус карточки с встроенным микропроцессором (варианты) |

| RU2202126C2 (ru) * | 1996-12-20 | 2003-04-10 | Сименс Акциенгезелльшафт | Непроводящая подложка, образующая ленту или единицу использования, на которой выполнено множество несущих элементов |

-

1991

- 1991-04-10 RU SU914926788A patent/RU2024110C1/ru active

Non-Patent Citations (2)

| Title |

|---|

| 1. Технология СБИС. Под ред. С. Зи.-М. Мир, 1986, т. 2, с.358-362. * |

| 2. Авторское свидетельство СССР N 1583995, кл. H 01L 23/28, 1988. * |

Cited By (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| RU2164720C2 (ru) * | 1995-04-25 | 2001-03-27 | Сименс Акциенгезелльшафт | Покрытие кристалла интегральной схемы |

| RU2172539C2 (ru) * | 1996-02-09 | 2001-08-20 | Сименс Акциенгезелльшафт | Разъединяемый соединительный мостик (разрушаемая перемычка) и соединяемый разрыв проводника (восстанавливаемая перемычка), а также способ изготовления и активирования разрушаемой перемычки и восстанавливаемой перемычки |

| RU2189071C2 (ru) * | 1996-08-23 | 2002-09-10 | Сименс Акциенгезелльшафт | Полупроводниковая схема, в частности, для применения в интегральном модуле |

| RU2165660C2 (ru) * | 1996-09-23 | 2001-04-20 | Сименс Акциенгезелльшафт | Модуль микросхемы и способ изготовления модуля микросхемы |

| RU2193231C2 (ru) * | 1996-09-30 | 2002-11-20 | Сименс Акциенгезелльшафт | Модуль микросхемы для имплантации в корпус карточки с встроенным микропроцессором (варианты) |

| RU2202126C2 (ru) * | 1996-12-20 | 2003-04-10 | Сименс Акциенгезелльшафт | Непроводящая подложка, образующая ленту или единицу использования, на которой выполнено множество несущих элементов |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US4941033A (en) | Semiconductor integrated circuit device | |

| CA2202426C (en) | Mounting structure for a semiconductor circuit | |

| US4975761A (en) | High performance plastic encapsulated package for integrated circuit die | |

| US5858815A (en) | Semiconductor package and method for fabricating the same | |

| US5705851A (en) | Thermal ball lead integrated package | |

| CA2171458C (en) | Multi-chip module | |

| US4907067A (en) | Thermally efficient power device package | |

| US4410905A (en) | Power, ground and decoupling structure for chip carriers | |

| US5598031A (en) | Electrically and thermally enhanced package using a separate silicon substrate | |

| US7236373B2 (en) | Electronic device capable of preventing electromagnetic wave from being radiated | |

| US5942795A (en) | Leaded substrate carrier for integrated circuit device and leaded substrate carrier device assembly | |

| EP0729183A2 (en) | Thin packaging of multi-chip modules with enhanced thermal/power management | |

| US20050280998A1 (en) | Half-bridge power module with insert molded heatsinks | |

| US5914535A (en) | Flip chip-on-flip chip multi-chip module | |

| JP3304957B2 (ja) | 多重チップ半導体モジュールとその製造方法 | |

| KR970067817A (ko) | 반도체 패키지 및 그 제조방법 | |

| US6115255A (en) | Hybrid high-power integrated circuit | |

| US5475565A (en) | Power distribution lid for IC package | |

| KR0158783B1 (ko) | 접속 핀을 통해 기판과 캡에 접속된 전자 부품을 탑재하는 멀티 칩 세라믹 모듈 | |

| US5977624A (en) | Semiconductor package and assembly for fabricating the same | |

| US5519576A (en) | Thermally enhanced leadframe | |

| RU2024110C1 (ru) | Интегральная микросхема | |

| US6387507B1 (en) | High temperature co-fired ceramic and low temperature co-fired ceramic combination electronic package device and method | |

| US5324890A (en) | Direct bond copper-output footprint | |

| JP2005166892A (ja) | スタック型小型メモリカード |