JP2006019727A - 勾配付き組み込みシリコン−ゲルマニウムのソース−ドレイン及び/又は延長部をもつ、歪みp型mosfetの構造及びこれを製造する方法 - Google Patents

勾配付き組み込みシリコン−ゲルマニウムのソース−ドレイン及び/又は延長部をもつ、歪みp型mosfetの構造及びこれを製造する方法 Download PDFInfo

- Publication number

- JP2006019727A JP2006019727A JP2005183624A JP2005183624A JP2006019727A JP 2006019727 A JP2006019727 A JP 2006019727A JP 2005183624 A JP2005183624 A JP 2005183624A JP 2005183624 A JP2005183624 A JP 2005183624A JP 2006019727 A JP2006019727 A JP 2006019727A

- Authority

- JP

- Japan

- Prior art keywords

- layer

- soi

- dopant

- germanium

- sige

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P32/00—Diffusion of dopants within, into or out of wafers, substrates or parts of devices

- H10P32/10—Diffusion of dopants within, into or out of semiconductor bodies or layers

- H10P32/14—Diffusion of dopants within, into or out of semiconductor bodies or layers within a single semiconductor body or layer in a solid phase; between different semiconductor bodies or layers, both in a solid phase

- H10P32/1408—Diffusion of dopants within, into or out of semiconductor bodies or layers within a single semiconductor body or layer in a solid phase; between different semiconductor bodies or layers, both in a solid phase from or through or into an external applied layer, e.g. photoresist or nitride layers

- H10P32/141—Diffusion of dopants within, into or out of semiconductor bodies or layers within a single semiconductor body or layer in a solid phase; between different semiconductor bodies or layers, both in a solid phase from or through or into an external applied layer, e.g. photoresist or nitride layers the applied layer comprising oxides only

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/01—Manufacture or treatment

- H10D30/021—Manufacture or treatment of FETs having insulated gates [IGFET]

- H10D30/022—Manufacture or treatment of FETs having insulated gates [IGFET] having lightly-doped source or drain extensions selectively formed at the sides of the gates

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/01—Manufacture or treatment

- H10D30/021—Manufacture or treatment of FETs having insulated gates [IGFET]

- H10D30/027—Manufacture or treatment of FETs having insulated gates [IGFET] of lateral single-gate IGFETs

- H10D30/0275—Manufacture or treatment of FETs having insulated gates [IGFET] of lateral single-gate IGFETs forming single crystalline semiconductor source or drain regions resulting in recessed gates, e.g. forming raised source or drain regions

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/01—Manufacture or treatment

- H10D30/021—Manufacture or treatment of FETs having insulated gates [IGFET]

- H10D30/031—Manufacture or treatment of FETs having insulated gates [IGFET] of thin-film transistors [TFT]

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/67—Thin-film transistors [TFT]

- H10D30/6704—Thin-film transistors [TFT] having supplementary regions or layers in the thin films or in the insulated bulk substrates for controlling properties of the device

- H10D30/6713—Thin-film transistors [TFT] having supplementary regions or layers in the thin films or in the insulated bulk substrates for controlling properties of the device characterised by the properties of the source or drain regions, e.g. compositions or sectional shapes

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/67—Thin-film transistors [TFT]

- H10D30/674—Thin-film transistors [TFT] characterised by the active materials

- H10D30/6741—Group IV materials, e.g. germanium or silicon carbide

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/791—Arrangements for exerting mechanical stress on the crystal lattice of the channel regions

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/791—Arrangements for exerting mechanical stress on the crystal lattice of the channel regions

- H10D30/797—Arrangements for exerting mechanical stress on the crystal lattice of the channel regions being in source or drain regions, e.g. SiGe source or drain

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P32/00—Diffusion of dopants within, into or out of wafers, substrates or parts of devices

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P32/00—Diffusion of dopants within, into or out of wafers, substrates or parts of devices

- H10P32/10—Diffusion of dopants within, into or out of semiconductor bodies or layers

- H10P32/17—Diffusion of dopants within, into or out of semiconductor bodies or layers characterised by the semiconductor material

- H10P32/171—Diffusion of dopants within, into or out of semiconductor bodies or layers characterised by the semiconductor material being group IV material

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D62/00—Semiconductor bodies, or regions thereof, of devices having potential barriers

- H10D62/10—Shapes, relative sizes or dispositions of the regions of the semiconductor bodies; Shapes of the semiconductor bodies

- H10D62/17—Semiconductor regions connected to electrodes not carrying current to be rectified, amplified or switched, e.g. channel regions

- H10D62/213—Channel regions of field-effect devices

- H10D62/221—Channel regions of field-effect devices of FETs

- H10D62/235—Channel regions of field-effect devices of FETs of IGFETs

- H10D62/299—Channel regions of field-effect devices of FETs of IGFETs having lateral doping variations

- H10D62/307—Channel regions of field-effect devices of FETs of IGFETs having lateral doping variations the doping variations being parallel to the channel lengths

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P90/00—Preparation of wafers not covered by a single main group of this subclass, e.g. wafer reinforcement

- H10P90/19—Preparing inhomogeneous wafers

- H10P90/1904—Preparing vertically inhomogeneous wafers

- H10P90/1906—Preparing SOI wafers

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W10/00—Isolation regions in semiconductor bodies between components of integrated devices

- H10W10/10—Isolation regions comprising dielectric materials

- H10W10/181—Semiconductor-on-insulator [SOI] isolation regions, e.g. buried oxide regions of SOI wafers

Landscapes

- Thin Film Transistor (AREA)

- Insulated Gate Type Field-Effect Transistor (AREA)

Abstract

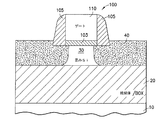

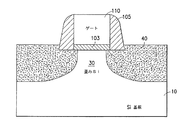

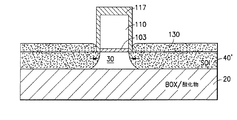

【解決手段】P型MOSFETは、ゲート110を絶縁体で封止し、ゲルマニウム含有層を側壁105の外側に成層させ、次いで、アニーリング又は酸化により、ゲルマニウムを絶縁体上シリコン層又はバルクシリコンの中に拡散させて、勾配付き組み込みシリコン−ゲルマニウムのソース−ドレイン40及び/又は延長部(geSiGe−SDE)を形成する。SOIデバイスにおいては、geSiGe−SDEは、水平方向の(ゲート誘電面に対して平行な)圧縮応力と、垂直方向の(該ゲート誘電面に対して直角の)引張り応力とをPMOSFETのチャネルに生成し、これによって、PMOSFET性能を向上させる構造を形成する。

【選択図】図1

Description

1)歪みシリコンは緩和SiGe上で成長されるものであり、したがって、デバイスの漏れを制御するのが困難である。

2)性能を向上させるために、ゲルマニウム濃度を30%以上にするという要求は、さらに、欠陥の密度を増加させる。

3)SiGeにおけるヒ素及びリンのようなドーパントの高い拡散率は、浅いp−n接合を形成するのを困難にする。サブミクロン又はディープ・サブミクロンのMOSFETにおいては、デバイスをスケーリングするのに浅い接合が要求される。

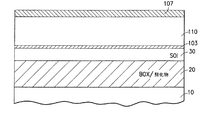

本発明の別の特徴は、ゲルマニウムによる垂直方向の完全な又は部分的な浸透によって、SOI層の中にSiGe領域を形成することである。

シリコンSOIウェハーで開始し、

ゲート酸化物(又はこれと等価のもの)を成長させ、

ポリゲート層を成層し(又は金属ゲートデバイスの金属を成層し)、

窒化物マスク層を成層し、

フォトレジスト、RIE窒化物、ポリ−Si(金属ゲートのためのRIE金属)及び酸化物を成層してパターン加工し、

薄い窒化物スペーサ(〜10ないし30nm)を形成し、

露出したシリコン上に、選択的にエピタキシャルSiGe(又はゲルマニウム)を形成し、

高温でアニールし、ゲルマニウムをSiデバイス層の中に拡散し、ゲルマニウム濃度を垂直方向及び水平方向に勾配付けするが、好ましくは、ゲルマニウムの濃度勾配形状がチャネル領域に入らないようにし、

ハロ注入、延長部注入、スペーサ形成、S/D注入、RTA、メタライゼーションを含んで、トランジスタを完成させる。

20:埋め込み絶縁体

30:SOI

40:ソース及びドレイン

100:電界効果トランジスタ

103:ゲート酸化物

105:側壁

107:ハードマスク

108:フォトレジスト

110:ゲート

130:エピタキシャル材料

Claims (25)

- PMOSFETを形成する方法であって、

埋め込み絶縁体層と前記埋め込み絶縁体層の上のSOI層とを有するSOIウェハーを準備し、

ゲート絶縁体層を前記SOI層の上方に形成し、

下側にチャネルを有するトランジスタゲートを前記SOI層の上に形成し、

絶縁体側壁を前記ゲートの第1の側面及び第2の側面に形成し、

ドーパントを含有するドーピング層を、前記SOI層上で前記絶縁体側壁に隣接してエピタキシャル形成し、

前記ドーパントを前記ドーピング層から前記SOI層の中に拡散させ、これによって、SOI表面に対して平行な水平方向の圧縮応力と、前記SOI表面に対して直角の垂直方向の引張り応力とを前記チャネルに生成し、

前記PMOSFETを完成させる、

ステップを含む方法。 - 前記拡散ステップが、高温アニールにより行われる請求項1に記載の方法。

- 前記ドーパントが前記SOI層の底面に到達するまで前記拡散ステップが継続される請求項1に記載の方法。

- 前記ドーパントが前記SOI層の底面に到達する前に前記拡散ステップが停止される請求項1に記載の方法。

- 前記ドーピング層がSiGeである請求項1に記載の方法。

- 前記ドーパント層が、原子番号20%より大きいゲルマニウム濃度をもつSiGeである請求項3に記載の方法。

- 熱酸化物の層を前記ドーピング層上に成長させ、これによって、該ドーピング層内の前記ドーパントを前記SOI層の中に拡散させるステップをさらに含む請求項1に記載の方法。

- 前記ドーパントを拡散させる前記ステップの後に、前記熱酸化物を除去するステップをさらに含む請求項7に記載の方法。

- 前記ドーパントが前記SOI層の底面に到達するまで前記拡散ステップが継続される請求項7に記載の方法。

- 前記ドーパントが前記SOI層の底面に到達する前に前記拡散ステップが停止される請求項7に記載の方法。

- 前記ドーピング層がSiGeである請求項7に記載の方法。

- 前記ドーピング層が、20%より大きいゲルマニウム濃度をもつSiGeである請求項11に記載の方法。

- PMOSFETを形成する方法であって、

バルクシリコンウェハーを準備し、

ゲート絶縁体層を前記バルクシリコンの上方に形成し、

下側にチャネルを有するトランジスタゲートを前記バルクシリコンの上に形成し、

絶縁体側壁を前記ゲートの第1の側面及び第2の側面に形成し、

ゲルマニウム又は不純物を含有するドーピング層を、前記バルクシリコン上で前記絶縁体側壁に隣接してエピタキシャル形成し、

ゲルマニウムを前記ゲルマニウムがドーピングされた層から前記バルクシリコンの中に拡散させ、これによって、(SOI表面に対して平行な)水平方向の圧縮応力と、(SOI表面に対して直角の)垂直方向の引張り応力とを前記チャネルに生成し、

前記PMOSFETを完成させる、

ステップを含む方法。 - 前記拡散ステップが、高温アニールにより行われる請求項13に記載の方法。

- 前記ドーピング層がSiGeである請求項13に記載の方法。

- 前記ドーパント層が、20%より大きいゲルマニウム濃度をもつSiGeである請求項13に記載の方法。

- 熱酸化物の層を前記ドーパント層上に成長させ、これによって、前記ドーパントを前記バルクシリコンの中に拡散させるステップをさらに含む請求項13に記載の方法。

- 前記ドーパントを拡散させる前記ステップの後に、前記熱酸化物を除去するステップをさらに含む請求項17に記載の方法。

- 前記ドーパント層がSiGeである請求項17に記載の方法。

- 前記ドーパント層が、20%より大きいゲルマニウム濃度をもつSiGeである請求項19に記載の方法。

- 埋め込み絶縁体層と前記埋め込み絶縁体層の上のSOI層とを有するSOIウェハーに形成された少なくとも1つのPMOSFETを含む集積回路であって、

前記少なくとも1つのPMOSFETが、前記SOI層の上方のゲート絶縁体と、該SOI層の上にあって下側にチャネルを有するトランジスタゲートとを有し、前記チャネルは、該チャネルにおいてSOI表面に対して平行な水平方向の圧縮応力と、前記SOI表面に対して直角の垂直方向の引張り応力とを有し、

前記SOI層が、前記水平方向の前記圧縮応力を生成するドーパントの濃度勾配を有し、前記ドーパントの前記濃度が、該SOI層の上面において最大値を有することを特徴とする集積回路。 - 前記ドーパントの濃度勾配が、前記SOI層の厚さより少ないドーパント深さまで延びる請求項21に記載の集積回路。

- 前記SOI層がシリコンであり、前記ドーパントがゲルマニウムである請求項22に記載の集積回路。

- 前記濃度勾配が高温アニールにより形成された請求項22に記載の集積回路。

- 前記濃度勾配が、前記SOI層の上に配設された成層ドーパント層を熱酸化することにより形成された請求項22に記載の集積回路。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US10/710244 | 2004-06-29 | ||

| US10/710,244 US7288443B2 (en) | 2004-06-29 | 2004-06-29 | Structures and methods for manufacturing p-type MOSFET with graded embedded silicon-germanium source-drain and/or extension |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2006019727A true JP2006019727A (ja) | 2006-01-19 |

| JP2006019727A5 JP2006019727A5 (ja) | 2008-06-19 |

| JP5043314B2 JP5043314B2 (ja) | 2012-10-10 |

Family

ID=35504716

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2005183624A Expired - Fee Related JP5043314B2 (ja) | 2004-06-29 | 2005-06-23 | 勾配付き組み込みシリコン−ゲルマニウムのソース−ドレイン及び/又は延長部をもつ、歪みp型mosfetを製造する方法 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US7288443B2 (ja) |

| JP (1) | JP5043314B2 (ja) |

| CN (1) | CN100444336C (ja) |

| TW (1) | TW200625460A (ja) |

Cited By (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2008515188A (ja) * | 2004-09-29 | 2008-05-08 | フリースケール セミコンダクター インコーポレイテッド | 歪みチャネル、及びヘテロ接合ソース/ドレインを有する半導体素子を形成する方法 |

| JP2011044706A (ja) * | 2009-07-28 | 2011-03-03 | Taiwan Semiconductor Manufacturing Co Ltd | 高ゲルマニウム濃度のSiGeストレッサの形成方法 |

| WO2011030782A1 (ja) * | 2009-09-09 | 2011-03-17 | 学校法人神奈川大学 | 半導体素子構造の形成方法、及び半導体素子 |

| CN114514392A (zh) * | 2019-05-03 | 2022-05-17 | 泰普科英普罗有限责任公司 | 用于浮动阀座板的系统和方法 |

Families Citing this family (35)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20060151808A1 (en) * | 2005-01-12 | 2006-07-13 | Chien-Hao Chen | MOSFET device with localized stressor |

| DE102005013982A1 (de) * | 2005-03-26 | 2006-10-05 | Atmel Germany Gmbh | Verfahren zur Herstellung eines Bipolartransistors und nach einem derartigen Verfahren hergestellter Bipolartransistor |

| US7439165B2 (en) * | 2005-04-06 | 2008-10-21 | Agency For Sceince, Technology And Reasearch | Method of fabricating tensile strained layers and compressive strain layers for a CMOS device |

| US7446350B2 (en) * | 2005-05-10 | 2008-11-04 | International Business Machine Corporation | Embedded silicon germanium using a double buried oxide silicon-on-insulator wafer |

| KR100675895B1 (ko) * | 2005-06-29 | 2007-02-02 | 주식회사 하이닉스반도체 | 반도체소자의 금속배선구조 및 그 제조방법 |

| EP1833094B1 (en) * | 2006-03-06 | 2011-02-02 | STMicroelectronics (Crolles 2) SAS | Formation of shallow SiGe conduction channel |

| CN100466255C (zh) * | 2006-04-18 | 2009-03-04 | 联华电子股份有限公司 | 半导体结构及其制作方法 |

| US8211761B2 (en) * | 2006-08-16 | 2012-07-03 | Globalfoundries Singapore Pte. Ltd. | Semiconductor system using germanium condensation |

| KR100773359B1 (ko) * | 2006-11-20 | 2007-11-05 | 삼성전자주식회사 | 높은 이동도를 갖는 트랜지스터들의 제조방법 및 그에 의해제조된 트랜지스터들 |

| US7696000B2 (en) | 2006-12-01 | 2010-04-13 | International Business Machines Corporation | Low defect Si:C layer with retrograde carbon profile |

| CN101295641B (zh) * | 2007-04-24 | 2010-09-29 | 中芯国际集成电路制造(上海)有限公司 | 栅极制造方法 |

| KR100844933B1 (ko) * | 2007-06-26 | 2008-07-09 | 주식회사 하이닉스반도체 | 반도체 소자의 트랜지스터 및 그 제조 방법 |

| US7709331B2 (en) * | 2007-09-07 | 2010-05-04 | Freescale Semiconductor, Inc. | Dual gate oxide device integration |

| US7704844B2 (en) * | 2007-10-04 | 2010-04-27 | International Business Machines Corporation | High performance MOSFET |

| US7964910B2 (en) | 2007-10-17 | 2011-06-21 | International Business Machines Corporation | Planar field effect transistor structure having an angled crystallographic etch-defined source/drain recess and a method of forming the transistor structure |

| CN101458337B (zh) * | 2007-12-12 | 2010-12-08 | 中国科学院微电子研究所 | 基于绝缘体上硅的双探头pmos辐射剂量计 |

| CN101937091B (zh) * | 2007-12-12 | 2012-07-25 | 中国科学院微电子研究所 | 一种可调整量程的堆叠测量电路 |

| US20090242989A1 (en) * | 2008-03-25 | 2009-10-01 | Chan Kevin K | Complementary metal-oxide-semiconductor device with embedded stressor |

| US7955909B2 (en) * | 2008-03-28 | 2011-06-07 | International Business Machines Corporation | Strained ultra-thin SOI transistor formed by replacement gate |

| FR2936095B1 (fr) * | 2008-09-18 | 2011-04-01 | Commissariat Energie Atomique | Procede de fabrication d'un dispositif microelectronique dote de zones semi-conductrices sur isolant a gradient horizontal de concentration en ge. |

| TWI416727B (zh) * | 2009-12-04 | 2013-11-21 | 華亞科技股份有限公司 | P型金屬氧化層半導體場效電晶體及其製造方法 |

| CN102130054B (zh) * | 2010-01-20 | 2013-05-01 | 中芯国际集成电路制造(上海)有限公司 | 改善半导体器件的截止漏电流发散的方法 |

| CN102339852B (zh) * | 2010-07-27 | 2013-03-27 | 中国科学院微电子研究所 | 半导体器件及其制造方法 |

| CN102569383A (zh) * | 2010-12-14 | 2012-07-11 | 中国科学院微电子研究所 | 一种mos管及其制造方法 |

| US20120161105A1 (en) * | 2010-12-22 | 2012-06-28 | Willy Rachmady | Uniaxially strained quantum well device and method of making same |

| DE102010064290B3 (de) * | 2010-12-28 | 2012-04-19 | GLOBALFOUNDRIES Dresden Module One Ltd. Liability Company & Co. KG | Verformungserhöhung in Transistoren mit einem eingebetteten verformungsinduzierenden Halbleitermaterial durch Kondensation der legierungsbildenden Substanz |

| CN102800594B (zh) * | 2011-05-26 | 2015-01-28 | 中芯国际集成电路制造(上海)有限公司 | Pmos管的制作方法 |

| CN102931082B (zh) * | 2011-08-10 | 2015-04-22 | 中芯国际集成电路制造(北京)有限公司 | 半导体器件及其制造方法 |

| US8735303B2 (en) * | 2011-11-02 | 2014-05-27 | Globalfoundries Inc. | Methods of forming PEET devices with different structures and performance characteristics |

| US8957476B2 (en) * | 2012-12-20 | 2015-02-17 | Intel Corporation | Conversion of thin transistor elements from silicon to silicon germanium |

| US9876110B2 (en) | 2014-01-31 | 2018-01-23 | Stmicroelectronics, Inc. | High dose implantation for ultrathin semiconductor-on-insulator substrates |

| CN105679645A (zh) * | 2014-11-17 | 2016-06-15 | 上海华力微电子有限公司 | 嵌入式锗硅外延位错缺陷的改善方法 |

| US10043893B1 (en) | 2017-08-03 | 2018-08-07 | Globalfoundries Inc. | Post gate silicon germanium channel condensation and method for producing the same |

| CN112635325A (zh) * | 2020-12-07 | 2021-04-09 | 广东省大湾区集成电路与系统应用研究院 | 一种绝缘体上应变硅/锗晶体管及其制备方法 |

| CN113410309A (zh) * | 2021-06-23 | 2021-09-17 | 电子科技大学 | 一种低比导通电阻的分立栅mosfet器件及其制造方法 |

Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0982975A (ja) * | 1995-09-14 | 1997-03-28 | Toshiba Corp | 半導体装置およびその製造方法 |

| JPH1012883A (ja) * | 1996-06-20 | 1998-01-16 | Toshiba Corp | 半導体装置 |

| JPH1197673A (ja) * | 1997-09-17 | 1999-04-09 | Toshiba Corp | 半導体装置 |

| JP2003318198A (ja) * | 2002-04-25 | 2003-11-07 | Sanyo Electric Co Ltd | 半導体装置の製造方法 |

| WO2004081982A2 (en) * | 2003-03-07 | 2004-09-23 | Amberwave Systems Corporation | Shallow trench isolation process |

Family Cites Families (92)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US3602841A (en) * | 1970-06-18 | 1971-08-31 | Ibm | High frequency bulk semiconductor amplifiers and oscillators |

| US4853076A (en) * | 1983-12-29 | 1989-08-01 | Massachusetts Institute Of Technology | Semiconductor thin films |

| US4665415A (en) * | 1985-04-24 | 1987-05-12 | International Business Machines Corporation | Semiconductor device with hole conduction via strained lattice |

| EP0219641B1 (de) * | 1985-09-13 | 1991-01-09 | Siemens Aktiengesellschaft | Integrierte Bipolar- und komplementäre MOS-Transistoren auf einem gemeinsamen Substrat enthaltende Schaltung und Verfahren zu ihrer Herstellung |

| JPS6476755A (en) | 1987-09-18 | 1989-03-22 | Hitachi Ltd | Semiconductor device |

| US4958213A (en) * | 1987-12-07 | 1990-09-18 | Texas Instruments Incorporated | Method for forming a transistor base region under thick oxide |

| US5354695A (en) * | 1992-04-08 | 1994-10-11 | Leedy Glenn J | Membrane dielectric isolation IC fabrication |

| US5459346A (en) * | 1988-06-28 | 1995-10-17 | Ricoh Co., Ltd. | Semiconductor substrate with electrical contact in groove |

| US5006913A (en) * | 1988-11-05 | 1991-04-09 | Mitsubishi Denki Kabushiki Kaisha | Stacked type semiconductor device |

| US5108843A (en) * | 1988-11-30 | 1992-04-28 | Ricoh Company, Ltd. | Thin film semiconductor and process for producing the same |

| US4952524A (en) * | 1989-05-05 | 1990-08-28 | At&T Bell Laboratories | Semiconductor device manufacture including trench formation |

| US5310446A (en) * | 1990-01-10 | 1994-05-10 | Ricoh Company, Ltd. | Method for producing semiconductor film |

| US5060030A (en) * | 1990-07-18 | 1991-10-22 | Raytheon Company | Pseudomorphic HEMT having strained compensation layer |

| US5081513A (en) * | 1991-02-28 | 1992-01-14 | Xerox Corporation | Electronic device with recovery layer proximate to active layer |

| US5371399A (en) * | 1991-06-14 | 1994-12-06 | International Business Machines Corporation | Compound semiconductor having metallic inclusions and devices fabricated therefrom |

| US5134085A (en) * | 1991-11-21 | 1992-07-28 | Micron Technology, Inc. | Reduced-mask, split-polysilicon CMOS process, incorporating stacked-capacitor cells, for fabricating multi-megabit dynamic random access memories |

| US5391510A (en) * | 1992-02-28 | 1995-02-21 | International Business Machines Corporation | Formation of self-aligned metal gate FETs using a benignant removable gate material during high temperature steps |

| US6008126A (en) | 1992-04-08 | 1999-12-28 | Elm Technology Corporation | Membrane dielectric isolation IC fabrication |

| US5561302A (en) * | 1994-09-26 | 1996-10-01 | Motorola, Inc. | Enhanced mobility MOSFET device and method |

| US5679965A (en) * | 1995-03-29 | 1997-10-21 | North Carolina State University | Integrated heterostructures of Group III-V nitride semiconductor materials including epitaxial ohmic contact, non-nitride buffer layer and methods of fabricating same |

| US5670798A (en) * | 1995-03-29 | 1997-09-23 | North Carolina State University | Integrated heterostructures of Group III-V nitride semiconductor materials including epitaxial ohmic contact non-nitride buffer layer and methods of fabricating same |

| US5557122A (en) * | 1995-05-12 | 1996-09-17 | Alliance Semiconductors Corporation | Semiconductor electrode having improved grain structure and oxide growth properties |

| KR100213196B1 (ko) * | 1996-03-15 | 1999-08-02 | 윤종용 | 트렌치 소자분리 |

| US6403975B1 (en) * | 1996-04-09 | 2002-06-11 | Max-Planck Gesellschaft Zur Forderung Der Wissenschafteneev | Semiconductor components, in particular photodetectors, light emitting diodes, optical modulators and waveguides with multilayer structures grown on silicon substrates |

| US5880040A (en) * | 1996-04-15 | 1999-03-09 | Macronix International Co., Ltd. | Gate dielectric based on oxynitride grown in N2 O and annealed in NO |

| WO1998010523A1 (en) * | 1996-09-06 | 1998-03-12 | Philips Electronics N.V. | A zero-if receiver |

| US5861651A (en) * | 1997-02-28 | 1999-01-19 | Lucent Technologies Inc. | Field effect devices and capacitors with improved thin film dielectrics and method for making same |

| US5940736A (en) * | 1997-03-11 | 1999-08-17 | Lucent Technologies Inc. | Method for forming a high quality ultrathin gate oxide layer |

| US6309975B1 (en) * | 1997-03-14 | 2001-10-30 | Micron Technology, Inc. | Methods of making implanted structures |

| US6025280A (en) * | 1997-04-28 | 2000-02-15 | Lucent Technologies Inc. | Use of SiD4 for deposition of ultra thin and controllable oxides |

| US5960297A (en) * | 1997-07-02 | 1999-09-28 | Kabushiki Kaisha Toshiba | Shallow trench isolation structure and method of forming the same |

| JP3139426B2 (ja) * | 1997-10-15 | 2001-02-26 | 日本電気株式会社 | 半導体装置 |

| US6066545A (en) * | 1997-12-09 | 2000-05-23 | Texas Instruments Incorporated | Birdsbeak encroachment using combination of wet and dry etch for isolation nitride |

| US6274421B1 (en) * | 1998-01-09 | 2001-08-14 | Sharp Laboratories Of America, Inc. | Method of making metal gate sub-micron MOS transistor |

| KR100275908B1 (ko) * | 1998-03-02 | 2000-12-15 | 윤종용 | 집적 회로에 트렌치 아이솔레이션을 형성하는방법 |

| US6165383A (en) | 1998-04-10 | 2000-12-26 | Organic Display Technology | Useful precursors for organic electroluminescent materials and devices made from such materials |

| US6361885B1 (en) * | 1998-04-10 | 2002-03-26 | Organic Display Technology | Organic electroluminescent materials and device made from such materials |

| US5989978A (en) * | 1998-07-16 | 1999-11-23 | Chartered Semiconductor Manufacturing, Ltd. | Shallow trench isolation of MOSFETS with reduced corner parasitic currents |

| JP4592837B2 (ja) * | 1998-07-31 | 2010-12-08 | ルネサスエレクトロニクス株式会社 | 半導体装置の製造方法 |

| US6319794B1 (en) * | 1998-10-14 | 2001-11-20 | International Business Machines Corporation | Structure and method for producing low leakage isolation devices |

| US6235598B1 (en) * | 1998-11-13 | 2001-05-22 | Intel Corporation | Method of using thick first spacers to improve salicide resistance on polysilicon gates |

| US6117722A (en) * | 1999-02-18 | 2000-09-12 | Taiwan Semiconductor Manufacturing Company | SRAM layout for relaxing mechanical stress in shallow trench isolation technology and method of manufacture thereof |

| US6255169B1 (en) * | 1999-02-22 | 2001-07-03 | Advanced Micro Devices, Inc. | Process for fabricating a high-endurance non-volatile memory device |

| US6284626B1 (en) * | 1999-04-06 | 2001-09-04 | Vantis Corporation | Angled nitrogen ion implantation for minimizing mechanical stress on side walls of an isolation trench |

| US6228694B1 (en) * | 1999-06-28 | 2001-05-08 | Intel Corporation | Method of increasing the mobility of MOS transistors by use of localized stress regions |

| US6281532B1 (en) * | 1999-06-28 | 2001-08-28 | Intel Corporation | Technique to obtain increased channel mobilities in NMOS transistors by gate electrode engineering |

| US6362082B1 (en) * | 1999-06-28 | 2002-03-26 | Intel Corporation | Methodology for control of short channel effects in MOS transistors |

| US6656822B2 (en) * | 1999-06-28 | 2003-12-02 | Intel Corporation | Method for reduced capacitance interconnect system using gaseous implants into the ILD |

| KR100332108B1 (ko) * | 1999-06-29 | 2002-04-10 | 박종섭 | 반도체 소자의 트랜지스터 및 그 제조 방법 |

| TW426940B (en) * | 1999-07-30 | 2001-03-21 | United Microelectronics Corp | Manufacturing method of MOS field effect transistor |

| US6483171B1 (en) * | 1999-08-13 | 2002-11-19 | Micron Technology, Inc. | Vertical sub-micron CMOS transistors on (110), (111), (311), (511), and higher order surfaces of bulk, SOI and thin film structures and method of forming same |

| US6284623B1 (en) * | 1999-10-25 | 2001-09-04 | Peng-Fei Zhang | Method of fabricating semiconductor devices using shallow trench isolation with reduced narrow channel effect |

| US6476462B2 (en) * | 1999-12-28 | 2002-11-05 | Texas Instruments Incorporated | MOS-type semiconductor device and method for making same |

| US6221735B1 (en) * | 2000-02-15 | 2001-04-24 | Philips Semiconductors, Inc. | Method for eliminating stress induced dislocations in CMOS devices |

| US6531369B1 (en) * | 2000-03-01 | 2003-03-11 | Applied Micro Circuits Corporation | Heterojunction bipolar transistor (HBT) fabrication using a selectively deposited silicon germanium (SiGe) |

| US6368931B1 (en) * | 2000-03-27 | 2002-04-09 | Intel Corporation | Thin tensile layers in shallow trench isolation and method of making same |

| US6493497B1 (en) | 2000-09-26 | 2002-12-10 | Motorola, Inc. | Electro-optic structure and process for fabricating same |

| US6501121B1 (en) | 2000-11-15 | 2002-12-31 | Motorola, Inc. | Semiconductor structure |

| US7312485B2 (en) * | 2000-11-29 | 2007-12-25 | Intel Corporation | CMOS fabrication process utilizing special transistor orientation |

| US6563152B2 (en) * | 2000-12-29 | 2003-05-13 | Intel Corporation | Technique to obtain high mobility channels in MOS transistors by forming a strain layer on an underside of a channel |

| US20020086497A1 (en) * | 2000-12-30 | 2002-07-04 | Kwok Siang Ping | Beaker shape trench with nitride pull-back for STI |

| US6265317B1 (en) * | 2001-01-09 | 2001-07-24 | Taiwan Semiconductor Manufacturing Company | Top corner rounding for shallow trench isolation |

| US6403486B1 (en) * | 2001-04-30 | 2002-06-11 | Taiwan Semiconductor Manufacturing Company | Method for forming a shallow trench isolation |

| US6531740B2 (en) * | 2001-07-17 | 2003-03-11 | Motorola, Inc. | Integrated impedance matching and stability network |

| US6498358B1 (en) | 2001-07-20 | 2002-12-24 | Motorola, Inc. | Structure and method for fabricating an electro-optic system having an electrochromic diffraction grating |

| US6908810B2 (en) * | 2001-08-08 | 2005-06-21 | Taiwan Semiconductor Manufacturing Co., Ltd. | Method of preventing threshold voltage of MOS transistor from being decreased by shallow trench isolation formation |

| JP2003060076A (ja) * | 2001-08-21 | 2003-02-28 | Nec Corp | 半導体装置及びその製造方法 |

| WO2003025984A2 (en) | 2001-09-21 | 2003-03-27 | Amberwave Systems Corporation | Semiconductor structures employing strained material layers with defined impurity gradients and methods for fabricating same |

| US20030057184A1 (en) * | 2001-09-22 | 2003-03-27 | Shiuh-Sheng Yu | Method for pull back SiN to increase rounding effect in a shallow trench isolation process |

| US6656798B2 (en) * | 2001-09-28 | 2003-12-02 | Infineon Technologies, Ag | Gate processing method with reduced gate oxide corner and edge thinning |

| US6621131B2 (en) * | 2001-11-01 | 2003-09-16 | Intel Corporation | Semiconductor transistor having a stressed channel |

| US6635506B2 (en) * | 2001-11-07 | 2003-10-21 | International Business Machines Corporation | Method of fabricating micro-electromechanical switches on CMOS compatible substrates |

| US6461936B1 (en) * | 2002-01-04 | 2002-10-08 | Infineon Technologies Ag | Double pullback method of filling an isolation trench |

| JP4173672B2 (ja) * | 2002-03-19 | 2008-10-29 | 株式会社ルネサステクノロジ | 半導体装置及びその製造方法 |

| US6621392B1 (en) * | 2002-04-25 | 2003-09-16 | International Business Machines Corporation | Micro electromechanical switch having self-aligned spacers |

| US7388259B2 (en) * | 2002-11-25 | 2008-06-17 | International Business Machines Corporation | Strained finFET CMOS device structures |

| US6974981B2 (en) * | 2002-12-12 | 2005-12-13 | International Business Machines Corporation | Isolation structures for imposing stress patterns |

| US6717216B1 (en) * | 2002-12-12 | 2004-04-06 | International Business Machines Corporation | SOI based field effect transistor having a compressive film in undercut area under the channel and a method of making the device |

| US6825529B2 (en) * | 2002-12-12 | 2004-11-30 | International Business Machines Corporation | Stress inducing spacers |

| US6900502B2 (en) * | 2003-04-03 | 2005-05-31 | Taiwan Semiconductor Manufacturing Company, Ltd. | Strained channel on insulator device |

| US6887798B2 (en) | 2003-05-30 | 2005-05-03 | International Business Machines Corporation | STI stress modification by nitrogen plasma treatment for improving performance in small width devices |

| US7279746B2 (en) | 2003-06-30 | 2007-10-09 | International Business Machines Corporation | High performance CMOS device structures and method of manufacture |

| US7119403B2 (en) * | 2003-10-16 | 2006-10-10 | International Business Machines Corporation | High performance strained CMOS devices |

| US8008724B2 (en) * | 2003-10-30 | 2011-08-30 | International Business Machines Corporation | Structure and method to enhance both nFET and pFET performance using different kinds of stressed layers |

| US6977194B2 (en) | 2003-10-30 | 2005-12-20 | International Business Machines Corporation | Structure and method to improve channel mobility by gate electrode stress modification |

| US7015082B2 (en) * | 2003-11-06 | 2006-03-21 | International Business Machines Corporation | High mobility CMOS circuits |

| US7122849B2 (en) * | 2003-11-14 | 2006-10-17 | International Business Machines Corporation | Stressed semiconductor device structures having granular semiconductor material |

| US7247912B2 (en) * | 2004-01-05 | 2007-07-24 | International Business Machines Corporation | Structures and methods for making strained MOSFETs |

| CA2454995C (en) * | 2004-01-07 | 2011-12-20 | Martinrea International Inc. | Method and apparatus for assembling and testing a fluid conduit |

| US7205206B2 (en) * | 2004-03-03 | 2007-04-17 | International Business Machines Corporation | Method of fabricating mobility enhanced CMOS devices |

| US7504693B2 (en) * | 2004-04-23 | 2009-03-17 | International Business Machines Corporation | Dislocation free stressed channels in bulk silicon and SOI CMOS devices by gate stress engineering |

| US7354806B2 (en) * | 2004-09-17 | 2008-04-08 | International Business Machines Corporation | Semiconductor device structure with active regions having different surface directions and methods |

-

2004

- 2004-06-29 US US10/710,244 patent/US7288443B2/en not_active Expired - Fee Related

-

2005

- 2005-06-21 CN CNB2005100789757A patent/CN100444336C/zh not_active Expired - Fee Related

- 2005-06-23 JP JP2005183624A patent/JP5043314B2/ja not_active Expired - Fee Related

- 2005-06-24 TW TW094121087A patent/TW200625460A/zh unknown

Patent Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0982975A (ja) * | 1995-09-14 | 1997-03-28 | Toshiba Corp | 半導体装置およびその製造方法 |

| JPH1012883A (ja) * | 1996-06-20 | 1998-01-16 | Toshiba Corp | 半導体装置 |

| JPH1197673A (ja) * | 1997-09-17 | 1999-04-09 | Toshiba Corp | 半導体装置 |

| JP2003318198A (ja) * | 2002-04-25 | 2003-11-07 | Sanyo Electric Co Ltd | 半導体装置の製造方法 |

| WO2004081982A2 (en) * | 2003-03-07 | 2004-09-23 | Amberwave Systems Corporation | Shallow trench isolation process |

Cited By (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2008515188A (ja) * | 2004-09-29 | 2008-05-08 | フリースケール セミコンダクター インコーポレイテッド | 歪みチャネル、及びヘテロ接合ソース/ドレインを有する半導体素子を形成する方法 |

| JP2011044706A (ja) * | 2009-07-28 | 2011-03-03 | Taiwan Semiconductor Manufacturing Co Ltd | 高ゲルマニウム濃度のSiGeストレッサの形成方法 |

| JP2014045208A (ja) * | 2009-07-28 | 2014-03-13 | Taiwan Semiconductor Manufactuaring Co Ltd | 集積回路のトランジスタ構造 |

| US9660082B2 (en) | 2009-07-28 | 2017-05-23 | Taiwan Semiconductor Manufacturing Company, Ltd. | Integrated circuit transistor structure with high germanium concentration SiGe stressor |

| JP2017147458A (ja) * | 2009-07-28 | 2017-08-24 | 台湾積體電路製造股▲ふん▼有限公司Taiwan Semiconductor Manufacturing Company,Ltd. | 集積回路のトランジスタ構造 |

| US10693003B2 (en) | 2009-07-28 | 2020-06-23 | Taiwan Semiconductor Manufacturing Company, Ltd. | Integrated circuit transistor structure with high germanium concentration SiGe stressor |

| WO2011030782A1 (ja) * | 2009-09-09 | 2011-03-17 | 学校法人神奈川大学 | 半導体素子構造の形成方法、及び半導体素子 |

| US8941092B2 (en) | 2009-09-09 | 2015-01-27 | Kanagawa University | Method for forming semiconductor device structure and semiconductor device |

| JP5700563B2 (ja) * | 2009-09-09 | 2015-04-15 | 学校法人神奈川大学 | 半導体素子構造の形成方法、及び半導体素子 |

| CN114514392A (zh) * | 2019-05-03 | 2022-05-17 | 泰普科英普罗有限责任公司 | 用于浮动阀座板的系统和方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP5043314B2 (ja) | 2012-10-10 |

| CN100444336C (zh) | 2008-12-17 |

| CN1716554A (zh) | 2006-01-04 |

| US20050285192A1 (en) | 2005-12-29 |

| US7288443B2 (en) | 2007-10-30 |

| TW200625460A (en) | 2006-07-16 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5043314B2 (ja) | 勾配付き組み込みシリコン−ゲルマニウムのソース−ドレイン及び/又は延長部をもつ、歪みp型mosfetを製造する方法 | |

| CN101523608B (zh) | 包括双应力源的n沟道mosfet及其制造方法 | |

| US8912567B2 (en) | Strained channel transistor and method of fabrication thereof | |

| CN100524666C (zh) | 制造晶体管结构的方法 | |

| CN100524778C (zh) | 利用双掩埋氧化物绝缘体上硅晶片的嵌入硅锗及其形成方法 | |

| KR101811796B1 (ko) | 급경사 접합 프로파일을 갖는 소스/드레인 영역들을 구비하는 반도체 소자 및 그 제조방법 | |

| CN102931222B (zh) | 半导体器件及其制造方法 | |

| CN101322228B (zh) | 通过倾斜式预非晶化而减少受应变的晶体管中的晶体缺陷的技术 | |

| US20060151837A1 (en) | In situ doped embedded sige extension and source/drain for enhanced pfet performance | |

| JP4847152B2 (ja) | 半導体装置とその製造方法 | |

| JPWO2008120335A1 (ja) | 半導体装置およびその製造方法 | |

| JP5614184B2 (ja) | 半導体装置の製造方法 | |

| US6696729B2 (en) | Semiconductor device having diffusion regions with different junction depths | |

| US20110306170A1 (en) | Novel Method to Improve Performance by Enhancing Poly Gate Doping Concentration in an Embedded SiGe PMOS Process | |

| CN102194748B (zh) | 半导体器件及其制造方法 | |

| US6323073B1 (en) | Method for forming doped regions on an SOI device | |

| US7381624B2 (en) | Technique for forming a substrate having crystalline semiconductor regions of different characteristics located above a crystalline bulk substrate | |

| US7964921B2 (en) | MOSFET and production method of semiconductor device | |

| US7951662B2 (en) | Method of fabricating strained silicon transistor | |

| CN109087859A (zh) | 一种半导体器件的制造方法 | |

| CN107437533B (zh) | 半导体结构及其制造方法 | |

| US7479422B2 (en) | Semiconductor device with stressors and method therefor | |

| JP2009016423A (ja) | 半導体装置及びその製造方法 | |

| JP2005209980A (ja) | 半導体装置の製造方法および半導体装置 | |

| KR100760912B1 (ko) | 반도체 소자 및 그 제조 방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080423 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20080423 |

|

| RD03 | Notification of appointment of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7423 Effective date: 20090206 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20120126 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120207 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120420 |

|

| RD12 | Notification of acceptance of power of sub attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7432 Effective date: 20120420 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A821 Effective date: 20120420 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20120626 |

|

| RD14 | Notification of resignation of power of sub attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7434 Effective date: 20120626 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20120712 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20150720 Year of fee payment: 3 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |