JP2007102902A - 半導体記憶装置、及びその検査方法 - Google Patents

半導体記憶装置、及びその検査方法 Download PDFInfo

- Publication number

- JP2007102902A JP2007102902A JP2005290283A JP2005290283A JP2007102902A JP 2007102902 A JP2007102902 A JP 2007102902A JP 2005290283 A JP2005290283 A JP 2005290283A JP 2005290283 A JP2005290283 A JP 2005290283A JP 2007102902 A JP2007102902 A JP 2007102902A

- Authority

- JP

- Japan

- Prior art keywords

- bit line

- precharge

- memory device

- semiconductor memory

- circuit

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Landscapes

- Tests Of Electronic Circuits (AREA)

- Static Random-Access Memory (AREA)

- For Increasing The Reliability Of Semiconductor Memories (AREA)

Abstract

【課題】 SRAMの検査において、SNM値不足による信頼性不良を初期検査でスクリーングすることを可能とする。

【解決手段】 SRAMのビット線対の各ビット線のそれぞれに、通常動作用プリチャージ回路と検査用プリチャージ回路の各一端が並列接続される。通常動作用プリチャージ回路と検査用プリチャージ回路とは、同一の電源電圧に接続される。ビット線対の各ビット線のそれぞれに接続された通常動作用プリチャージ回路は同一の第1の活性化信号で、ビット線対の一方のビット線に接続された検査用プリチャージ回路は第2の活性化信号で、ビット線対の他方のビット線に接続された検査用プリチャージ回路は第3の活性化信号でそれぞれ活性化される。検査時において、読出し動作前に第2または第3の活性化信号の活性化によって、ビット線対の一方のビット線と他方のビット線とを互いに異なるプリチャージ電位までプリチャージする。

【選択図】 図1(a)

【解決手段】 SRAMのビット線対の各ビット線のそれぞれに、通常動作用プリチャージ回路と検査用プリチャージ回路の各一端が並列接続される。通常動作用プリチャージ回路と検査用プリチャージ回路とは、同一の電源電圧に接続される。ビット線対の各ビット線のそれぞれに接続された通常動作用プリチャージ回路は同一の第1の活性化信号で、ビット線対の一方のビット線に接続された検査用プリチャージ回路は第2の活性化信号で、ビット線対の他方のビット線に接続された検査用プリチャージ回路は第3の活性化信号でそれぞれ活性化される。検査時において、読出し動作前に第2または第3の活性化信号の活性化によって、ビット線対の一方のビット線と他方のビット線とを互いに異なるプリチャージ電位までプリチャージする。

【選択図】 図1(a)

Description

本発明は、半導体記憶装置、及びその検査方法に関し、特にスタティックランダムアクセスメモリの回路方式、及びその信頼性不良をスクリーニングする方法に関するものである。

近年、半導体集積回路装置の高機能化に伴い、スタティックランダムアクセスメモリ(以下SRAMと称す)が、その高速性と、制御とシステム組み込みの簡易性から半導体集積回路装置上に多く搭載されている。

ところが、SRAMのメモリセルを構成するトランジスタが、製造工程で発生する微細な異物により汚染されると、その異物を含んだ半導体素子は所望の動作をせず、したがって所定の特性を得られずに不良となる。このような特性不良を発生した半導体素子を市場に出さないために、通常、出荷時に検査を行って不良素子をスクリーニングする。

しかし、上記した異物による特性不良には、製造直後の初期状態で不良と判定されるものもあるが、不純物による汚染等が原因の場合には、実使用条件下で徐々に特性が悪化していき、市場不良に至るものがある。特に、市場に出た後に発生する不良は、半導体素子が既に種々の装置に組み込まれているため、不具合の影響によるユーザーへの不利益が大きく、このような市場不良をなくすことは必須である。

そこで、従来、市場不良率を低減する種々のスクリーニング技術が提案されている。

以下、SRAMメモリセルの読み出し能力不足が発生した場合の、従来のスクリーニング方法について、図2、図3、図4(a)、図4(b)を参照しながら説明する(例えば、特許文献1参照)。

以下、SRAMメモリセルの読み出し能力不足が発生した場合の、従来のスクリーニング方法について、図2、図3、図4(a)、図4(b)を参照しながら説明する(例えば、特許文献1参照)。

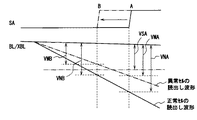

図2は一般的なSRAMの簡略化した回路構成の例を示し、図3はその主要信号の動作波形の一例を示す。また、図4(a)は、SRAMメモリセルからデータを読み出す際の、ワード線選択信号WLと、センスアンプ起動信号SA、及びビット線対の電位波形BL、XBLの例を示し、図4(b)は、センスアンプ起動時の、ビット線対の電位波形BL、XBLの波形拡大図を示す。図4(b)において、図中のAが、通常動作時の動作タイミングを示し、Bが、スクリーニング検査時の動作タイミングを示す。

これらの図において、103はメモリセル、104はセンスアンプ、PRCはプリチャージ活性化信号、WLはワード線活性化信号、SAはセンスアンプ活性化信号(以下SA信号ともいう。)、BLは正論理側ビット線、XBLは負論理側ビット線、SNは正論理側メモリセル内部ノード、XSNは負論理側メモリセル内部ノード、Q11〜Q17はトランジスタである。

SA信号が、Aのタイミングで活性化されたとき、読出し電流能力が十分な正常セルの場合には、図4(b)の実線で示すように、この正常セルからの読出し電位差VNAは、センスアンプ104の検知レベルVSAより大きく、メモリセルからのデータを、センスアンプ104で検出することができる。

一方、SA信号がAのタイミングで活性化されたとき、工程中の異物等により読出し電流能力が少なくなった異常セルの場合には、この異常セルからの読出し電位VMAがセンスアンプ104の検知レベルより小さい時(図示せず)には、読み出しが行えずに異常セルは不良として検出されるが、図4(b)の一点鎖線で示すように、VNA>VMA>VSAである時には、この時点では正常読出しが行われてしまい、異常セルであることが初期検査で検出できない。

このような異常セルは、使用頻度が重なるにつれその特性が劣化し、時間の経過とともに信頼性不良に至ることが多く、特に市場不良となった場合には大きな問題となる。

そこで、このような異常セルは、極力、初期検査時にスクリーニングすることが望ましい。これに対応するため、上記特許文献1に示される手法では、スクリーニング検査時に、センスアンプ104の起動タイミングをAからBに早めるようにしている。

このように、センスアンプ104の起動タイミングを早めることにより、図4(b)からわかるように、異常セルからの読出し電位VMBは、センスアンプ検知レベルVSAより小さくなり、初期検査時に異常セルの検出が可能となる。

特開平2−206087号公報

ところで、半導体集積回路装置の動作電圧の低電圧化により、SRAMの記憶ノードの安定性(以下、スタティックノイズマージン:SNMと略す)の確保が困難になり、読み出し動作時に、SRAMのデータを破壊してしまう“読みつぶし”を起こしやすくなる、という問題がある。この現象についての詳細は、IEEE JOURNAL OF SOLID−STATE CIRCUITS. VOL. SC−22,No.5, OCTOBER 1987 “Static−Noise Margin Analysis of MOS SRAM Cells”や電子情報通信学会論文誌C−II Vol.J75−C−II No.7 pp.350−361 1992年 7月“微細CMOSメモリセルのスタティックノイズマージン解析”などに示されている。

このように、半導体素子の微細化に伴う電源電圧の低下により、十分なSNM値を確保することが困難になってきており、更に製造工程で発生する異物等によりSRAMセルを構成するトランジスタの能力劣化が生じて、セル内のトランジスタ能力が設計値よりずれた場合には、SNM値は劣化し不良に至る。

前述したように、このような製造工程で生じた異物による不具合は、この異常セルの使用頻度が重なるにつれその特性を劣化させるため、時間の経過とともに信頼性不良に至ることが多く、市場不良発生を未然に防ぐためにも、初期検査でスクリーニングすることが望ましい。

ここで、前述した従来の手法では、センスアンプの動作タイミングを早めることによりスクリーニングを行っているが、最近の半導体素子の低電圧化、及び高速化に伴い、センスアンプの動作タイミングは、ほとんどマージンの無い設計となっており、実質的に動作タイミングを早めることは、ほぼ不可能である。したがって、今後は、この手法によってSNM不足による信頼性不良を初期検査でスクリーニングすることは、事実上不可能な状態となっているものである。

本発明は上記従来の課題に鑑みてなされたもので、SNM値不足による信頼性不良を、初期検査でスクリーニングすることのできる半導体記憶装置、及びその検査方法を提供することを目的としている。

上記課題を解決するために、本発明の第1の半導体記憶装置は、SRAMを搭載した半導体記憶装置であって、前記SRAMのビット線対の各ビット線のそれぞれに通常動作用プリチャージ回路と検査用プリチャージ回路の各一端が並列接続されており、前記通常動作用プリチャージ回路と検査用プリチャージ回路とは同一の電源電圧に接続されており、前記ビット線対の各ビット線のそれぞれに接続された第1および第2の通常動作用プリチャージ回路は同一の第1の活性化信号で活性化され、前記ビット線対の一方のビット線に接続された第1の検査用プリチャージ回路は第2の活性化信号で活性化され、前記ビット線対の他方のビット線に接続された第2の検査用プリチャージ回路は第3の活性化信号で活性化され、前記第1乃至第3の各活性化信号は互いに独立に制御され、該半導体記憶装置の検査時において読出し動作前に、前記ビット線対の他方のビット線が第1のプリチャージ電位にある状態で、前記第2の活性化信号を活性化することにより、前記ビット線対の一方のビット線を第2のプリチャージ電位にして、または前記ビット線対の一方のビット線が前記1のプリチャージ電位にある状態で、前記第3の活性化信号を活性化することにより、前記ビット線対の他方のビット線を第2のプリチャージ電位にして、前記ビット線対の一方のビット線と前記ビット線対の他方のビット線とを互いに異なるプリチャージ電位までプリチャージするプリチャージ手段を、備えている。

また、本発明の第1の半導体記憶装置において、前記ビット線対の各ビット線の電位を設定するセンスアンプは、該半導体記憶装置の検査時において読出し動作前に、メモリセルに保持されているデータに応じて、前記ビット線対の一方のビット線をHまたはLレベルの所定の論理電位に設定し、その他方のビット線を、該一方のビット線に設定される論理電位とは相補型の論理電位に設定し、前記プリチャージ手段は、前記センスアンプにより前記ビット線対の他方のビット線が前記第1のプリチャージ電位と等しいHレベル論理電位に設定されているとき、前記第2の活性化信号を活性化して、Lレベル論理電位に設定されている一方のビット線を、前記Hレベル論理電位より低い第2のプリチャージ電位に充電し、前記センスアンプにより前記一方のビット線が前記第1のプリチャージ電位と等しいHレベル論理電位に設定されているとき、前記第3の活性化信号を活性化して、Lレベル論理電位に設定されている他方のビット線を、前記Hレベル論理電位より低い第2のプリチャージ電位に充電することが好ましい。

また、本発明の第1の半導体記憶装置において、前記通常動作用プリチャージ回路および検査用プリチャージ回路は共にPチャネル型トランジスタからなり、前記プリチャージ手段は、前記検査用プリチャージ回路のPチャネル型トランジスタが、前記通常動作用プリチャージ回路のPチャネル型トランジスタより駆動能力が小さいトランジスタで構成されていることが好ましい。

また、本発明の第1の半導体記憶装置において、前記通常動作用プリチャージ回路はPチャネル型トランジスタからなり、前記検査用プリチャージ回路はNチャネル型トランジスタからなり、前記ビット線対の一方のビット線と前記ビット線対の他方のビット線とを互いに異なるプリチャージ電位までプリチャージする手段は、前記通常動作用プリチャージ回路が接続されたビット線には第1のプリチャージ電位が印加され、前記検査用プリチャージ回路が接続されたビット線には前記第1のプリチャージ電位よりも前記Nチャネル型トランジスタの閾値電圧分低い第2のプリチャージ電位が印加されることが好ましい。

また、本発明の第2の半導体記憶装置は、SRAMを搭載した半導体記憶装置であって、前記SRAMのビット線対の各ビット線のそれぞれに通常動作用プリチャージ回路と検査用プリチャージ回路の各一端が並列接続されており、前記通常動作用プリチャージ回路は、第1の電源電圧に接続されており、前記検査用プリチャージ回路は前記第1の電源電圧よりも低い第2の電源電圧に接続されており、前記ビット線対の一方のビット線に接続された通常動作用プリチャージ回路は第1の活性化信号で活性化され、前記ビット線対の他方のビット線に接続された通常動作用プリチャージ回路は第2の活性化信号で活性化され、前記ビット線対の一方のビット線に接続された検査用プリチャージ回路は第3の活性化信号で活性化され、前記ビット線対の他方のビット線に接続された検査用プリチャージ回路は第4の活性化信号で活性化され、前記第1乃至第4の各活性化信号は互いに独立に制御され、該半導体記憶装置の検査時において読出し動作前に、前記第1および第4の活性化信号を活性化するか、または前記第2および第3の活性化信号を活性化することにより、前記ビット線対の一方のビット線と前記ビット線対の他方のビット線とを互いに異なるプリチャージ電位までプリチャージするプリチャージ手段を備えている。

また、本発明の第2の半導体記憶装置において、前記通常動作用プリチャージ回路および検査用プリチャージ回路は共にPチャネル型トランジスタからなり、前記プリチャージ手段は、前記検査用プリチャージ回路のPチャネル型トランジスタと前記通常動作用プリチャージ回路のPチャネル型トランジスタとが駆動能力が等しいトランジスタで構成されていることが好ましい。

また、本発明の第3の半導体記憶装置は、SRAMを搭載した半導体記憶装置であって、前記SRAMのビット線対の各ビット線のそれぞれに通常動作用プリチャージ回路と検査用プリチャージ回路の各一端が並列接続されており、前記通常動作用プリチャージ回路と検査用プリチャージ回路とは同一の電源電圧に接続されており、前記ビット線対の一方のビット線に接続された通常動作用プリチャージ回路は第1の活性化信号で活性化され、前記ビット線対の他方のビット線に接続された通常動作用プリチャージ回路は第2の活性化信号で活性化され、前記ビット線対の一方のビット線に接続された検査用プリチャージ回路は第1のレベルシフト回路を介して第3の活性化信号で活性化され、前記ビット線対の他方のビット線に接続された検査用プリチャージ回路は第2のレベルシフト回路を介して第4の活性化信号で活性化され、前記第1乃至第4の各活性化信号は互いに独立に制御され、該半導体記憶装置の検査時において読出し動作前に、前記第1および第4の活性化信号を活性化するか、または前記第2および第3の活性化信号を活性化することにより、前記ビット線対の一方のビット線と前記ビット線対の他方のビット線とを互いに異なるプリチャージ電位までプリチャージするプリチャージ手段を備えている。

また、本発明の第3の半導体記憶装置において、前記通常動作用プリチャージ回路および検査用プリチャージ回路は共にPチャネル型トランジスタからなり、前記プリチャージ手段は、前記第1または第2のレベルシフト回路により前記検査用プリチャージ回路のPチャネル型トランジスタの駆動能力が前記通常動作用プリチャージ回路のPチャネル型トランジスタの駆動能力より小さくなるように制御することが好ましい。

また、本発明の第4の半導体記憶装置は、SRAMを搭載した半導体記憶装置であって、前記SRAMのビット線対の各ビット線のそれぞれ第1および第2のプリチャージ回路が接続されており、前記各プリチャージ回路は同一の電源電圧に接続されており、前記ビット線対の一方のビット線に接続された第1のプリチャージ回路は第1のレベルシフト回路を介して第1の活性化信号で活性化され、前記ビット線対の他方のビット線に接続された第2のプリチャージ回路は第2のレベルシフト回路を介して第2の活性化信号で活性化され、前記第1および第2の各活性化信号は互いに独立に制御され、前記第1および第2のプリチャージ回路の通常動作モードと検査動作モードの切替えは前記第1および第2のレベルシフト回路を制御する制御回路によって行なわれ、該半導体記憶装置の検査時において読出し動作前に、前記第1および第2の活性化信号を活性化することにより、前記ビット線対の一方のビット線と前記ビット線対の他方のビット線とを互いに異なるプリチャージ電位までプリチャージするプリチャージ手段を備えている。

また、本発明の第4の半導体記憶装置において、前記各プリチャージ回路はPチャネル型トランジスタからなり、前記プリチャージ手段は、前記第1および第2のレベルシフト回路により前記各プリチャージ回路の一方のPチャネル型トランジスタの駆動能力が前記各プリチャージ回路の他方のPチャネル型トランジスタの駆動能力よりも小さくなるよう制御することが好ましい。

また、本発明の第5の半導体記憶装置は、SRAMを搭載した半導体記憶装置であって、前記SRAMのビット線対の各ビット線のそれぞれに第1および第2のプリチャージ回路が接続されており、前記各プリチャージ回路は同一の電源電圧に接続されており、前記ビット線対の一方のビット線に接続された第1のプリチャージ回路は第1の遅延回路を介して第1の活性化信号で活性化され、前記ビット線対の他方のビット線に接続された第2のプリチャージ回路は第2の遅延回路を介して第2の活性化信号で活性化され、前記第1および第2の各活性化信号は互いに独立に制御され、前記プリチャージ回路の通常動作モードと検査動作モードの切替えは、前記第1および第2の遅延回路を制御する制御回路によって行なわれ、該半導体装置の検査時において読出し動作前に、前記第1および第2の活性化信号を活性化することにより、前記ビット線対の一方のビット線と前記ビット線対の他方のビット線とを互いに異なるプリチャージ電位までプリチャージするプリチャージ手段を備えている。

また、本発明の第5の半導体記憶装置において、前記各プリチャージ回路はPチャネル型トランジスタからなり、前記プリチャージ手段は、前記第1および第2の遅延回路により、前記各プリチャージ回路の一方のPチャネル型トランジスタの立ち上がり動作を前記各プリチャージ回路の他方のPチャネル型トランジスタの立ち上がり動作より早めて、前記各プリチャージ回路の一方のPチャネル型トランジスタのプリチャージが不十分な状態でプリチャージ動作を完了させることが好ましい。

また、本発明の第1の半導体記憶装置の検査方法は、本発明の第1の半導体記憶装置を用いた半導体記憶装置の検査方法であって、前記第1または第2の通常動作用プリチャージ回路が接続された前記ビット線対の一方のビット線に第1のプリチャージ電位を印加し、前記第1または第2の検査用プリチャージ回路が接続された前記ビット線対の他方のビット線に前記第1のプリチャージ電位より低い第2のプリチャージ電位を印加する第1の工程と、前記第1の工程の後に読出し動作を行なって動作マージン検査を行う第2の工程とを有する。

また、本発明の第2の半導体記憶装置の検査方法は、本発明の第2の半導体記憶装置を用いた半導体記憶装置の検査方法であって、前記第1または第2の通常動作用プリチャージ回路が接続された前記ビット線対の一方のビット線に前記第1の電源電圧を印加し、前記第1または第2の検査用プリチャージ回路が接続された前記ビット線対の他方のビット線に前記第2の電源電圧を印加する第1の工程と、前記第1の工程の後に読出し動作を行なって動作マージン検査を行う第2の工程とを有する。

また、本発明の第3の半導体記憶装置の検査方法は、本発明の第3の半導体記憶装置を用いた半導体記憶装置の検査方法であって、前記第1または第2の通常動作用プリチャージ回路が接続された前記ビット線対の一方のビット線に電源電圧を印加し、前記第1または第2の検査用プリチャージ回路が接続された前記ビット線対の他方のビット線に、前記第1または第2のレベルシフト回路によって前記電源電圧よりも低く設定された電位を印加する第1の工程と、前記第1の工程の後に読出し動作を行なって動作マージン検査を行う第2の工程とを有する。

また、本発明の第4の半導体記憶装置の検査方法は、本発明の第4の半導体記憶装置を用いた半導体記憶装置の検査方法であって、前記第2のプリチャージ回路が接続された前記ビット線対の他方のビット線に電源電圧を印加し、前記第1のプリチャージ回路が接続された前記ビット線対の一方のビット線に前記第1および第2のレベルシフト回路によって前記電源電圧よりも低く設定された電位を印加する第1の工程と、前記第1の工程の後に読出し動作を行なって動作マージン検査を行う第2の工程とを有する。

また、本発明の第5の半導体記憶装置の検査方法は、本発明の第5の半導体記憶装置を用いた半導体記憶装置の検査方法であって、前記第2のプリチャージ回路を第2の遅延回路を介して第2の活性化信号により活性化して、前記第2のプリチャージ回路が接続された前記ビット線対の他方のビット線に電源電圧を印加し、前記第1のプリチャージ回路を第1の遅延回路を介して第1の活性化信号により活性化し、前記第1のプリチャージ回路の立ち上がり動作を前記第1の遅延回路によって前記第2のプリチャージ回路の立ち上がり動作よりも早めて、プリチャージが不十分な状態で該プリチャージ動作を完了して、前記第1のプリチャージ回路が接続された前記ビット線対の一方のビット線に、前記電源電圧よりも低い電位を印加する第1の工程と、前記第1の工程の後に読出し動作を行なって動作マージン検査を行う第2の工程とを有する。

本発明に係る半導体記憶装置、およびその検査方法によれば、通常動作ではスクリーニングできない、工程不良等によるSNM値不足による信頼性不良を、初期検査でスクリーニングすることができる。

本発明の実施の形態について述べる前に、SNM値不足による“読みつぶし”不良について図面を参照しながら説明する。

SNM値不足による“読みつぶし”不良と、本発明の全ての実施の形態に共通する作用効果について、図5(a)〜図5(d)を参照しながら説明する。

図5(a)は、図3と同じく、SRAMメモリセルの動作時の各信号波形を示し、破線の円で囲んだ部分の波形を拡大したものを、図5(b)〜図5(d)に示す。

図5(b)のBL/XBLは、ビット線対の波形を示す。この図では、実線がBLを示し、破線がXBLを示す。また、BL=“H”であり、メモリセルに“1”のデータが蓄えられているものとする。SN,XSNは、メモリセルの内部ノードの波形を示し、SN=“H”、XSN=“L”である。

正常セルの場合、SN,XSNの波形は、実線で示したような波形となる。一方、前述のようなSNM値が不足したメモリセルの内部ノードの波形SN,XSNは、一点鎖線と破線で示すようになり、正常セルの実線波形に比べ、両者間の電位差が小さくなる。このような不良モードは、実使用時間の経過とともに、劣化が進み、図5(c)のように、内部ノードの電位差が無くなり、最終的に読出し不良に至ってしまう。

このような信頼性不良は、初期検査時にスクリーニングすることが望ましい。そこで、本発明において、初期検査時にスクリーニングする手段について、以下に述べる。

本発明では、図5(d)に示すように、読出し開始直前に“L”データを保存する内部ノードXSNにつながるビット線XBLの電位を、対となるビット線BLより高めに設定する。しかる後に、読出し動作を始めると、上記従来回路では、図5(b)に示すような、初期状態でSNM値が小さいメモリセルの“L”側ノードである、破線で示されるXSNの内部波形は、図5(b)に示すように低い電圧であったが、本発明回路では、その接続するビット線XBLの初期電位が上記のように高めに設定されていることから、図5(d)の破線で示すように、従来回路で読み出す場合より、電位が高くなる。この結果、対となるSNの電位は、相対的に低くなり、結果として、図5(d)に示されるように、より評価初期において、図5(c)に示す電位差が無くなった状態にすることが可能となり、早期に誤動作に至らせることができ、通常動作ではスクリーニングできないSNM値不足のメモリセルを、初期状態で不良と判定することができる。

以上のことから、読み出し前に、ビット線対の一方のビット線と、他方のビット線に互いに異なるプリチャージ電位を与えた後、読出し検査を行うことで、従来、初期不良として検出できなかったSNM値不足のメモリセルを、初期状態で不良と判定することができるようになる。

(実施の形態1)

以下、本発明の実施の形態1による半導体記憶装置について、図面を参照しながら説明する。

以下、本発明の実施の形態1による半導体記憶装置について、図面を参照しながら説明する。

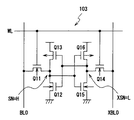

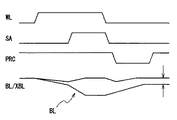

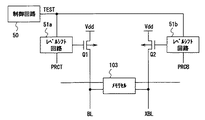

図1(a)は、本発明の実施の形態1による半導体記憶装置の回路構成を示す図、図1(b)は、該半導体記憶装置を構成するメモリセルの回路構成を示す図、図1(c)は、該半導体記憶装置における主要信号の動作波形の一例を示す図である。

図1において、図2及び図3と同一符号は、従来の半導体記憶装置におけるものと同一のものを示し、101a〜101dは通常動作用プリチャージ回路、102a〜102dはスクリーニング検査用プリチャージ回路、PRC0は、通常動作用プリチャージ回路101a〜101dの活性化信号(第1の活性化信号であり、以下、PRC0信号ともいう。)、PRCTは、正論理側ビット線BL0,BL1につながる検査用プリチャージ回路102a,102cの活性化信号(第2の活性化信号であり、以下、PRCT信号ともいう。)、PRCBは、負論理側ビット線BLX0,BLX1につながる検査用プリチャージ回路102b,102dの活性化信号(第3の活性化信号であり、以下、PRCB信号ともいう。)である。

以下、本実施の形態1の半導体記憶装置の構成を、より詳細に説明する。

まず、本実施の形態1の半導体記憶装置は、図1(a)に示すように、ビット線対をプリチャージするためのプリチャージ回路として、正論理側ビット線BL、負論理側ビット線XBLの各ビット線ごとに、2つのプリチャージ回路、つまり通常動作時用のプリチャージ回路101a,101b,101c,101dと、スクリーニング検査時用のプリチャージ回路102a,102b,102c,102dとを有する。

まず、本実施の形態1の半導体記憶装置は、図1(a)に示すように、ビット線対をプリチャージするためのプリチャージ回路として、正論理側ビット線BL、負論理側ビット線XBLの各ビット線ごとに、2つのプリチャージ回路、つまり通常動作時用のプリチャージ回路101a,101b,101c,101dと、スクリーニング検査時用のプリチャージ回路102a,102b,102c,102dとを有する。

それぞれのビット線BL0,XBL0,BL1,XBL1につながる通常動作用のプリチャージ回路101a,101b,101c,101dは、通常動作用のプリチャージ起動信号PRC0=“L”(第1の活性化信号)によって活性化され、ビット線を、“H”=“Vdd”状態にプリチャージする。正論理側ビット線BL0,BL1につながるスクリーニング検査時用プリチャージ回路102a,102cは、正論理ビット線プリチャージ回路活性化信号PRCT(第2の活性化信号)により活性化され、該正論理側ビット線のプリチャージ動作を行う。負論理側ビット線XBL0,XBL1につながるスクリーニング検査時用プリチャージ102b,102dは、負論理ビット線プリチャージ回路活性化信号PRCB(第3の活性化信号)によって活性化し、該負論理側ビット線をプリチャージする。ここで、スクリーニング検査用プリチャージ回路102a〜102dは、通常動作用プリチャージ回路101a〜101dとは、異なる電位までビット線をプリチャージする機能を有する回路で構成されている。

また、図1(b)において、メモリセル103において、Q11、Q12、Q13、Q14、Q15、Q16は、メモリセル103を構成するトランジスタである。

次に、本実施の形態1の半導体記憶装置の動作について説明する。

通常の動作時には、PRC0信号(第1の活性化信号)のみが活性化し、通常動作用プリチャージ回路101a〜101dのみが動作して、図3に示したように、ビット線対を、読出し動作前に“H”=“Vdd”状態にプリチャージする。

通常の動作時には、PRC0信号(第1の活性化信号)のみが活性化し、通常動作用プリチャージ回路101a〜101dのみが動作して、図3に示したように、ビット線対を、読出し動作前に“H”=“Vdd”状態にプリチャージする。

次に、SNM不足ビットをスクリーニングする、スクリーニング検査時の動作について説明する。

この検査時には、ビット線対の、メモリセル内部の“L”データが保持されるノードにつながるビット線を第1のプリチャージ電位にプリチャージし、該ビット線対の、メモリセル内部の“H”データが保持されるノードにつながるビット線を第1のプリチャージ電位より低い第2のプリチャージ電位にプリチャージする。

この検査時には、ビット線対の、メモリセル内部の“L”データが保持されるノードにつながるビット線を第1のプリチャージ電位にプリチャージし、該ビット線対の、メモリセル内部の“H”データが保持されるノードにつながるビット線を第1のプリチャージ電位より低い第2のプリチャージ電位にプリチャージする。

たとえば、メモリセル103が“1”のデータを保持している時、内部ノードSNが“H”状態で、相補側ノードXSNは“L”の状態になっていたとする。

該当セルデータを読み出すのに先立って、該当セルの保持するデータとは相補型のデータをビット線上に読み出す。つまり、正論理側ビット線BL0に、正論理側内部ノードSNに保持される“H”状態とは相補型の“L”データを読出し、負論理側ビット線XBL0には、負論理側内部ノードXSNの“L”データと相補型の“H”データを読み出す。これは、半導体記憶装置の検査で通常用いられる検査パターンの1つ、例えば“チェッカーパターン”などのように“H”、“L”を交互に書込み/読出しを行う検査パターンを用いれば容易に行える。これにより、正論理側ビット線BL0は“L”状態となり、負論理側ビット線XBL0は“H”状態となる。このとき、“H”状態のビット線の電位は、通常の“H”=“Vdd”電位であり、これは第1のプリチャージ電位と等しい。

この後、正論理側プリチャージ回路活性信号PRCTを活性化することにより、“L”状態のBL0をプリチャージする。このとき、スクリーニング検査用プリチャージ回路102は、通常の“H”=“Vdd”電位より低い電位までプリチャージする機能を有しているので、正論理側ビット線BL0は“H”より低い電位である第2のプリチャージ電位となる。また、負論理側ビット線XBL0は直前の読出し動作でセンスアンプにより電位が前記第1のプリチャージ電位と等しい“H”=“Vdd”となっているので、特にプリチャージする必要はない。

これにより、ビット線対BL0/XBL0には、スクリーニング検査用プリチャージ回路102によって設定される電位差が生じる。この後に、通常と同じように読出し動作を行えば、前述のようにSNM値がセンスアンプの検知レベルに対してマージンの少ないメモリセル103では誤読み出しが行なわれ、不良と判定されてスクリーニングされることになる。

一方、メモリセルの負論理側ノードXSNに“H”を書き込んだメモリセル103が“0”のデータを保持している場合には、負論理側プリチャージ回路活性信号PRCBを活性化することで、同様に検査できる。

次に、プリチャージ回路のより詳細な内容を、図7に示す。通常動作用のプリチャージ起動信号PRC0(第1の活性化信号)には、通常動作用プリチャージ回路101a,101bをそれぞれ構成するプリチャージ用トランジスタQ1、Q2がつながっており、ビット線対を電源電位“Vdd”にプリチャージする。スクリーニング検査時用プリチャージ活性化信号PRCT/PRCB(第2、第3の活性化信号)には、スクリーニング検査用プリチャージ回路102a,102bをそれぞれ構成するトランジスタQ3、Q4がつながっており、ビット線対を電源電位“Vdd”にプリチャージする(すなわち、これらの信号PRCT/PRCBは“L”=“Vss”状態でビット線対をプリチャージし、“H”=“Vdd”状態でビット線対をプリチャージしない)。

これら4個のトランジスタの駆動能力は、Q1=Q2>Q3=Q4と設定され、Q1、Q2のトランジスタは通常の動作時のプリチャージ動作に十分な駆動能力を有するが、Q3、Q4のトランジスタはQ1、Q2に比べて駆動能力が小さく、通常の動作タイミングではビット線を十分に“H”=“Vdd”レベルまでプリチャージする駆動能力を有さない。このため、スクリーニング検査時には、Q3、Q4のトランジスタを使用することでビット線対に電位差を生じさせることができる。

これにより、本実施の形態1においては、通常の検査では不良と判定されないSNM値不足のメモリセル103を、スクリーニング検査によってスクリーニングすることが可能となり、かかる検査を行った半導体記憶装置の市場での信頼性を向上することができる。

このように、本実施の形態1による半導体記憶装置によれば、SRAMを搭載した半導体記憶装置において、SRAMのビット線対の各ビット線のそれぞれに通常動作用プリチャージ回路と検査用プリチャージ回路の各一端を並列接続し、通常動作用プリチャージ回路と検査用プリチャージ回路とは同一の電源電圧に接続し、ビット線対の各ビット線のそれぞれに接続した通常動作用プリチャージ回路は同一の第1の活性化信号で活性化し、ビット線対の一方のビット線に接続した検査用プリチャージ回路は第2の活性化信号で活性化し、ビット線対の他方のビット線に接続した検査用プリチャージ回路は第3の活性化信号で活性化し、第1乃至第3の各活性化信号は互いに独立に制御されるものとし、検査時においては、読出し動作前に、前記ビット線対の他方または一方のビット線が第1のプリチャージ電位にある状態で、前記第2または第3の活性化信号を活性化することによって、前記ビット線対の一方または他方のビット線を第2のプリチャージ電位にして、ビット線対の一方のビット線と、ビット線対の他方のビット線とを、互いに異なるプリチャージ電位までプリチャージするようにしたので、通常動作ではスクリーニングできない工程不良等によるSNM値不足による信頼性不良を、初期検査でスクリーニングすることができる効果が得られる。

(実施の形態2)

以下、本発明の実施の形態2による半導体記憶装置について、図面を参照しながら説明する。

本実施の形態2の半導体記憶装置の基本的回路構成は、上記実施の形態1と同じ図1で表されるため、その説明は省略する。

以下、本発明の実施の形態2による半導体記憶装置について、図面を参照しながら説明する。

本実施の形態2の半導体記憶装置の基本的回路構成は、上記実施の形態1と同じ図1で表されるため、その説明は省略する。

本実施の形態2では、プリチャージ回路の回路構成が、上記実施の形態1と異なっている。

具体的には、図7に示した実施の形態1では、通常動作用プリチャージトランジスタ、つまり通常動作用プリチャージ回路を構成するトランジスタQ1、Q2と、スクリーニング検査用プリチャージトランジスタ、つまりスクリーニング検査用プリチャージ回路を構成するトランジスタQ3、Q4は、ともにP型半導体で構成されているが、図8に示す本実施の形態2では、通常動作用プリチャージトランジスタQ1、Q2は、P型半導体で構成されており、スクリーニング検査用プリチャージトランジスタQ3、Q4は、N型半導体で構成されている。

具体的には、図7に示した実施の形態1では、通常動作用プリチャージトランジスタ、つまり通常動作用プリチャージ回路を構成するトランジスタQ1、Q2と、スクリーニング検査用プリチャージトランジスタ、つまりスクリーニング検査用プリチャージ回路を構成するトランジスタQ3、Q4は、ともにP型半導体で構成されているが、図8に示す本実施の形態2では、通常動作用プリチャージトランジスタQ1、Q2は、P型半導体で構成されており、スクリーニング検査用プリチャージトランジスタQ3、Q4は、N型半導体で構成されている。

また、これに伴い、スクリーニング検査用プリチャージ回路の活性化信号PRCT/PRCB(第2、第3の活性化信号)の極性も、反転しており、これらの信号XPRCT/XPRCBは、“H”=“Vdd”状態で、ビット線対をプリチャージし、“L”=“Vss”状態では、ビット線対を、プリチャージしないものである。

本実施の形態2においても、上記実施の形態1と同様にSNM値不足のメモリセル103のスクリーニングを行うが、本実施の形態2においては、スクリーニング検査用プリチャージトランジスタがN型半導体トランジスタで構成されているため、スクリーニング検査用プリチャージ回路を活性化するとき、該N型半導体トランジスタよりなる検査用プリチャージトランジスタのソース電位は“Vdd”、そのゲート電位も“VDD”となるため、ビット線対のプリチャージ電位は、“Vdd”よりトランジスタの閾値電圧分だけ低いレベルまでしか、プリチャージされない。

このことにより、本実施の形態2においては、実施の形態1と同様に、スクリーニング検査時において、読出し動作前にビット線対に電位差を設けることができる。これにより、本実施の形態2では、通常の検査では不良と判定されないSNM値不足のメモリセル103をスクリーニングすることが可能となり、かかる検査を行った半導体記憶装置の市場での信頼性を向上することができる。

また、実施の形態1では、トランジスタの駆動能力差によりビット線のプリチャージ電位に電位差を設けていたため、検査温度やプリチャージ時間により発生させる電位差が変動するが、本実施の形態2では、閾値電圧が電位差となって現れるため、上記実施の形態1より安定した電位差を生じさせることができる。

(実施の形態3)

以下、本発明の実施の形態3による半導体記憶装置について、図面を参照しながら説明する。

以下、本発明の実施の形態3による半導体記憶装置について、図面を参照しながら説明する。

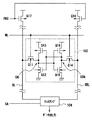

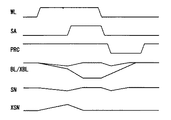

本実施の形態3による半導体記憶装置は、図6(a)に示すように、ビット線対をプリチャージするプリチャージ回路として、各ビット線ごとに、すなわち、正論理側ビット線、負論理側ビット線、の各々ごとに、2つのプリチャージ回路、つまり通常動作用プリチャージ回路101a,101b,101c,101dと、スクリーニング検査用プリチャージ回路102a,102b,102c,102dとを、設けたものである。

すなわち、上記実施の形態1では、正論理側ビット線BLにつながる通常動作用プリチャージ回路と、負論理側ビット線XBLにつながる通常動作用プリチャージ回路は、ともにプリチャージ活性化信号PRC0により活性化されていたが、本実施の形態3の半導体記憶装置では、図6(a)に示すように、正論理側ビット線BLにつながる通常動作用プリチャージ回路101aと、負論理側ビット線XBLにつながる通常動作用プリチャージ回路101bは、それぞれ別の活性化信号PRC0T、PRC0Bにより、活性化される構成としている。

なお、図6(b)において、Q11、Q12、Q13、Q14、Q15、Q16は、図1(b)におけると同様、メモリセル103を構成するトランジスタである。

次に、プリチャージ回路のより詳細な内容を、図9に示す。図9において、図7と同様に、Q1、Q2は、通常動作用プリチャージ回路101a,101bを構成するトランジスタ、Q3、Q4は、スクリーニング検査用プリチャージ回路102a,102bを構成するトランジスタであり、それぞれのトランジスタQ1、Q2、Q3、Q4のゲートは、プリチャージ活性化信号PRC0T、PRC0B、PRCT、PRCBにより制御される。

ここで、プリチャージトランジスタQ1、Q2、Q3、Q4は、P型トランジスタで構成されているので、これらの活性化信号PRC0T、PRC0B、PRCT、PRCBが“L”(=“Vss”)状態で、該プリチャージトランジスタQ1、Q2、Q3、Q4は導通状態となり、ビット線をプリチャージし、活性化信号PRC0T、PRC0B、PRCT、PRCBが“H”(=“Vdd”)状態で、プリチャージトランジスタQ1、Q2、Q3、Q4は非導通状態となり、ビット線をプリチャージしない。また、トランジスタQ1とQ2は、電源Vdd0に接続され、トランジスタQ3とQ4は、別電源Vdd1に接続されており、ここで、電源Vdd0と電源Vdd1は、独立に電位を設定できるものとする。

この実施の形態3の構成では、活性化信号PRC0Tと、PRC0Bを同時に駆動し、且つVdd0=Vdd1=Vddとするようにすれば、上記実施の形態1と同様な動作を行うことができる。

さらに、電源Vdd0と、電源Vdd1とを、独立して制御できることから、スクリーニング検査時のプリチャージにおいて、たとえば、メモリセル103に“H”データが蓄えられている時、“H”がつながる正論理側ビット線BLを検査する際には、活性化信号PRCTと、PRC0Bとを、活性化し、且つVdd1<Vdd0となる電位設定を行うことで、ビット線対に所望の電位差を設定することができる。

このとき、トランジスタQ3、Q4の駆動能力は、トランジスタQ1、Q2のものに比べて小さくする必要はなく、等しいものとすればよい。また、このとき、通常の電源電圧Vddに対して、Vdd1<Vdd0<Vddにも、Vdd<Vdd1<Vdd0にも、Vdd1<Vdd<Vdd0にも、設定可能であり、より細かなスクリーニング条件を設定することが可能となる。

また、前述の実施の形態1,2では、検査パターンとして“チェッカーパターン”、あるいは“コラムバー”のような、検査されるメモリセルが保存しているデータと相補関係のデータを所定のビット線に事前に読み出し、ビット線対をこれから読み出すデータとは反転した状態に設定する必要があったが、本実施の形態3では、読出し前のプリチャージ動作ごとに、ビット線電位を任意に設定することができるため、検査パターンの設定は上記のものに限定されるものではなく、その自由度が高まり、よりスクリーニング効果を高めることができる。

以上のように、本実施の形態3による半導体記憶装置によれば、SRAMを搭載した半導体記憶装置において、SRAMのビット線対の各ビット線のそれぞれに通常動作用プリチャージ回路と検査用プリチャージ回路の各一端を並列接続し、通常動作用プリチャージ回路は第1の電源電圧に接続し、検査用プリチャージ回路は第1の電源電圧よりも低い第2の電源電圧に接続し、ビット線対の一方のビット線に接続した通常動作用プリチャージ回路は第1の活性化信号で活性化し、ビット線対の他方のビット線に接続した通常動作用プリチャージ回路は第2の活性化信号で活性化し、ビット線対の一方のビット線に接続した検査用プリチャージ回路は第3の活性化信号で活性化し、前記ビット線対の他方のビット線に接続した検査用プリチャージ回路は第4の活性化信号で活性化し、第1乃至第4の各活性化信号は互いに独立に制御されるものとし、検査時において読出し動作前に第1および第4の活性化信号を活性化するか、または第2および第3の活性化信号を活性化することによって、ビット線対の一方のビット線とビット線対の他方のビット線とを互いに異なるプリチャージ電位までプリチャージする手段を備え、上記各ビット線ごとに設けた通常動作用プリチャージ回路と検査用プリチャージ回路を異なる電源に接続し、これら4つのプリチャージ回路をそれぞれ異なる活性化信号により活性化することによりビット線対に所望の電位差を得る構成としたので、より細かなスクリーニング条件を設定することが可能となり、また、このように読出し前のプリチャージ動作ごとにビット線電位を任意に設定することができることにより、検査パターンの自由度が高まり、よりスクリーニング効果を高めることができる。

(実施の形態4)

以下、本発明の実施の形態4による半導体記憶装置について、図面を参照しながら説明する。

上記実施の形態3では、図9に示した、通常動作用、検査用の各プリチャージトランジスタQ1、Q2、Q3、Q4のソース電位を制御することによって、各プリチャージ回路101a,101b、102a,102bによるビット線プリチャージ電位を制御し、ビット線対に電位差を発生するようにしている。

以下、本発明の実施の形態4による半導体記憶装置について、図面を参照しながら説明する。

上記実施の形態3では、図9に示した、通常動作用、検査用の各プリチャージトランジスタQ1、Q2、Q3、Q4のソース電位を制御することによって、各プリチャージ回路101a,101b、102a,102bによるビット線プリチャージ電位を制御し、ビット線対に電位差を発生するようにしている。

これに対し、本実施の形態4では、図10に示すように、通常動作用プリチャージトランジスタQ1、Q2、スクリーニング検査用プリチャージトランジスタQ3、Q4のそれぞれのソース電位は、Vddとし、該各スクリーニング検査用プリチャージトランジスタQ3、Q4を制御する活性化信号PRCT、PRCBの電圧を、該各スクリーニング検査用プリチャージトランジスタQ3、Q4に接続したレベルシフト回路105a,105bで制御するようにしたものである。これにより、ビット線を駆動する各スクリーニング検査用プリチャージトランジスタQ3、Q4の駆動能力を制御し、これにつき上記実施の形態1で示したようなトランジスタの駆動能力差を設けて、ビット線対に電位差を発生させるようにしたものであり、これにより、本実施の形態4においても、上記実施の形態1と同様の効果を得ることができる。

このように、本実施の形態4による半導体記憶装置によれば、SRAMを搭載した半導体記憶装置において、SRAMのビット線対の各ビット線のそれぞれに通常動作用プリチャージ回路と検査用プリチャージ回路の各一端を並列接続し、各プリチャージ回路は同一の電源電圧に接続し、ビット線対の一方のビット線に接続した通常動作用プリチャージ回路は第1の活性化信号で活性化し、ビット線対の他方のビット線に接続した通常動作用プリチャージ回路は第2の活性化信号で活性化し、ビット線対の一方のビット線に接続した検査用プリチャージ回路は第3の活性化信号で活性化し、ビット線対の他方のビット線に接続した検査用プリチャージ回路は第4の活性化信号で活性化し、第1乃至第4の各活性化信号は互いに独立に制御されるものとし、検査時において読出し動作前に第1および第4の活性化信号を活性化するか、または第2および第3の活性化信号を活性化することによって、ビット線対の一方のビット線とビット線対の他方のビット線とを互いに異なるプリチャージ電位までプリチャージする手段を備え、通常動作用、検査用の各プリチャージトランジスタのそれぞれのソース電位はVddとし、スクリーニング検査用プリチャージトランジスタを制御する活性化信号の電圧をそれぞれのスクリーニング検査用プリチャージトランジスタQ3、Q4に接続したレベルシフト回路で制御するようにし、この際、プリチャージトランジスタの駆動能力差を設けてビット線対に電位差を発生させるようにしたので、上記実施の形態1と同様、通常動作ではスクリーニングできない工程不良等によるSNM値不足による信頼性不良を、初期検査でスクリーニングできる効果を得ることができる。

(実施の形態5)

以下、本発明の実施の形態5による半導体記憶装置について、図面を参照しながら説明する。

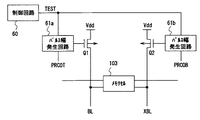

図10に示される上記実施の形態4では、通常検査用プリチャージ回路101a,101bと、スクリーニング検査用プリチャージ回路102a,102b、及びそれぞれのプリチャージ回路のトランジスタQ1〜Q4を制御する制御信号PRCT、PRCB、PRC0T、PRC0Bを設けて、各プリチャージ回路の制御を行うようにしていたが、図11に示す本実施の形態5では、通常動作時と、検査動作時の機能切替えを行うテスト信号TESTにより、レベルシフト回路51a,51bの出力信号レベルを制御するようにし、これにより、各プリチャージ回路の制御を行い、各プリチャージトランジスタの駆動能力を変えて、ビット線対に、電位差を発生させるようにしたものである。

以下、本発明の実施の形態5による半導体記憶装置について、図面を参照しながら説明する。

図10に示される上記実施の形態4では、通常検査用プリチャージ回路101a,101bと、スクリーニング検査用プリチャージ回路102a,102b、及びそれぞれのプリチャージ回路のトランジスタQ1〜Q4を制御する制御信号PRCT、PRCB、PRC0T、PRC0Bを設けて、各プリチャージ回路の制御を行うようにしていたが、図11に示す本実施の形態5では、通常動作時と、検査動作時の機能切替えを行うテスト信号TESTにより、レベルシフト回路51a,51bの出力信号レベルを制御するようにし、これにより、各プリチャージ回路の制御を行い、各プリチャージトランジスタの駆動能力を変えて、ビット線対に、電位差を発生させるようにしたものである。

すなわち、本実施の形態5による半導体記憶装置は、図11(a)に示すように、ビット線対をプリチャージするプリチャージ回路として、各ビット線ごとに1つのプリチャージ回路を設け、具体的にはビット線BL0,XBL0,BL1,XBL1にプリチャージ回路101a,101b,101c,101dを設け、正論理側ビット線BLにつながるプリチャージ回路101a,101cと、負論理側ビット線XBLにつながるプリチャージ回路101b,101dは、それぞれ別の活性化信号PRCT、PRCBにより、制御回路50により制御される第1、第2のレベルシフト回路51a,51bを介して活性化される構成としている。

また、図11(b)に示すように、正論理側ビット線BLにつながるプリチャージ回路を構成するトランジスタQ1のゲートは、レベルシフト回路51aにて制御回路50からの制御信号TESTに応じてレベルシフトされた活性化信号PRCTにより制御され、負論理側ビット線XBLにつながるプリチャージ回路を構成するトランジスタQ2のゲートは、レベルシフト回路51bにて制御回路50からの制御信号TESTに応じてレベルシフトされた活性化信号PRCBにより制御される。

通常動作時、制御回路50からのテスト信号TEST=“L”であるときには、レベルシフト回路51a,51bでは、レベルシフト動作は行わず、通常の、電圧レベル“H”=“Vdd”、または“L”=“Vss”での出力を行う。一方、検査動作時には、つまり制御回路50からのテスト信号TEST=“H”であるときには、プリチャージ活性化信号PRCT,PRCBのレベルを、レベルシフト回路51a,51bにより制御し、プリチャージトランジスタQ1、Q2を、通常より低い駆動能力とする。これにより、“L”側ビット線のプリチャージ電位は、“Vdd”までは、プリチャージされず、読出し前に、ビット線には電位差が生じ、前述のスクリーニング効果が現れることとなり、これにより、本実施の形態5においても、上記実施の形態1と同様の効果を得ることができることとなる。

このような本実施の形態5による半導体記憶装置によれば、SRAMを搭載した半導体記憶装置において、SRAMのビット線対の各ビット線のそれぞれにプリチャージ回路を接続し、各プリチャージ回路は同一の電源電圧に接続し、ビット線対の一方のビット線に接続した第1のプリチャージ回路は第1のレベルシフト回路を介して第1の活性化信号で活性化し、ビット線対の他方のビット線に接続した第2のプリチャージ回路は第2のレベルシフト回路を介して第2の活性化信号で活性化し、第1および第2の各活性化信号は互いに独立に制御されるものとし、第1および第2の各プリチャージ回路の通常動作モードと検査動作モードとの切替えは第1および第2の各レベルシフト回路を制御する制御回路によって行い、検査時において読出し動作前に第1および第2の活性化信号を活性化することによってビット線対の一方のビット線とビット線対の他方のビット線とを互いに異なるプリチャージ電位までプリチャージする手段を備え、通常動作時と検査動作時の機能切替えを行うテスト信号TESTにより第1および第2のレベルシフト回路の出力信号レベルを制御し、プリチャージトランジスタの駆動能力を変えてビット線対に電位差を発生させるようにしたので、たとえば、“L”側ビット線のプリチャージ電位は“Vdd”まではプリチャージされず、読出し前にビット線対に電位差が生じ、スクリーニング効果が現れるようになるため、上記実施の形態1と同様、通常動作ではスクリーニングできない工程不良等によるSNM値不足による信頼性不良を、初期検査でスクリーニングできる効果を得ることができる。

(実施の形態6)

以下、本発明の実施の形態6による半導体記憶装置について、図面を参照しながら説明する。

本実施の形態6による半導体記憶装置は、図12に示すように、プリチャージ回路の活性化信号であるプリチャージ制御信号のパルス幅を、通常動作時と、検査動作時とで可変とする機能を有するようにしたものである。

以下、本発明の実施の形態6による半導体記憶装置について、図面を参照しながら説明する。

本実施の形態6による半導体記憶装置は、図12に示すように、プリチャージ回路の活性化信号であるプリチャージ制御信号のパルス幅を、通常動作時と、検査動作時とで可変とする機能を有するようにしたものである。

すなわち、本実施の形態6による半導体記憶装置は、図12(a)に示すように、ビット線対をプリチャージするプリチャージ回路として、各ビット線ごとに1つのプリチャージ回路を設け、具体的にはビット線BL0,XBL0,BL1,XBL1にプリチャージ回路101a,101b,101c,101dを設け、正論理側ビット線BLにつながるプリチャージ回路101a,101cと、負論理側ビット線XBLにつながるプリチャージ回路101b,101dは、制御回路60により制御される第1、第2のパルス幅発生回路61a,61bからのそれぞれ別の活性化信号PRCT、PRCBにより活性化される構成としている。

また、図12(b)に示すように、正論理側ビット線BLにつながるプリチャージ回路を構成するトランジスタQ1のゲートは、パルス幅発生回路61aにて制御回路60からの制御信号TESTに応じて活性化信号PRCOTを遅延して得られる信号PRCTにより制御され、負論理側ビット線XBLにつながるプリチャージ回路を構成するトランジスタQ2のゲートは、パルス幅発生回路61bにて制御回路60からの制御信号TESTに応じて活性化信号PRCOTを遅延して得られる信号PRCBにより制御される。

通常、パルス幅を発生する回路61は、図13(a)に示すように遅延回路41と論理回路40a及び40bで構成され、その遅延回路41は、図13(c)に示すようなインバータ42の多段接続によって構成される。このインバータ42は、Pチャネルトランジスタ42aとNチャネルトランジスタ42bとをVdd電源とVss電源との間に直列に接続してなるもので、両トランジスタの共通ゲートが入力ノード、両トランジスタの接続点が出力ノードとなっている。

そして、上記パルス発生回路を構成するインバータ42の一部に、図13(d)に示すように、通常動作と、検査動作を切替えるTEST信号を入力する回路を設けることにより、この入力によって、上記遅延回路41の遅延時間を可変とし、すなわちその出力パルス幅を可変とし、ひいては、その出力によってプリチャージトランジスタの駆動能力を切替える構成とすることができ、図12(a),(b)に示す本実施の形態6の第1,第2の活性化信号PRCOT,PRCOBを入力とするパルス幅発生回路61a,61bを、容易に実現することができるものである。

なお、図13(b)は、本実施の形態6の第1の活性化信号PRCOTを入力とするパルス幅発生回路61aを示しており、また、図13(d)は、上記パルス幅発生回路61aにおける遅延回路を構成する1つのインバータを示している。このインバータは、図13(c)に示すインバータ42のNチャネルトランジスタ42bと低電位側電源Vssとの間に、並列接続のPチャネルトランジスタ43a及び43bを接続してなるもので、その一方のPチャネルトランジスタ43aのゲートは高電位側電源Vddに接続され、その他方のPチャネルトランジスタ43bのゲートには制御回路60からのテスト信号TESTが入力される。

このようにすれば、スクリーニング検査時には、制御回路60からのテスト信号TESTを、Pチャネルトランジスタ43bがオンして遅延回路41の遅延時間が短くなるよう“L”レベルとして、プリチャージパルス幅を短くすることで、ビット線が“L”レベルから“H”レベルに十分にプリチャージする前に、プリチャージ動作を完了させることができるものであり、その結果、読出し前のビット線電位差を生じさせることができ、前述のように、スクリーニングを行うことができる。

ここで、上述したように従来技術でのスクリーニング手法では、センスアンプの動作タイミングを早めることによりスクリーニングを行っているところ、最近の半導体素子の低電圧化及び高速化に伴いセンスアンプの動作タイミングはほとんどマージンの無い設計となっているため、上記従来の方法では実質的に動作タイミングを早めることはほぼ不可能であったが、一方、本実施の形態6では、アクセス速度に直接関与しないプリチャージ時間を制御しているため、SRAMの動作マージンを損ねることなく、容易にこのスクリーニングを実現できるものであり、本実施の形態6においては、このようにして上記実施の形態1と同様の効果を得ることができるものである。

以上のような本実施の形態6による半導体集積装置によれば、SRAMを搭載した半導体記憶装置において、SRAMのビット線対の各ビット線のそれぞれにプリチャージ回路を接続し、各プリチャージ回路は同一の電源電圧に接続し、ビット線対の一方のビット線に接続した第1のプリチャージ回路は第1の遅延回路を介して第1の活性化信号で活性化し、ビット線対の他方のビット線に接続した第2のプリチャージ回路は第2の遅延回路を介して第2の活性化信号で活性化し、第1および第2の各活性化信号は互いに独立に制御されるものとし、プリチャージ回路の通常動作モードと検査動作モードとの切替えは第1および第2の遅延回路を制御する制御回路によって行い、検査時において読出し動作前に記第1および第2の活性化信号を活性化することによってビット線対の一方のビット線と前記ビット線対の他方のビット線とを互いに異なるプリチャージ電位までプリチャージする手段が構成されるものとし、さらに、上記構成において各プリチャージ回路はPチャネル型トランジスタからなり、ビット線対の一方のビット線とビット線対の他方のビット線とを互いに異なるプリチャージ電位までプリチャージする手段は、第1および第2の遅延回路により各プリチャージ回路の一方のPチャネル型トランジスタの立ち上がり動作を、各プリチャージ回路の他方のPチャネル型トランジスタの立ち上がり動作よりも早めて、各プリチャージ回路の一方のPチャネル型トランジスタのプリチャージが不十分な状態でプリチャージ動作を完了するよう制御されるようにしたので、スクリーニング検査時にはプリチャージパルス幅を短くしてビット線が“L”レベルから“H”レベルに十分にプリチャージする前にプリチャージ動作を完了させることができるようになり、その結果、十分に読出し前のビット線電位差を生じさせることができ、スクリーニングを確実に行うことができる。また、従来技術のスクリーニング手法では、最近の半導体素子の低電圧化及び高速化に伴いセンスアンプの動作タイミングはほとんどマージンの無い設計となっているため、実質的にスクリーニングのために動作タイミングを早めることはほぼ不可能であったが、本実施の形態6では、アクセス速度に直接関与しないプリチャージ時間を制御するようにしているため、SRAMの動作マージンを損ねることなく容易にこのスクリーニングを実現することができるものである。

以上説明したように、本発明の半導体記憶装置、及びその検査方法は、通常動作ではスクリーニングできない、工程不良等によるSNM値不足による信頼性不良を、初期検査でスクリーングすることができ、特に、SRAMのスクリーニング方法等に有用である。

PRC0 通常動作時用プリチャージ活性化信号

PRCT スクリーニング検査時用正論理ビット線プリチャージ回路活性化信号

PRCB スクリーニング検査時用負論理ビット線プリチャージ回路活性化信号

101a,101b,101c,101d 通常動作時用プリチャージ回路

102a,102b,102c,102d スクリーニング検査時用プリチャージ回路

103 メモリセル

WL ワード線活性化信号

SA センスアンプ活性化信号

BL0 正論理側ビット線

XBL0 負論理側ビット線

SN 正論理側メモリセル内部ノード

XSN 負論理側メモリセル内部ノード

Q1、Q2、Q3、Q4 プリチャージ用トランジスタ

PRCT スクリーニング検査時用正論理ビット線プリチャージ回路活性化信号

PRCB スクリーニング検査時用負論理ビット線プリチャージ回路活性化信号

101a,101b,101c,101d 通常動作時用プリチャージ回路

102a,102b,102c,102d スクリーニング検査時用プリチャージ回路

103 メモリセル

WL ワード線活性化信号

SA センスアンプ活性化信号

BL0 正論理側ビット線

XBL0 負論理側ビット線

SN 正論理側メモリセル内部ノード

XSN 負論理側メモリセル内部ノード

Q1、Q2、Q3、Q4 プリチャージ用トランジスタ

Claims (17)

- SRAMを搭載した半導体記憶装置であって、

前記SRAMのビット線対の一方のビット線に第1の通常動作用プリチャージ回路および第1の検査用プリチャージ回路の各一端が並列接続されており、

前記SRAMのビット線対の他方のビット線に第2の通常動作用プリチャージ回路および第2の検査用プリチャージ回路の各一端が並列接続されており、

前記第1および第2の通常動作用プリチャージ回路および第1および第2の検査用プリチャージ回路は同一の電源電圧に接続されており、

前記ビット線対の一方および他方のビット線のそれぞれに接続された第1および第2の通常動作用プリチャージ回路は共に第1の活性化信号で活性化され、

前記ビット線対の一方のビット線に接続された第1の検査用プリチャージ回路は第2の活性化信号で活性化され、

前記ビット線対の他方のビット線に接続された第2の検査用プリチャージ回路は第3の活性化信号で活性化され、

前記第1ないし第3の活性化信号は互いに独立に制御され、

該半導体記憶装置の検査時において読出し動作前に、前記ビット線対の他方のビット線が第1のプリチャージ電位にある状態で、前記第2の活性化信号を活性化することにより、前記ビット線対の一方のビット線を第2のプリチャージ電位にして、または前記ビット線対の一方のビット線が第1のプリチャージ電位にある状態で、前記第3の活性化信号を活性化することにより、前記ビット線対の他方のビット線を第2のプリチャージ電位にして、前記ビット線対の一方のビット線と前記ビット線対の他方のビット線とを互いに異なるプリチャージ電位までプリチャージするプリチャージ手段を、備えた、

ことを特徴とする半導体記憶装置。 - 請求項1に記載の半導体記憶装置において、

前記ビット線対の各ビット線の電位を設定するセンスアンプは、

該半導体記憶装置の検査時において読出し動作前に、メモリセルに保持されているデータに応じて、前記ビット線対の一方のビット線をHまたはLレベルの所定の論理電位に設定し、その他方のビット線を、該一方のビット線に設定される論理電位とは相補型の論理電位に設定し、

前記プリチャージ手段は、前記センスアンプにより前記ビット線対の他方のビット線が前記第1のプリチャージ電位と等しいHレベル論理電位に設定されているとき、前記第2の活性化信号を活性化して、Lレベル論理電位に設定されている一方のビット線を、前記Hレベル論理電位より低い第2のプリチャージ電位に充電し、前記センスアンプにより前記一方のビット線が前記第1のプリチャージ電位と等しいHレベル論理電位に設定されているとき、前記第3の活性化信号を活性化して、Lレベル論理電位に設定されている他方のビット線を、前記Hレベル論理電位より低い第2のプリチャージ電位に充電する、

ことを特徴とする半導体記憶装置。 - 請求項1に記載の半導体記憶装置において、

前記第1および第2の通常動作用プリチャージ回路および前記第1および第2の検査用プリチャージ回路は共にPチャネル型トランジスタからなり、

前記プリチャージ手段は、前記第1および第2の検査用プリチャージ回路のPチャネル型トランジスタが前記第1および第2の通常動作用プリチャージ回路のPチャネル型トランジスタより駆動能力が小さいトランジスタよりなる、

ことを特徴とする半導体記憶装置。 - 請求項1に記載の半導体記憶装置において、

前記第1および第2の通常動作用プリチャージ回路はPチャネル型トランジスタからなり、

前記第1および第2の検査用プリチャージ回路はNチャネル型トランジスタからなり、

前記プリチャージ手段は、前記第1および第2の通常動作用プリチャージ回路が接続されたビット線に第1のプリチャージ電位を印加し、前記第1および第2の検査用プリチャージ回路が接続されたビット線に前記第1のプリチャージ電位よりも前記Nチャネル型トランジスタの閾値電圧分低い第2のプリチャージ電位を印加してプリチャージを行う、

ことを特徴とする半導体記憶装置。 - SRAMを搭載した半導体記憶装置であって、

前記SRAMのビット線対の一方のビット線に第1の通常動作用プリチャージ回路および第1の検査用プリチャージ回路の各一端が並列接続されており、

前記SRAMのビット線対の他方のビット線に第2の通常動作用プリチャージ回路および第2の検査用プリチャージ回路の各一端が並列接続されており、

前記第1および第2の通常動作用プリチャージ回路は第1の電源電圧に接続されており、

前記第1および第2の検査用プリチャージ回路は前記第1の電源電圧よりも低い第2の電源電圧に接続されており、

前記ビット線対の一方のビット線に接続された第1の通常動作用プリチャージ回路は第1の活性化信号で活性化され、

前記ビット線対の他方のビット線に接続された第2の通常動作用プリチャージ回路は第2の活性化信号で活性化され、

前記ビット線対の一方のビット線に接続された第1の検査用プリチャージ回路は第3の活性化信号で活性化され、

前記ビット線対の他方のビット線に接続された第2の検査用プリチャージ回路は第4の活性化信号で活性化され、

前記第1乃至第4の各活性化信号は互いに独立に制御され、

該半導体記憶装置の検査時において読出し動作前に、前記第1および第4の活性化信号を活性化するか、または前記第2および第3の活性化信号を活性化することにより、前記ビット線対の一方のビット線と前記ビット線対の他方のビット線とを互いに異なるプリチャージ電位までプリチャージするプリチャージ手段を、備えた、

ことを特徴とする半導体記憶装置。 - 請求項5に記載の半導体記憶装置において、

前記第1および第2の通常動作用プリチャージ回路および前記第1および第2の検査用プリチャージ回路は共にPチャネル型トランジスタからなり、

前記プリチャージ手段は、前記第1および第2の検査用プリチャージ回路のPチャネル型トランジスタと前記第1および第2の通常動作用プリチャージ回路のPチャネル型トランジスタとが駆動能力が等しいトランジスタよりなる、

ことを特徴とする半導体記憶装置。 - SRAMを搭載した半導体記憶装置であって、

前記SRAMのビット線対の一方のビット線に第1の通常動作用プリチャージ回路および第1の検査用プリチャージ回路の各一端が並列接続されており、

前記SRAMのビット線対の他方のビット線に第2の通常動作用プリチャージ回路および第2の検査用プリチャージ回路の各一端が並列接続されており、

前記第1および第2の通常動作用プリチャージ回路および第1および第2の検査用プリチャージ回路は同一の電源電圧に接続されており、

前記ビット線対の一方のビット線に接続された第1の通常動作用プリチャージ回路は第1の活性化信号で活性化され、

前記ビット線対の他方のビット線に接続された第2の通常動作用プリチャージ回路は第2の活性化信号で活性化され、

前記ビット線対の一方のビット線に接続された第1の検査用プリチャージ回路は第1のレベルシフト回路を介して第3の活性化信号で活性化され、

前記ビット線対の他方のビット線に接続された第2の検査用プリチャージ回路は第2のレベルシフト回路を介して第4の活性化信号で活性化され、

前記第1乃至第4の各活性化信号は互いに独立に制御され、

該半導体記憶装置の検査時において読出し動作前に、前記第1および第4の活性化信号を活性化するか、または前記第2および第3の活性化信号を活性化することにより、前記ビット線対の一方のビット線と前記ビット線対の他方のビット線とを互いに異なるプリチャージ電位までプリチャージするプリチャージ手段を、備えた、

ことを特徴とする半導体記憶装置。 - 請求項7に記載の半導体記憶装置において、

前記第1および第2の通常動作用プリチャージ回路および第1および第2の検査用プリチャージ回路は共にPチャネル型トランジスタからなり、

前記プリチャージ手段は、前記第1および第2のレベルシフト回路により前記第1および第2の検査用プリチャージ回路のPチャネル型トランジスタの駆動能力が前記第1および第2の通常動作用プリチャージ回路のPチャネル型トランジスタの駆動能力より小さくなるよう制御する、

ことを特徴とする半導体記憶装置。 - SRAMを搭載した半導体記憶装置であって、

前記SRAMのビット線対の一方および他方のビット線のそれぞれに第1および第2のプリチャージ回路が接続されており、

前記第1および第2のプリチャージ回路は同一の電源電圧に接続されており、

前記ビット線対の一方のビット線に接続された第1のプリチャージ回路は第1のレベルシフト回路を介して第1の活性化信号で活性化され、

前記ビット線対の他方のビット線に接続された第2のプリチャージ回路は第2のレベルシフト回路を介して第2の活性化信号で活性化され、

前記第1および第2の活性化信号は互いに独立に制御され、

前記第1および第2のプリチャージ回路の通常動作モードと検査動作モードとの切替えは前記第1および第2のレベルシフト回路を制御する制御回路によって行なわれ、

該半導体記憶装置の検査時において読出し動作前に、前記第1および第2の活性化信号を活性化することにより、前記ビット線対の一方のビット線と他方のビット線とを互いに異なるプリチャージ電位までプリチャージするプリチャージ手段を、備えた、

ことを特徴とする半導体記憶装置。 - 請求項9に記載の半導体記憶装置において、

前記第1および第2のプリチャージ回路はPチャネル型トランジスタからなり、

前記プリチャージ手段は、前記第1および第2のレベルシフト回路により前記第1および第2のプリチャージ回路の一方のPチャネル型トランジスタの駆動能力が前記第1および第2のプリチャージ回路の他方のPチャネル型トランジスタの駆動能力より小さくなるよう制御する、

ことを特徴とする半導体記憶装置。 - SRAMを搭載した半導体記憶装置であって、

前記SRAMのビット線対の一方および他方のビット線のそれぞれに第1および第2のプリチャージ回路が接続されており、

前記第1および第2のプリチャージ回路は同一の電源電圧に接続されており、

前記ビット線対の一方のビット線に接続された第1のプリチャージ回路は第1の遅延回路を介して第1の活性化信号で活性化され、

前記ビット線対の他方のビット線に接続された第2のプリチャージ回路は第2の遅延回路を介して第2の活性化信号で活性化され、

前記第1および第2の各活性化信号は互いに独立に制御され、

前記第1および第2のプリチャージ回路の通常動作モードと検査動作モードとの切替えは、前記第1および第2の遅延回路を制御する制御回路によって行なわれ、

該半導体装置の検査時において読出し動作前に、前記第1および第2の活性化信号を活性化することにより、前記ビット線対の一方のビット線と他方のビット線とを互いに異なるプリチャージ電位までプリチャージするプリチャージ手段を、備えた、

ことを特徴とする半導体記憶装置。 - 請求項11に記載の半導体記憶装置において、

前記第1および第2のプリチャージ回路はPチャネル型トランジスタからなり、

前記プリチャージ手段は、前記第1および第2の遅延回路により前記第1および第2のプリチャージ回路の一方のPチャネル型トランジスタの立ち上がり動作を前記第1および第2のプリチャージ回路の他方のPチャネル型トランジスタの立ち上がり動作より早めて、前記第1および第2のプリチャージ回路の一方のPチャネル型トランジスタのプリチャージが不十分な状態でプリチャージ動作を完了させる、

ことを特徴とする半導体記憶装置。 - 請求項1に記載の半導体記憶装置において該半導体記憶装置の検査を行う方法であって、

前記第1または第2の通常動作用プリチャージ回路が接続された前記ビット線対の一方のビット線に第1のプリチャージ電位を印加し、前記第1または第2の検査用プリチャージ回路が接続された前記ビット線対の他方のビット線に前記第1のプリチャージ電位より低い第2のプリチャージ電位を印加する第1の工程と、

前記第1の工程の後に読出し動作を行なって動作マージン検査を行う第2の工程と、を有する、

ことを特徴とする半導体記憶装置の検査方法。 - 請求項5に記載の半導体記憶装置において該半導体記憶装置の検査を行う方法であって、

前記第1または第2の通常動作用プリチャージ回路が接続された前記ビット線対の一方のビット線に第1の電源電圧を印加し、前記第1または第2の検査用プリチャージ回路が接続された前記ビット線対の他方のビット線に前記第2の電源電圧を印加する第1の工程と、

前記第1の工程の後に読出し動作を行なって動作マージン検査を行う第2の工程と、を有する、

ことを特徴とする半導体記憶装置の検査方法。 - 請求項7に記載の半導体記憶装置において該半導体記憶装置の検査を行う方法であって、

前記第1または第2の通常動作用プリチャージ回路が接続された前記ビット線対の一方のビット線に電源電圧を印加し、前記第1または第2の検査用プリチャージ回路が接続された前記ビット線対の他方のビット線に前記第1または第2のレベルシフト回路によって前記電源電圧よりも低く設定された電位を印加する第1の工程と、

前記第1の工程の後に読出し動作を行なって動作マージン検査を行う第2の工程と、を有する、

ことを特徴とする半導体記憶装置の検査方法。 - 請求項9に記載の半導体記憶装置において該半導体記憶装置の検査を行う方法であって、

前記第2のプリチャージ回路が接続された前記ビット線対の他方のビット線に電源電圧を印加し、前記第1のプリチャージ回路が接続された前記ビット線対の一方のビット線に前記第1および第2のレベルシフト回路によって前記電源電圧よりも低く設定された電位を印加する第1の工程と、

前記第1の工程の後に読出し動作を行なって動作マージン検査を行う第2の工程と、を有する、

ことを特徴とする半導体記憶装置の検査方法。 - 請求項11に記載の半導体記憶装置において該半導体記憶装置の検査を行う方法であって、

前記第2のプリチャージ回路を第2の遅延回路を介して第2の活性化信号により活性化して、前記第2のプリチャージ回路が接続された前記ビット線対の他方のビット線に電源電圧を印加し、前記第1のプリチャージ回路を第1の遅延回路を介して第1の活性化信号により活性化し、前記第1のプリチャージ回路の立ち上がり動作を前記第1の遅延回路によって前記第2のプリチャージ回路の立ち上がり動作よりも早めて、プリチャージが不十分な状態で該プリチャージ動作を完了して、前記第1のプリチャージ回路が接続された前記ビット線対の一方のビット線に、前記電源電圧よりも低い電位を印加する第1の工程と、

前記第1の工程の後に読出し動作を行なって動作マージン検査を行う第2の工程と、を有する、

ことを特徴とする半導体記憶装置の検査方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005290283A JP2007102902A (ja) | 2005-10-03 | 2005-10-03 | 半導体記憶装置、及びその検査方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005290283A JP2007102902A (ja) | 2005-10-03 | 2005-10-03 | 半導体記憶装置、及びその検査方法 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| JP2007102902A true JP2007102902A (ja) | 2007-04-19 |

Family

ID=38029680

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2005290283A Pending JP2007102902A (ja) | 2005-10-03 | 2005-10-03 | 半導体記憶装置、及びその検査方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP2007102902A (ja) |

Cited By (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| DE102008017813A1 (de) | 2007-04-10 | 2008-10-23 | Toyota Jidosha Kabushiki Kaisha, Toyota-shi | Bremsregelungsvorrichtung und Bremsregelungsverfahren |

| JP2009117026A (ja) * | 2007-11-05 | 2009-05-28 | Sony Computer Entertainment Inc | Sramのビット線スクリーニング方法 |

| JP2010027155A (ja) * | 2008-07-22 | 2010-02-04 | Sanyo Electric Co Ltd | 半導体記憶装置 |

| JP2010061731A (ja) * | 2008-09-03 | 2010-03-18 | Nec Electronics Corp | SRAM(StaticRandomAccessMemory)、及びSRAMのテスト方法 |

| JP2011204295A (ja) * | 2010-03-24 | 2011-10-13 | Renesas Electronics Corp | 半導体記憶装置及びその負荷テスト方法 |

| US8284591B2 (en) | 2009-02-27 | 2012-10-09 | Renesas Electronics Corporation | Semiconductor memory device and test method therefor |

| JP2016085775A (ja) * | 2014-10-27 | 2016-05-19 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

-

2005

- 2005-10-03 JP JP2005290283A patent/JP2007102902A/ja active Pending

Cited By (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| DE102008017813A1 (de) | 2007-04-10 | 2008-10-23 | Toyota Jidosha Kabushiki Kaisha, Toyota-shi | Bremsregelungsvorrichtung und Bremsregelungsverfahren |

| JP2009117026A (ja) * | 2007-11-05 | 2009-05-28 | Sony Computer Entertainment Inc | Sramのビット線スクリーニング方法 |

| JP2010027155A (ja) * | 2008-07-22 | 2010-02-04 | Sanyo Electric Co Ltd | 半導体記憶装置 |

| JP2010061731A (ja) * | 2008-09-03 | 2010-03-18 | Nec Electronics Corp | SRAM(StaticRandomAccessMemory)、及びSRAMのテスト方法 |

| US8284591B2 (en) | 2009-02-27 | 2012-10-09 | Renesas Electronics Corporation | Semiconductor memory device and test method therefor |

| US8737118B2 (en) | 2009-02-27 | 2014-05-27 | Renesas Electronics Corporation | Semiconductor memory device and test method therefor |

| JP2011204295A (ja) * | 2010-03-24 | 2011-10-13 | Renesas Electronics Corp | 半導体記憶装置及びその負荷テスト方法 |

| JP2016085775A (ja) * | 2014-10-27 | 2016-05-19 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| EP0543408B1 (en) | Semiconductor memory and screening test method thereof | |

| KR100334184B1 (ko) | 스태틱램을테스트하는장치및방법 | |

| US5185722A (en) | Semiconductor memory device having a memory test circuit | |

| KR101061080B1 (ko) | Sram 셀과 어레이 테스트 장치 및 방법 | |

| EP2518727A1 (en) | Differential sense amplifier without dedicated precharge transistors | |

| JPH0969300A (ja) | 半導体記憶装置 | |

| US6829183B2 (en) | Active restore weak write test mode | |

| CN101065809B (zh) | 用于检测薄弱单元的sram测试方法和sram测试设备 | |

| JP5032004B2 (ja) | 半導体装置、半導体メモリ及びその読み出し方法 | |

| JP2008027544A (ja) | 半導体記憶装置及びそのテスト方法 | |

| JP2009070474A (ja) | 半導体集積回路 | |

| KR100248645B1 (ko) | 반도체 기억 장치 및 그 테스트 방법 | |

| JP2007102902A (ja) | 半導体記憶装置、及びその検査方法 | |

| JP5587141B2 (ja) | 半導体装置 | |

| US6385103B1 (en) | Semiconductor memory device having a circuit for testing memories | |

| JP2006331511A (ja) | 半導体記憶装置およびその検査手法 | |

| CN108010552B (zh) | 半导体存储装置 | |

| JP5623688B2 (ja) | 半導体記憶装置、および欠陥セルテスト方法 | |

| US8737118B2 (en) | Semiconductor memory device and test method therefor | |

| US7787318B2 (en) | Semiconductor memory device having read operation testing function | |

| US7505339B2 (en) | Static semiconductor memory device allowing simultaneous writing of data into a plurality of memory cells | |

| JP2014099225A (ja) | 半導体装置 | |

| US7286426B2 (en) | Semiconductor memory device | |

| JP4771610B2 (ja) | メモリ回路及びその試験方法 | |

| JP2020123411A (ja) | 半導体記憶装置及びその動作方法 |