JP4354663B2 - 半導体メモリ装置 - Google Patents

半導体メモリ装置 Download PDFInfo

- Publication number

- JP4354663B2 JP4354663B2 JP2001371802A JP2001371802A JP4354663B2 JP 4354663 B2 JP4354663 B2 JP 4354663B2 JP 2001371802 A JP2001371802 A JP 2001371802A JP 2001371802 A JP2001371802 A JP 2001371802A JP 4354663 B2 JP4354663 B2 JP 4354663B2

- Authority

- JP

- Japan

- Prior art keywords

- gate

- potential

- semiconductor layer

- channel body

- word line

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Semiconductor Memories (AREA)

- Thin Film Transistor (AREA)

- Dram (AREA)

Description

【発明の属する技術分野】

この発明は、トランジスタのチャネルボディを記憶ノードとしてダイナミックにデータ記憶を行う半導体メモリ装置に関する。

【0002】

【従来の技術】

従来のDRAMは、MOSトランジスタとキャパシタによりメモリセルが構成されている。DRAMの微細化は、トレンチキャパシタ構造やスタックトキャパシタ構造の採用により大きく進んでいる。現在、単位メモリセルの大きさ(セルサイズ)は、最小加工寸法をFとして、2F×4F=8F2の面積まで縮小されている。つまり、最小加工寸法Fが世代と共に小さくなり、セルサイズを一般にαF2としたとき、係数αも世代と共に小さくなり、F=0.18μmの現在、α=8が実現されている。

【0003】

【発明が解決しようとする課題】

今後も従来と変わらないセルサイズ或いはチップサイズのトレンドを確保するためには、F<0.18μmでは、α<8、更にF<0.13μmでは、α<6を満たすことが要求され、微細加工と共に如何にセルサイズを小さい面積に形成するかが大きな課題になる。そのため、1トランジスタ/1キャパシタのメモリセルを6F2や4F2の大きさにする提案も種々なされている。しかし、トランジスタを縦型にしなければならないといった技術的困難や、隣接メモリセル間の電気的干渉が大きくなるといった問題、更に加工や膜生成等の製造技術上の困難があり、実用化は容易ではない。

【0004】

そこで、この発明は、単純なトランジスタ構造のメモリセルにより、ダイナミックにデータを記憶可能な半導体メモリ装置を提供することを1つの目的としている。

【0005】

【課題を解決するための手段】

本発明に係る半導体メモリ装置は、メモリセルを構成するための複数のMISトランジスタを有する半導体メモリ装置であって、各MISトランジスタは、

半導体層と、

前記半導体層に形成されたソース領域と、

前記半導体層に前記ソース領域と離れて形成されたドレイン領域であって、前記ソース領域と前記ドレイン領域との間の前記半導体層が、フローティング状態のチャネルボディとなる、ドレイン領域と、

前記チャネルボディにチャネルを形成するための第1のゲートと、

前記チャネルボディの電位を容量結合により制御するための第2のゲートと、

前記チャネルボディの前記第2のゲート側に形成された高濃度領域であって、前記チャネルボディと同じ導電型で前記チャネルボディの不純物濃度よりも高い不純物濃度を有する、高濃度領域と、

を備え、

前記MISトランジスタは、前記チャネルボディを第1の電位に設定した第1データ状態と、前記チャネルボディを第2の電位に設定した第2データ状態とをダイナミックに記憶する、

ことを特徴とする。

【0006】

また、本発明に係る半導体メモリ装置は、メモリセルを構成するための複数のMISトランジスタを有する半導体メモリ装置であって、各MISトランジスタは、

半導体層と、

前記半導体層に形成されたソース領域と、

前記半導体層に前記ソース領域と離れて形成されたドレイン領域であって、前記ソース領域と前記ドレイン領域との間の前記半導体層が、フローティング状態のチャネルボディとなる、ドレイン領域と、

前記チャネルボディにチャネルを形成するための第1のゲートと、

を備え、

前記第1のゲートは、前記ソース領域に対する重なり量が正であり、前記ドレイン領域に対する重なり量が負であるように配置して、前記第1のゲートを前記ドレイン領域に対してオフセットさせており、

前記MISトランジスタのドレイン領域がビット線に接続されており、前記MISトランジスタの第1のゲートが第1のワード線に接続されており、前記MISトランジスタのソース領域がソース線に接続されており、

前記ソース領域と前記ドレイン領域は、n型の半導体層で構成されており、前記ソース領域と前記ドレイン領域との間の前記チャネルボディは、p型の半導体層で構成されており、

前記ソース線の電位が0Vに固定された状態で、前記第1のワード線を正の電位にし、前記ビット線を正の電位にすることにより、前記MISトランジスタに前記第1データ状態を書き込み、前記第1のワード線を正の電位にし、前記ビット線を負の電位にすることにより、前記MISトランジスタに前記第2データ状態を書き込む、書き込み手段を、さらに備えることを特徴とする。

【0007】

本発明に係る半導体メモリ装置は、メモリセルを構成するための複数のMISトランジスタを有する半導体メモリ装置であって、各MISトランジスタは、

半導体層と、

前記半導体層に形成されたソース領域と、

前記半導体層に前記ソース領域と離れて形成されたドレイン領域であって、前記ソース領域と前記ドレイン領域との間の前記半導体層が、フローティング状態のチャネルボディとなる、ドレイン領域と、

前記チャネルボディにチャネルを形成するためのゲートと、

を備え、

前記MISトランジスタのドレイン領域がビット線に接続されており、前記MISトランジスタのゲートがワード線に接続されており、前記MISトランジスタのソース領域がソース線に接続されており、

前記ソース領域と前記ドレイン領域は、n型の半導体層で構成されており、前記ソース領域と前記ドレイン領域との間の前記チャネルボディは、p型の半導体層で構成されており、

前記ソース線の電位が0Vに固定された状態で、前記ワード線を負の電位にし、前記ビット線を正の電位にすることにより、前記MISトランジスタに前記第1データ状態を書き込み、前記ワード線を正の電位にし、前記ビット線を負の電位にすることにより、前記MISトランジスタに前記第2データ状態を書き込む、書き込み手段を、さらに備える、

ことを特徴とする。

【0008】

【発明の実施の形態】

以下、図面を参照して、この発明の実施の形態を説明する。

【0009】

[基本コンセプト]

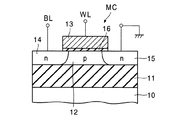

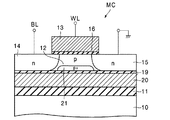

図1は後述する各実施の形態によるDRAMの単位メモリセルMCの基本断面構造を示し、図2はその等価回路を示している。メモリセルMCは、SOI構造のNチャネルMISトランジスタにより構成されている。即ち、シリコン基板10上に絶縁膜としてシリコン酸化膜11が形成され、このシリコン酸化膜11上にp型シリコン層12が形成されたSOI基板が用いられている。この基板のシリコン層12上に、ゲート酸化膜16を介してゲート電極13が形成され、ゲート電極13に自己整合されてn型ソース、ドレイン拡散層14,15が形成されている。

【0010】

ソース、ドレイン14,15は、底部のシリコン酸化膜11に達する深さに形成されている。従って、p型シリコン層12からなるチャネルボディは、チャネル幅方向(図の紙面に直交する方向)の分離を酸化膜で行うとすれば、底面及びチャネル幅方向の側面が他から絶縁分離され、チャネル長方向はpn接合分離されたフローティング状態になる。

【0011】

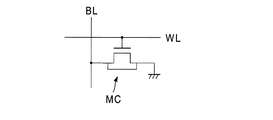

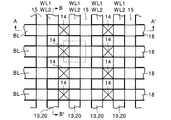

このメモリセルMCをマトリクス配列する場合、ゲート13はワード線WLに接続され、ソース15は固定電位線(接地電位線)に接続され、ドレイン14はビット線BLに接続される。

【0012】

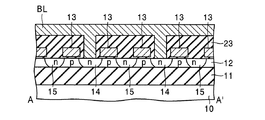

図3は、メモリセルアレイのレイアウトを示し、図4A及び図4Bはそれぞれ図3のA−A’,B−B’断面を示している。p型シリコン層12は、シリコン酸化膜22の埋め込みにより、格子状にパターン形成される。即ちドレインを共有する二つのトランジスタの領域がワード線WL方向にシリコン酸化膜22により素子分離されて配列される。或いはシリコン酸化膜22の埋め込みに代わって、シリコン層12をエッチングすることにより、横方向の素子分離を行っても良い。ゲート13は一方向に連続的に形成されて、これがワード線WLとなる。ソース15は、ワード線WL方向に連続的に形成されて、これが固定電位線(共通ソース線)となる。

【0013】

トランジスタ上は層間絶縁膜23で覆われこの上にビット線BLが形成される。ビット線BLは、二つのトランジスタで共有するドレイン14にコンタクトして、ワード線WLと交差するように配設される。なおソース15の固定電位線(共通ソース線)の配線抵抗を低下させるために、ビット線BLの上又は下に、ワード線WLと平行な金属配線を形成し、これを複数のビツト線毎に固定電位線に接続するようにしてもよい。

【0014】

これにより、各トランジスタのチャネルボディであるシリコン層12は、底面及びチャネル幅方向の側面が酸化膜により互いに分離され、チャネル長方向にはpn接合により互いに分離されてフローティング状態に保たれる。

【0015】

そしてこのメモリセルアレイ構成では、ワード線WLおよびビット線BLを最小加工寸法Fのピッチで形成したとして、単位セル面積は、図3に破線で示したように、2F×2F=4F2となる。

【0016】

このnチャネル型MISトランジスタからなるメモリセルMCの動作原理は、MISトランジスタのチャネルボディ(他から絶縁分離されたp型シリコン層12)の多数キャリアであるホールの蓄積を利用する。即ち、トランジスタを5極管領域で動作させることにより、ドレイン14から大きな電流を流し、ドレイン14の近傍でインパクトイオン化を起こす。このインパクトイオン化により生成される多数キャリアであるホールをp型シリコン層12に保持させ、そのホール蓄積状態を例えばデータ“1”とする。ドレイン14とp型シリコン層12の間のpn接合を順方向バイアスして、p型シリコン層12の過剰ホールをドレイン側に放出した状態をデータ“0”とする。

【0017】

データ“0”,“1”は、チャネルボディの電位の差として、従ってトランジスタのしきい値電圧の差として記憶される。即ち、ホール蓄積によりチャネルボディの電位が高いデータ“1”状態のしきい値電圧Vth1は、データ“0”状態のしきい値電圧Vth0より低い。ボデイに多数キャリアであるホールを蓄積した“1”データ状態を保持するためには、ワード線には負のバイアス電圧を印加することが必要になる。このデータ保持状態は、理論上、リニア領域で読み出し動作を行っている限り、且つ、逆データの書き込み動作(消去)を行わない限り、読み出し動作を行っても変わない。即ち、キャパシタの電荷蓄積を利用する1トランジスタ/1キャパシタのDRAMと異なり、非破壊読み出しが可能である。

【0018】

データ読み出しの方式には、いくつか考えられる。ワード線電位Vwlとチャネルボディ電位VBの関係は、データ“0”,“1”との関係で図5のようになる。従ってデータ読み出しの第1の方法は、ワード線WLにデータ“0”,“1”のしきい値電圧Vth0,Vth1の中間になる読み出し電位を与えて、“0”データのメモリセルでは電流が流れず、“1”データのメモリセルでは電流が流れることを利用する。具体的には例えば、ビット線BLを所定の電位VBLにプリチャージして、その後ワード線WLを駆動する。これにより、図6に示すように、“0”データの場合、ビット線プリチャージ電位VBLの変化がなく、“1”データの場合はプリチャージ電位VBLが低下する。

【0019】

第2の読み出し方式は、ワード線WLを立ち上げてから、ビット線BLに電流を供給して、“0”,“1”の導通度に応じてビット線電位の上昇速度が異なることを利用する。簡単には、ビット線BLを0Vにプリチャージし、図7に示すようにワード線WLを立ち上げて、ビット線電流を供給する。このとき、ビット線の電位上昇の差をダミーセルを利用して検出することにより、データ判別が可能となる。

【0020】

第3の読み出し方式は、ビット線BLを所定の電位にクランプしたときの、“0”,“1”で異なるビット線電流の差を読む方式である。電流差を読み出すには、電流−電圧変換回路が必要であるが、最終的には電位差を差動増幅して、センス出力を出す。

【0021】

この発明において、選択的に“0”データを書き込むためには、即ちメモリセルアレイのなかで選択されたワード線WLとビット線BLの電位により選択されたメモリセルのチャネルボディのみからホールを放出させるには、ワード線WLとチャネルボディの間の容量結合が本質的になる。データ“1”でチャネルボディにホールが蓄積された状態は、ワード線を十分負方向にバイアスして、メモリセルのゲート・チャネルボディ間容量が、ゲート酸化膜容量となる状態(即ち表面に空乏層が形成されていない状態)で保持することが必要である。

【0022】

また、書き込み動作は、“0”,“1”共に、パルス書き込みとして消費電力を減らすことが好ましい。“0”書き込み時、選択トランジスタのチャネルボディからドレインにホール電流が、ドレインからチャネルボディに電子電流が流れるが、チャネルボディにホールが注入されることはない。

【0023】

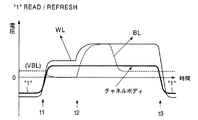

より具体的な動作波形を説明する。図8〜図11は、選択セルによるビット線の放電の有無によりデータ判別を行う第1の読み出し方式を用いた場合のリード/リフレッシュ及びリード/ライトの動作波形である。

【0024】

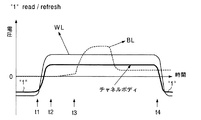

図8及び図9は、それぞれ“1”データ及び“0”データのリード/リフレッシュ動作である。時刻t1までは、データ保持状態(非選択状態)であり、ワード線WLには負電位が与えられている。時刻t1でワード線WLを正の所定電位に立ち上げる。このときワード線電位は、“0”,“1”データのしきい値Vth0,Vth1の間に設定する。これにより、“1”データの場合、予めプリチャージされていたビット線VBLは放電により低電位になる。“0”データの場合はビット線電位VBLは保持される。これにより“1”,“0”データが判別される。

【0025】

そして、時刻t2で、ワード線WLの電位を更に高くし、同時に読み出しデータが“1”の場合には、ビット線BLに正電位を与え(図8)、読み出しデータが“0”の場合はビット線BLに負電位を与える(図9)。これにより、選択メモリセルが“1”データの場合、5極管動作により大きなチャネル電流が流れてインパクトイオン化が起こり、チャネルボディに過剰のホールが注入保持されて再度“1”データが書き込まれる。“0”データの場合には、ドレイン接合が順方向バイアスになり、チャネルボディに過剰ホールが保持されていない“0”データが再度書き込まれる。

【0026】

そして、時刻t3でワード線WLを負方向にバイアスして、リード/リフレッシュ動作を終了する。“1”データ読み出しを行ったメモリセルと同じビット線BLにつながる他の非選択メモリセルでは、ワード線WLが負電位、従ってチャネルボディが負電位に保持されて、インパクトイオン化は起こらない。“0”データ読み出しを行ったメモリセルと同じビット線BLにつながる他の非選択メモリセルでは、やはりワード線WLが負電位に保持されて、ホール放出は起こらない。

【0027】

図10及び図11は、同じ読み出し方式によるそれぞれ“1”データ及び“0”データのリード/ライト動作である。図10及び図11での時刻t1での読み出し動作はそれぞれ、図8及び図9と同様である。読み出し後、時刻t2でワード線WLを更に高電位とし、同じ選択セルに“0”データを書き込む場合には同時に、ビット線BLに負電位を与え(図10)、“1”データを書き込む場合にはビット線BLに正電位を与える(図11)。これにより、“0”データが与えられたセルでは、ドレイン接合が順方向バイアスになり、チャネルボディのホールが放出される。“1”データが与えられたセルでは、ドレイン近傍でインパクトイオン化が起こり、チャネルボディに過剰ホールが注入保持される。

【0028】

図12〜図15は、ビット線BLを0Vにプリチャージし、ワード線選択後にビット線BLに電流を供給して、ビット線BLの電位上昇速度によりデータ判別を行う第2の読み出し方式を用いた場合のリード/リフレッシュ及びリード/ライトの動作波形である。

【0029】

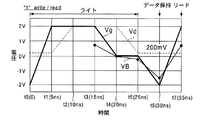

図12及び図13は、それぞれ“1”データ及び“0”データのリード/リフレッシュ動作である。負電位に保持されていたワード線WLを、時刻t1で正電位に立ち上げる。このときワード線電位は、図7に示したように、“0”,“1”データのしきい値Vth0,Vth1のいずれよりも高い値に設定する。或いは・ワード線電位を、第1の読み出し方式と同様に、“0”,“1”データのしきい値Vth0,Vth1の間に設定してもよい。そして、時刻t2でビット線に電流を供給する。これにより、“1”データの場合、メモリセルが深くオンしてビット線BLの電位上昇は小さく(図12)、“0”データの場合メモリセルの電流が小さく(或いは電流が流れず)、ビット線電位は急速に上昇する。これにより“1”,“0”データが判別される。

【0030】

そして、時刻t3で・読み出しデータが“1”の場合には、ビット線BLに正の電位を与え(図12)、読み出しデータが“0”の場合はビット線BLに負の電位を与える(図13)。これにより、選択メモリセルが“1”データの場合、ドレイン電流が流れてインパクトイオン化が起こり、チャネルボディに過剰ホールが注入保持されて再度“1”データが書き込まれる。“0”データの場合には、ドレイン接合が順方向バイアスになり、チャネルボディに過剰ホールのない“0”データが再度書き込まれる。

【0031】

時刻t4でワード線WLを負方向にバイアスして、リード/リフレッシュ動作を終了する。

【0032】

図14及び図15は、同じ読み出し方式によるそれぞれ“1”データ及び“0”データのリード/ライト動作である。図14及び図15での時刻t1及びt2での読み出し動作はそれぞれ、図12及び図13と同様である。読み出し後、同じ選択セルに“0”データを書き込む場合には、ビット線BLに負電位を与え(図14)、“1”データを書き込む場合にはビット線BLに正電位を与える(図15)。これにより、“0”データが与えられたセルでは、ドレイン接合が順方向バイアスになり、チャネルボディの過剰ホールが放出される。“1”データが与えられたセルでは、大きなドレイン電流が流れてドレイン近傍でインパクトイオン化が起こり、チャネルボディに過剰ホールが注入保持される。

【0033】

以上のようにこの発明によるメモリセルMCは、他から電気的に分離されたフローティングのチャネルボディを持つ単純なMISトランジスタにより構成され、4F2のセルサイズが実現可能である。また、フローティングのチャネルボディの電位制御は、ゲート電極からの容量結合を利用しており、ソースも固定電位である。即ち、読み出し/書き込みの制御は、ワード線WLとビット線BLで行われ、簡単である。更にメモリセルMCは基本的に非破壊読み出しであるので、センスアンプをビット線毎に設ける必要がなく、センスアンプのレイアウトは容易になる。更に電流読み出し方式であるので、ノイズにも強く、例えばオープンビット線方式でも読み出しが可能である。また、メモリセルの製造プロセスも簡単である。

【0034】

また、SOI構造は、今後のロジックLSIの性能向上を考えたときに重要な技術となる。この発明によるDRAMは、この様なSOI構造のロジックLSIとの混載を行う場合にも非常に有望である。キャパシタを用いる従来のDRAMと異なり、ロジックLSIのプロセスと異なるプロセスを必要とせず、製造工程が簡単になるからである。

【0035】

更に、この発明によるSOI構造のDRAMは、従来の1トランジスタ/1キャパシタ型のDRAMをSOI構造とした場合に比べて、優れた記憶保持特性が得られるという利点がある。即ち従来の1トランジスタ/1キャパシタ型のDRAMをSOI構造とすると、フローティングのチャネルボディにホールが蓄積されてトランジスタのしきい値が下がり、トランジスタのサブスレッショルド電流が増加する。これは記憶保持特性を劣化させる。これに対してこの発明による1トランジスタのみのメモリセルでは、記憶電荷を減少させるトランジスタパスは存在せず、データ保持特性は純粋にpn接合のリークのみで決まり、サブスレッショルドリークという問題がなくなる。

【0036】

ここまでに説明した基本的なメモリセルにおいて、チャネルボディの電位の差として記憶されるデータ“0”,“1”のしきい値電圧差をどれだけ大きくとれるかがメモリ特性にとって重要になる。この点に関してシミュレーションを行った結果によると、ゲートからの容量結合によるチャネルボディの電位制御を伴うデータ書き込みに際して、書き込み直後の“0”,“1”データのチャネルボデイ電位差に比べて、その後のデータ保持状態での“0”,“1”データのチャネルボディ電位差が小さくなることが明らかになった。そのシミュレーション結果を次に説明する。

【0037】

デバイス条件は、ゲート長Lg=0.35μm、p型シリコン層12は厚さがtSi=100nm、アクセプタ濃度がNA=5×1017/cm3であり、ソース14及びドレイン15のドナー濃度がND=5×1020/cm3、ゲート酸化膜厚がtox=10nmである。

【0038】

図16は、“0”データ書き込みと、その後のデータ保持及びデータ読み出し(それぞれ瞬時で示している)におけるゲート電位Vg、ドレイン電位Vd、及びチャネルボディの電位VBを示している。図17は同じく、“1”データ書き込みと、その後のデータ保持及びデータ読み出し(それぞれ瞬時で示している)におけるゲート電圧Vg、ドレイン電圧Vd、及びチャネルボディ電圧VBを示している。

【0039】

また、時刻t6−t7のデータ読み出し動作における“0”データのしきい値電圧Vth0と“1”データのしきい値電圧Vth1を見るために、その時間のドレイン電流Idsとゲート・ソース間電圧Vgsを描くと、図18のようになる。但し、チャネル幅Wとチャネル長LをW/L=0.175μm/0.35μmとし、ドレイン・ソース間電圧をVds=0.2Vとしている。

【0040】

図18から、“0”書き込みセルのしきい値電圧Vth0と“1”書き込みセルのしきい値電圧Vth1の差ΔVthは、ΔVth=0.32Vとなっている。以上の解析結果から、問題になるのは、図16及び図17において、“0”書き込み直後(時刻t3)のチャネルボディ電位がVB=−0.77V、“1”書き込み直後のチャネルボディ電位がVB=0.85Vであり、その差が1.62Vであるのに対し、データ保持状態(時刻t6)では、“0”書き込みセルのチャネルボディ電位がVB=−2.04V、“1”書き込みセルのボデイ電位がVB=−1.6Vであり、その差が0.44Vと書き込み直後より小さくなっていることである。

【0041】

このように書き込み直後に比べて、その後のデータ保持状態でのチャネルボディ電位のデータによる差が小さくなる要因は、二つ考えられる。

【0042】

その一つは、ゲートからチャネルボディヘの容量カップリングがデータにより異なることである。“0”書き込み直後(t3−t4)では、ドレインは−1.5Vであるが、“1”書き込み直後ではドレインが2Vである。従って、その後ゲート電位Vgを下げたとき、“1”書き込みセルではチャネルが容易に消失し、ゲート・チャネルボディ間の容量が顕在化して、次第にチャネルボディにホールが蓄積されて容量が大きくなる。一方、“0”書き込みセルではチャネルが容易には消失せず、ゲート・チャネルボディ間容量が顕在化しない。

【0043】

ゲート電位を下げ始めるより先にドレイン電位を200mVにリセットすれば、上述したアンバランスは解消されるかに思われる。しかしこの場合には、“0”書き込みを行ったセルでは、チャネルが形成された状態でドレイン電位が上昇して3極管動作による電流が流れる。そして、“0”書き込みにより折角下げたチャネルボディ電位が、n型のドレイン及びチャネル反転層とp型のチャネルボディとの間の容量結合により上昇してしまい、好ましくない。

【0044】

もう一つは、書き込み後の時刻t4−t5の間で、ソース或いはドレインとチャネルボディとの間のpn接合の容量でチャネルボディ電位が影響され、これが“0”,“1”データの信号量を減らす方向に作用することである。

【0045】

そこで、上記基本メモリセルに対して、チャネル形成の制御を行うためのゲート(第1のゲート)とは別に、チャネルボディを容量結合により電位制御するためのゲート(第2のゲート)を付加する。第2のゲートとチャネルボディとの間の容量を確保するために、第2のゲート側の表面には、チャネル反転層が形成されることなく、蓄積状態(アキュミュレーション状態)を保つように、チャネルボディと同じ導電型の高濃度領域を形成する。そして、第2のゲートは、例えば第1のゲートより低い電位で、或いは同じ電位で第1のゲートと同期して駆動する。或いはまた第2のゲートは例えば、ソースに与えられる基準電位或いはそれより低い電位(nチャネルの場合であれば、負電位)に固定してもよい。

【0046】

以下に具体的な実施の形態を説明する。

【0047】

[実施の形態1]

図19Aは、この発明の実施の形態1によるメモリセルMCの構造を、図1に対応させて示している。基本構造は、図1と同様であり、図1と異なる点は、チャネル制御を行う第1のゲート13とは別に、シリコン層12にゲート絶縁膜19を介して対向して容量結合する第2のゲート20が酸化膜11に埋め込まれている点、及びシリコン層12の第2のゲート20側の表面には、チャネル反転層が形成されない程度の高濃度のp+型層21を形成している点である。すなわち、シリコン層12には、このシリコン層12と同じ導電型で、且つ、シリコン層12の不純物濃度よりも高い不純物濃度を有する、p+型層21が形成されている。このp+型層21が存在することにより、第1のゲート13と第2のゲート20に正の電位を印加して書き込みを行う場合でも、第1のゲート13側のチャネルボディにはチャネルが形成されるが、第2のゲート20側のチャネルボディにはチャネルが形成されにようになる。

【0048】

なお、この実施の形態のメモリセルMCにおいては、ゲート絶縁膜19は、第1のゲート13側のゲート絶縁膜16と同じ膜厚としている。

【0049】

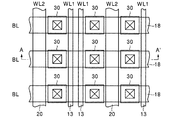

実際のメモリセルアレイ構成では、図19Aに示すメモリセルMCが複数個マトリクス配列され、第1のゲート13は第1のワード線WL1として連続的に形成され、第2のゲート20はこれと並行する第2のワード線WL2として配設される。

【0050】

図19Bは、この様なメモリセルMCを複数、マトリクス配列したメモリセルアレイの等価回路を示している。一方向に並ぶ複数のメモリセルMCの第1のゲート(G1)13は、第1のワード線WL1に接続され、第2のゲート(G2)20は、第2のワード線WL2に接続される。これらのワード線WL1,WL2と交差する方向に、メモリセルMCのドレインが接続されるビット線BLが配設される。全メモリセルMCのソース15は固定電位線(接地電位線VSS)に接続される。

【0051】

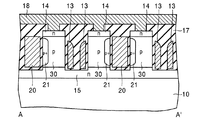

図19Cは、メモリセルアレイのレイアウトを示し、図19D、図19Eはそれぞれ図19CのA−A’,B−B’線断面を示している。p型シリコン層12は、シリコン酸化膜22の埋め込みにより、格子状にパターン形成される。即ちドレイン14を共有する二つのトランジスタの領域がワード線WL1,WL2の方向にシリコン酸化膜22により素子分離されて配列される。或いはシリコン酸化膜22の埋め込みに代わって、シリコン層12をエッチングすることにより、横方向の素子分離を行っても良い。第1のゲート13及び第2のゲート20は、一方向に連続的に形成されて、これらがワード線WL1及びWL2となる。ソース15は、ワード線WL1,WL2の方向に連続的に形成されて、これが固定電位線(共通ソース線)となる。トランジスタ上は層間絶縁膜17で覆われこの上にビット線(BL)18が形成される。ビット線18は、二つのトランジスタで共有するドレイン14にコンタクトして、ワード線WL1,WL2と交差するように配設される。

【0052】

これにより、各トランジスタのチャネルボディであるシリコン層12は、底面及びチャネル幅方向の側面が酸化膜により互いに分離され、チャネル長方向にはpn接合により互いに分離されて、フローティング状態に保たれる。

【0053】

そしてこのメモリセルアレイ構成では、ワード線WL1,WL2およびビット線BLを最小加工寸法Fのピッチで形成したとして、単位セル面積は、図19Cに破線で示したように、2F×2F=4F2となる。

【0054】

この様な構成として、先に基本メモリセルを用いて説明したと同様の動作を行う。このとき、第2のワード線WL2は、第1のワード線WL1と同期して、第1のワード線WL1より低い電位で駆動するものする。この様に、第2のゲート20を第1のゲート13と共に駆動することにより、しきい値電圧差の大きい“0”,“1”データ書き込みができる。即ち、第2のゲート20をデータ保持状態では負電位にして、“1”データの蓄積状態を良好に保持しながら、データ書き込み時にその電位を上昇させることにより、容量結合によりチャネルボディ電位を上昇させて、データ書き込みを確実にすることができる。

【0055】

すなわち、“0”データ書き込みの場合に、第1のゲート13に正の電位を印加するが、そうすると、チャネルボディの第1のゲート13側にチャネル反転層が形成される。しかし、チャネル反転層が形成されると、このチャネル反転層が阻害要因となり、第1のゲート13によるチャネルボディへの容量結合が弱くなる。このため、第1のゲート13に正の電位を印加してもチャネルボディの電位を十分に上昇させることができなくなってしまう。

【0056】

しかし、この実施の形態では、第2のゲート20にも正の電位を印加することにより、チャネルボディの電位を十分に上昇させることができる。なぜなら、p+型層21が形成されているため、チャネルボディの第2のゲート20側にはチャネル反転層が形成されず、したがって、第2のゲート20に正の電位を印加することにより、容量結合でチャネルボディの電位を十分に上昇させることができるのである。このため、的確な“0”データ書き込みが可能である。

【0057】

また、非選択の第1のワード線WL1の電位を下げることでデータ保持を行うが、このとき対をなす第2のワード線WL2の電位も下げてチャネルボディ電位を低く制御することにより、同じビット線に接続された他のセルで“0”データ書き込みを行う場合に、“1”データを保持する非選択セルでのデータ破壊が確実に防止される。更に、“1”書き込みビット線に接続される非選択の“0”データセルでは、表面ブレークダウンやGIDL電流によるデータ破壊の懸念があるが、この実施の形態の場合、第2のワード線によりチャネルボディ電位を下げることで、これらの懸念も解消される。

【0058】

更に、“0”書き込み時、ビット線の電位を大きく下げると、ソースからビット線に電流が流れるが、この実施の形態の場合、第2のゲート20によりチャネルボディ電位を上昇せしめるため、ビット線電位をそれほど下げる必要がない。例えばビット線電位をソースの基準電位と同じ程度として、ソースからビット線に流れる電流を抑制することが可能である。

【0059】

またデータ読み出し時は、誤まって“1”書き込みにならないように、3極管動作させることが必要である。このため、ビット線電位は“1”書き込み時より低いが、このためドレインとチャネルボディ間の空乏層の伸びは、“1”書き込み時より小さく、従ってビット線とチャネルボディの容量結合が大きくなる。このことは、書き込み時にチャネルボディに注入されたキャリアが容量再分配されて、チャネルボディ電位の低下の原因となる。この実施の形態においては、第2のゲート20による制御によって、チャネルボディの多数キャリア蓄積状態を良好に保持することができる。

【0060】

なお、上の説明では、第1のゲート13に対して第2のゲート20を低い電位で駆動するようにしたが、第2のゲート20側のチャネルボディ表面にはp+型層21を形成しているため、第2のゲート20を第1のゲート13と同じ電位で駆動してもチャネル反転層が形成されることはなく、チャネルボディに対して大きな容量結合で電位制御することができる。

【0061】

また、第1のゲート13側のゲート絶縁膜16と第2のゲート20側のゲート絶縁膜19は、厚みが同じでなくてもよく、必要とする容量結合の大きさに応じてそれぞれ最適設定することができる。

【0062】

また、この実施の形態では、第1のゲート13と第2のゲート20をシリコン層の上下面に対向させたが、同じ面に対向させるようにしてもよい。具体的には、第1のゲートと第2のゲートを一体として配設し、チャネル領域の一部にチャネル反転層の形成を防止する高濃度領域を形成することにより、上記実施の形態と同様の動作が可能になる。第1のゲートと第2のゲートをシリコン層の同じ面に別々に配置することもできる。

【0063】

図19Fは、第1のゲート13と第2のゲート20を一体にしたメモリセルMCの構成を示す斜視図であり、図19Gは、図19FのA−A’断面を示しており、図19Hは、図19FのB−B’断面を示している。

【0064】

これらの図から分かるように、この例では、第2のゲート20は形成されておらず、第1のゲート13が第2のゲート20と同様の役割を果たすようにしている。このために、シリコン層12の表面側半分の領域に、高濃度のp+型層21が形成されている。すなわち、この例では、シリコン層12が不純物濃度の低いp−型の領域として形成されており、p+型層21がこれよりも不純物濃度が高いp+型の領域として形成されている。

【0065】

p+型層21は、その平面視において、シリコン層12のおよそ半分の領域に形成されている。p+型層21の深さは、ゲート絶縁膜16と酸化膜11との間の位置まで形成されている。あるいは、酸化膜11まで届いても構わない。このp+型層21を形成する大きさは任意であり、第1のゲート13を駆動した場合にチャネル反転層が形成されないようにして、チャネルボディに対して大きな容量結合で電位制御できればよい。

【0066】

図19Iは、図19Fに示したメモリセルMCをマトリクス状に配置したメモリセルアレイのレイアウトを示す図であり、図19Cに対応する図である。図19Jは、図19IのA−A’断面を示す図であり、図19Kは、図19IのB−B’断面を示す図であり、図19Lは、図19IのC−C’断面を示す図である。

【0067】

これらの図から分かるように、ゲート13は一方向に連続的に形成されて、1つのワード線WLとなる。但し、この例では、上述した第2のゲート20が存在しないので、第2のワード線WL2は形成されていない。ビット線18は、二つのトランジスタで共有するドレイン14にコンタクトして、ワード線WLと交差するように配設される。そして、ドレイン14及びソース15の間のチャネルボディにおけるワード線WL側の一部に、p+型層21が形成される。

【0068】

なお、このメモリセルMCにおいては、図19Hに示すように、p+型層21は、そのB−B’断面方向において、ドレイン領域14とソース領域15に接するように形成されている。但し、必ずしもp+型層21は、ドレイン領域14とソース領域15に接していなくともよい。

【0069】

そのような例を、図19M及び図19Nに示す。図19Mは、メモリセルMCの構成を示す斜視図であり、図19Fに対応する図である。図19Nは、図19MにおけるB−B’断面を示す図であり、図19Hに対応する図である。図19MにおけるA−A’断面は、先に示した図19Gと同様である。

【0070】

これら図19M及び図19Nに示すように、p+型層21は、ドレイン領域14とソース領域15と接していない。このようにすることにより、このメモリセルMCのリテンション時間が短くなってしまうのを、回避することができる。より詳しく説明すると、p+型層21とn型のドレイン領域14とソース領域15とが直接的に接すると、pn接合に逆バイアスが印加された場合の空乏層の延びが小さくなってしまう。すると、電界の強さが大きくなり、pn接合部分のリーク電流が増加してしまい、メモリセルMCがデータを保持することのできる時間であるリテンション時間が短くなってしまうのである。

【0071】

これに対して、図19M及び図19Nに示すように、p+型層21をドレイン領域14とソース領域15と接しないように形成することにより、このような事態を回避することができる。つまり、p+型層21がドレイン領域14とソース領域15と接する場合と比べて、メモリセルMCのリテンション時間を長くすることができるのである。

【0072】

[実施の形態2]

図20は、実施の形態2によるメモリセルMCの構造である。図19Aの実施の形態と異なりこの実施の形態では、第2のゲート20は、配線としてパターニングされず、セルアレイ領域全体をカバーするように共通のゲート(バックプレート)として配設される。すなわち、第2のゲート20は、このメモリセルアレイ内にあるすべてのMISトランジスタに共通に設けられている。この様な構造とすれば、第2のゲート20と第1のゲート13の位置合わせが不要であり、製造プロセスが簡単になる。

【0073】

この様な構成として、第2のゲート20を例えばソース電位或いはそれより低い電位に固定して、先の基本メモリセルで説明したと同様の動作を行う。この場合にも、第1のゲート13(ワード線WL)の振幅を大きくすることにより、“0”,“1”データの信号差を大きくすることができる。即ち、第2のゲート20を固定電位でチャネルボディに容量結合させると、第1のゲート13からのチャネルボディに対する容量結合は基本メモリセルの場合に比べて容量分割により小さくなる。しかしその分、第1のゲート13の駆動振幅を上げることによって、第1のゲート13によるチャネルボディの電位を、“0”,“1”データについて大きな差のない状態で制御することができ、データ保持状態で“0”,“1”データのしきい値電圧差を大きくすることが可能になる。

【0074】

[実施の形態3]

図21は、実施の形態3によるメモリセルアレイのレイアウトを示し、図22はそのA−A’断面を示している。ここまでの実施の形態では、フローティングのチャネルボディを持つトランジスタを作るためにSOI基板を用いたのに対し、この実施の形態では、いわゆるSGT(Surrounding Gate Transistor)構造を利用して、フローティングのチャネルボディを持つ縦型MISトランジスタによりメモリセルを構成する。

【0075】

シリコン基板10には、RIEにより、縦横に走る溝を加工して、p型柱状シリコン30が配列形成される。これらの各柱状シリコン30の両側面に対向するように、第1のゲート13と第2のゲート20が形成される。第1のゲート13と第2のゲート20は、図22の断面において、柱状シリコン30の間に交互に埋め込まれる。第1のゲート13は、側壁残しの技術により、隣接する柱状シリコン30の間で隣接する柱状シリコン30に対して独立したゲート電極として分離形成される。一方第2のゲート20は、隣接する柱状シリコン30の間にこれらが共有するように埋め込まれる。第1,第2のゲート13,20はそれぞれ、第1,第2のワード線WL1,WL2として連続的にパターン形成される。

【0076】

柱状シリコン30の上面にn型ドレイン拡散層14が形成され、下部には全セルで共有されるn型ソース拡散層15が形成される。また柱状シリコン層30の第2のゲート20側の側面には、p+型層21が形成される。これにより、各チャネルボディがフローティングである縦型トランジスタからなるメモリセルMCが構成される。ゲート13,20が埋め込まれた基板には層間絶縁膜17が形成され、この上にビット線18が配設される。

【0077】

この実施の形態によっても、先の各実施の形態と同様の動作ができる。この実施の形態によれば、SOI基板を用いる必要がなく、従ってメモリセルのみ縦型トランジスタによるフローティングのチャネルボディを持たせ、セルアレイ以外のセンスアンプ、トランスファゲート、ロウ/カラムデコーダ等の周辺回路は通常の平面型トランジスタを用いることができる。このため、SOI基板を用いた場合のように、チャネルボディ浮遊効果による回路の不安定性がなくすために周辺回路トランジスタのチャネルボディ電位を固定するためのコンタクトを形成するという必要がなく、それだけ周辺回路部の面積縮小が可能になる。

【0078】

[実施の形態4]

図23及び図24は、実施の形態3と同様のSGT構造を用いた実施の形態のセルアレイのレイアウトとそのA−A’断面を、図21及び図22に対応させて示している。実施の形態3との相違は、ゲート13と20とが一体に柱状シリコン層30の周囲を取り巻いて、共通のワード線WLとして配設されていることである。柱状シリコン層30のゲート20が対向する側面には、実施の形態3と同様に、p+型層21が形成されている。

【0079】

この実施の形態の場合、ゲート13,20は、ワード線WLとして一体に同電位で駆動されることになる。ゲート20側はp+型層21があるためにチャネル反転層が形成されることはなく、従ってワード線WLは大きな容量でチャネルボディに結合して、その電位を制御することができる。このp+型層21が形成される面は、柱状シリコン層30の1つの面に限られるものではなく、2つの面、3つの面に形成するようにしてもよい。つまり、p+型層21は、柱状シリコン層30の一つ以上の面に形成されていればよい。

【0080】

[実施の形態5]

図25Aは、“0”データ書き込みの信頼性の改善を可能とした実施の形態のメモリセルMCの構造を、図1に対応させて示す。この実施の形態のメモリセル構造が図1と異なる点は、ゲート13がドレイン14に対してオフセットを持つようにしていることである。すなわち、チャネルボディ側のソース15上には、ゲート絶縁膜16を介して、ゲート13が形成されている。つまり、ゲート13のソース15に対する重なり量は正である。これに対して、ドレイン14上には、ゲート13が形成されていない。つまり、ゲート13のドレイン14に対する重なり量は負である。

【0081】

これは、図25Aに示したように、ドレイン14及びソース15のイオン注入を斜めイオン注入とすることにより、容易に実現することができる。或いは斜めイオン注入によらず、ドレイン側のゲート側壁にのみ側壁絶縁膜を形成した状態で通常のイオン注入を行うことによっても、同様のオフセット構造を得ることができる。その他は、図1と変わらない。

【0082】

上述した実施の形態におけるメモリセルでは、“0”書き込みは、ドレイン領域14とチャネルボデイの間に順バイアスを与えて、チャネルボディの多数キャリアをドレイン領域14に放出させる。この場合、図1に示した通常のトランジスタ構造では、チャネル反転層が形成されてこれがゲート13とチャネルボディの間のシールド層となり、チャネル反転層とチャネルボディとの間の容量結合が大きくなる。この結果、ドレイン領域14を負電位から0Vに戻すときに、チャネル反転層とチャネルボディの容量結合によりチャネルボディ電位が上昇し、十分に“0”書き込みができなくなる可能性がある。また、チャネル反転層のためにゲート13とチャネルボディの間の容量が小さくなるため、ビット線の影響をより大きく受けやすくなる。更にチャネル反転層が形成されると、チャネル電流(nチャネルの場合電子電流)が流れる。このチャネル電流は、書き込み動作には無用の電流であり、書き込み電力の増大を招くだけでなく、もしインパクトイオン化が生じれば、“1”書き込みモードとなり、“0”書き込みの信頼性が低下する。

【0083】

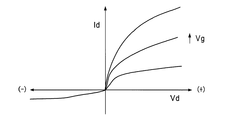

これに対して、図25Aに示すように、ドレイン側にオフセット構造を持たせると、ドレイン領域14に正電位が与えられてドレイン接合が逆バイアスとなる通常のトランジスタ動作の場合は、図25Bに示すように、ドレイン領域14から拡がる空乏層DLがゲート13直下まで延びる。このため、ゲート13に正の電圧を印加することにより、ドレイン領域14からの空乏層DLとソース領域15との間にチャネル反転層CHが形成され、ドレイン領域14とソース領域15との間にチャネル電流が流れる状態になる。つまり、図25Aに示すメモリセルMCは、図26に示すように、MISトランジスタとして、正常動作する。この図26は、ドレイン領域14に印加される電圧Vdと、ソース/ドレイン間を流れる電流Idとの関係を示すグラフを示している。そして、ゲート13に印加される電圧Vgを変化させた場合の特性を示している。

【0084】

しかし、ドレイン領域14に負電位が与えられた場合には、トランジスタ動作としてはドレイン,ソースの機能が逆となり、図25Cに示すように、空乏層DLはソース領域15側に形成されるとともに、チャネル反転層CHがソース領域14から離れて形成される。このため、図26に示すように、ドレイン領域14とソース領域15との間にチャネル電流が殆ど流れない。

【0085】

従ってこの実施の形態によると、“0”書き込み時(つまり、図25Cに示すように、ドレイン領域14とチャネルボディとの間に順バイアスを与えた時)、ドレイン領域14とチャネルボディとの無用な容量結合によるチャネルボディ電位の上昇が抑えられ、“0”書き込みマージンを上げることができる。また“0”書き込み時に無用なチャネル電流を抑えて、ビット線BLに流れる書き込み電流を低減し、書き込み電力を低減することができる。

【0086】

上では、逆方向について殆ど電流が流れない場合について述べたが、チャネル電流に10%以上の差がつく軽い非対称性を持たせることで、同様に電流低減等の効果が得られる。また、ドレイン領域14側にオフセットを持たせるのは、ソース、ドレイン逆転時のチャネル電流を非対称とする手段の一つであり、ソース、ドレインの順逆時のチャネル電流に非対称を与えるために他の手法を用いることもできる。すなわち、MISトランジスタが、ソース領域15からドレイン領域14へチャネル電流が流れる場合と、ドレイン領域14からソース領域15へチャネル電流が流れる場合とで、同じ電位をゲート13に与えた場合でも異なる特性を有するようにすればよい。

【0087】

[実施の形態6]

図27及び図28はそれぞれ、図19A及び図20のメモリセルMCについて、同様にゲートオフセット構造を導入した実施の形態を示している。この実施の形態によっても同様に、“0”書き込み時の無用な電流を低減することができる。

【0088】

図29A及び図29Bは、SGT構造を用いたメモリセルMCについて、同様にゲートオフセット構造を導入した実施の形態を示している。図29Aは、そのようなメモリセルMCにより構成されたメモリセルアレイのレイアウトを示す平面図であり、図29Bは、図29AのA−A’断面を示す図である。これら図29A及び図29Bに示すように、ゲート13は柱状シリコン層30を取り巻く一体のものである。また、柱状シリコン30には、p+型層21の高濃度領域は形成されていない。

【0089】

図29Bに示すように、柱状シリコン層30におけるチャネルボディ側のソース15の周囲には、ゲート絶縁膜を介して、ゲート13が形成されている。つまり、ゲート13のソース15に対する重なり量は正である。これに対して、柱状シリコン層30におけるドレイン14の周囲には、ゲート13が形成されていない。つまり、ゲート13のドレイン14に対する重なり量は負である。

【0090】

図30Aは、図21及び図22の実施の形態3において、ゲートオフセット構造を導入したメモリセルで構成されたメモリセルアレイのレイアウトを示す平面図である。図30Bは、図30AにおけるA−A’断面を示す図である。これら図30A及び図30Bに示すように、第1のゲート13は、ソース領域15側にシフトして形成されている。すなわち、柱状シリコン層30におけるソース15の側面には、ゲート絶縁膜を介して、第1のゲート13が形成されている。つまり、第1のゲート13のソース15に対する重なり量は正である。これに対して、柱状シリコン層30におけるドレイン14の側面には、第1のゲート13が形成されていない。つまり、第1のゲート13のドレイン14に対する重なり量は負である。それ以外の構成は、上述した実施の形態3と同様であり、第1のゲート13と第2のゲート20は、別々のワード線として配設されている。

【0091】

図30Cは、図23及び図24の実施の形態4において、ゲートオフセット構造を導入したメモリセルにより構成されたメモリセルアレイのレイアウトを示す平面図である。図30Dは、図30CにおけるA−A’断面を示す図である。これら図30C及び図30Dに示すように、第1のゲート13は、ソース領域15側にシフトして形成されている。すなわち、柱状シリコン層30におけるソース15の側面には、ゲート絶縁膜を介して、第1のゲート13が形成されている。つまり、第1のゲート13のソース15に対する重なり量は正である。これに対して、柱状シリコン層30におけるドレイン14の側面には、第1のゲート13が形成されていない。つまり、第1のゲート13のドレイン14に対する重なり量は負である。それ以外の構成は、上述した実施の形態4と同様であり、第1のゲート13と第2のゲート20は、共通のワード線として配設されている。

【0092】

この実施の形態6によっても同様に、“0”書き込み時の無用な電流をなくすことができる。

【0093】

[実施の形態7]

ここまでの実施の形態では、“1”書き込みにはドレイン接合近傍でのインパクトイオン化による基板電流を利用したが、インパクトイオン化に代わり、ゲートにより誘起されるドレインリーク電流、いわゆるGIDL電流を利用することもできる。図31は、ゲート長/ゲート幅=0.175μm/10μmのMISFETでのゲート電圧−ドレイン電流特性を示している。ゲート長が短くなると、図示のようにゲート電圧Vgが負の領域で正のドレイン電圧Vdがかかると、大きな基板電流が流れる。これが、GIDL電流であり、これを利用することで“1”書き込みが可能である。

【0094】

図32は、GIDL電流を利用した“1”書き込み/読み出しの動作波形を示している。インパクトイオン化を利用する場合と異なり、“1”書き込み時、ゲート電圧Vgを負、ドレイン電圧Vdを正にする。これにより、GIDL電流により、チャネルボディにホールを注入蓄積することができる。

【0095】

なおGIDL電流を利用する“1”書き込み方式は、図1に示した基本メモリセル構造はもちろん、図19A以下に示した各実施の形態のメモリセル構造の場合にも同様に適用が可能である。

【0096】

[実施の形態8]

図33、図34A及び図34Bは、シリコン層12を絶縁膜11上で凸型のストライプ状に形成した実施の形態である。図33は、そのようなメモリセルによるメモリセルアレイのレイアウトを示す平面図であり、図34Aは図33におけるA−A’断面を示す図であり、図34Bは図33におけるB−B’断面を示す図である。

【0097】

この場合、ゲート13は、上記各実施の形態の第1のゲートと第2のゲートを一体に形成したものということができ、凸型シリコン層12の上面と両側面に対向させる。具体的にこの構造は、素子分離絶縁膜24の埋め込み時に、シリコン層12が突出した状態に埋め込むことにより、得られる。そして、シリコン層12のゲート13が対向する3面のうち、例えば両側面にp+型層21を形成して、ここをチャネル反転層が形成されない容量結合部とする。なお、p+型層21は、シリコン層12の上面及び両側面からなる3つの面のうち、一つ以上の面に形成されていればよい。

【0098】

これにより、先の各実施の形態と同様の動作ができる。

【0099】

[実施の形態9]

上述した各実施の形態によれば、一つのMISトランジスタを1ビットのメモリセルMCとして、ダイナミック記憶ができるメモリセルアレイが構成される。そして、上述したように、第1のゲート13と第2のゲート20とを別々に形成した場合、第1のワード線WL1と第2のワード線WL2は異なる電位で同期駆動してもよいし、同じ電位で同期駆動してもよい。

【0100】

図35A及び図35Bは、データ書き込み時のワード線WL1,WL2及びビット線BLの電圧波形を示している。対をなす第1のワード線WL1と第2のワード線WL2は同期して駆動する。図35Aは、第1のゲート13と第2のゲート20とを別々に形成した場合に、第2のゲート20を第1のゲート13より低い電位で制御して、チャネルボディの第2のゲート20側に多数キャリア蓄積を可能とするものである。一方、図35Bは、第1のゲート13と第2のゲート20を同じ電位で駆動して、チャネルボディの第2のゲート20側に多数キャリア蓄積を可能とするものである。この図35Bの電圧波形は、第1のゲート13と第2のゲート20とを共通に形成した場合にも、同様に適用される。

【0101】

図35Aの場合、“1”データ書き込み時、選択された第1のワード線WL1に基準電位VSSより高い正の電位VWL1Hを与え、同時に選択された第2のワード線WL2にはそれより低い電位VWL2H(図の例では基準電位VSSより高い正電位)を与え、選択されたビット線BLには、基準電位VSSより高い正の電位VBLHを与える。これにより、選択されたメモリセルMCにおいて、5極管動作によるインパクトイオン化が生じ、ホールがチャネルボディに蓄積される。

【0102】

データ保持は、第1のワード線WL1に基準電位VSSより低い負の電位VWL1Lを与え、第2のワード線WL2にはそれより更に低い電位VWL2Lを与える。これにより、チャネルボディに過剰ホールを蓄積した状態である“1”データを保持する。

【0103】

“0”データ書き込み時は、選択された第1及び第2のワード線WL1及びWL2にそれぞれ“1”書き込み時と同様の電位VWL1H及びVWL2Hを与え、選択されたビット線BLには基準電位VSSより低い負の電位VBLLを与える。これにより、選択されたメモリセルMCにおいて、ドレイン接合が順バイアスになり、チャネルボディのホールがドレイン14に排出されて、チャネルボディ電位の低い状態である“0”データが書かれる。

【0104】

図35Bの場合、“1”データ書き込み時、選択された第1及び第2のワード線WL1及びWL2に基準電位VSSより高い正の電位VWLHを与え、選択ビット線BLには、基準電位VSSより高い正の電位VBLHを与える。これにより、選択されたメモリセルMCにおいて、5極管動作によるインパクトイオン化が生じ、ホールがチャネルボディに蓄積される。

【0105】

データ保持は、第1及び第2のワード線WL1及びWL2に基準電位VSSより低い負の電位VWLLを与える。これにより、チャネルボディに過剰ホールを蓄積した状態である“1”データを保持する。

【0106】

“0”データ書き込み時は、選択された第1及び第2のワード線WL1及びWL2に“1”書き込み時と同様の電位VWLHを与え、選択ビット線BLには基準電位VSSより低い負の電位VBLLを与える。これにより、選択されたメモリセルMCでドレイン接合が順バイアスになり、チャネルボディのホールがドレインに排出されて、チャネルボディ電位の低い状態である“0”データが書かれる。

【0107】

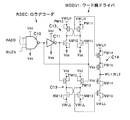

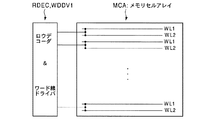

次に、この実施の形態におけるロウデコーダとワード線ドライバの具体的な回路構成の一例を説明する。図35Cは、ロウデコーダの一例と、図35Bに示したワード線WL1、WL2の電圧波形を生成するためのワード線ドライバWDDV1の一例を示す図である。

【0108】

この図35Cに示すように、ロウデコーダRDECは、NAND回路C10により構成されており、ワード線ドライバWDDV1は、インバータ回路C11と、レベル変換回路C12と、レベル変換回路C13と、出力バッファ回路C14とにより構成されている。この構成により、ロウデコーダRDECにより選択されたワード線ドライバWDDV1は、ハイレベルの電位を、正の電位VCCより高い電位であるVWLHに変換して、ワード線WL1、WL2に供給する。

【0109】

より具体的には、NAND回路C10には、ロウアドレス信号RADDとワード線イネーブル信号WLENとが、入力される。選択されたワード線WL1、WL2に対応するワード線ドライバWDDV1には、すべてハイレベルのロウアドレス信号RADDと、ハイレベルのワード線イネーブル信号WLENが入力される。したがって、選択されたワード線WL1、WL2に対応するワード線ドライバWDDV1のNAND回路C10の出力は、ローレベル、つまり基準電位VSSになる。NAND回路C10の出力は、インバータ回路C11に入力される。

【0110】

このインバータ回路C11は、入力された信号を反転して出力する。したがって、選択されたワード線ドライバWDDV1においては、インバータ回路C11の出力はハイレベル、つまり正の電位VCCになる。このインバータ回路C11の出力は、レベル変換回路C12とレベル変換回路C13とに入力される。また、レベル変換回路C12とレベル変換回路C13には、NAND回路C10の出力も、入力される。

【0111】

このレベル変換回路C12及びレベル変換回路C13の出力は、出力バッファ回路C14に入力される。レベル変換回路C12と出力バッファ回路C14とにより、インバータ回路C11のハイレベル出力電位であるVCCの出力を、VCCよりも高い正の電位であるVWLHに変換して、ワード線WL1、WL2に供給する。また、レベル変換回路C13と出力バッファ回路C14とにより、インバータ回路C11のローレベル出力電位であるVSSの出力を、VSSよりも低い電位であるVWLLに変換して、ワード線WL1、WL2に供給する。

【0112】

この実施の形態においては、レベル変換回路C12は、p型MOSトランジスタPM10、PM11と、n型MOSトランジスタNM10、NM11とを、備えて構成されている。p型MOSトランジスタPM10、PM11のソース端子は、それぞれ、電位VWLHの供給線に接続されており、そのドレイン端子は、それぞれ、n型MOSトランジスタNM10、NM11のドレイン端子に接続されている。また、p型MOSトランジスタPM10のゲート端子は、p型MOSトランジスタPM11とn型MOSトランジスタNM11の間のノードに接続されており、p型MOSトランジスタPM11のゲート端子は、p型MOSトランジスタPM10とn型MOSトランジスタNM10の間のノードに接続されている。

【0113】

n型MOSトランジスタNM10のゲート端子には、インバータ回路C11の出力が入力され、n型MOSトランジスタNM11のゲート端子には、NAND回路C10の出力が入力される。これらn型MOSトランジスタNM10、NM11のソース端子は、ぞれぞれ、電位VSSの供給線に接続されている。

【0114】

一方、レベル変換回路C13は、p型MOSトランジスタPM12、PM13と、n型MOSトランジスタNM12、NM13とを、備えて構成されている。p型MOSトランジスタPM12、PM13のソース端子は、それぞれ、電位VCCの供給線に接続されており、そのドレイン端子は、それぞれ、n型MOSトランジスタNM12、NM13のドレイン端子に接続されている。また、p型MOSトランジスタPM12のゲート端子には、インバータ回路C11の出力が入力され、p型MOSトランジスタPM13のゲート端子には、NAND回路C10の出力が入力される。

【0115】

n型MOSトランジスタNM12のゲート端子は、p型MOSトランジスタPM13とn型MOSトランジスタNM13との間のノードに接続されており、n型MOSトランジスタNM13のゲート端子は、p型MOSトランジスタPM12とn型MOSトランジスタNM12との間のノードに接続されている。また、これらn型MOSトランジスタNM12、NM13のソース端子は、ぞれぞれ、電位VWLLの供給線に接続されている。

【0116】

出力バッファ回路C14は、p型MOSトランジスタPM14、PM15と、n型MOSトランジスタNM14、NM15とを、直列的に接続することにより、構成されている。

【0117】

p型MOSトランジスタPM14のソース端子は、電位VWLHの供給線に接続されており、そのゲート端子は、レベル変換回路C12におけるp型MOSトランジスタPM11のゲート端子に接続されている。p型MOSトランジスタPM14のドレイン端子は、p型MOSトランジスタPM15のソース端子に接続されている。このp型MOSトランジスタPM15のゲート端子には、電位VSSが入力されている。このため、p型MOSトランジスタPM15は、ノーマリーオンのMOSトランジスタとなる。また、p型MOSトランジスタPM15のドレイン端子は、n型MOSトランジスタNM14のドレイン端子に接続されている。これらp型MOSトランジスタPM15とn型MOSトランジスタNM14との間のノードから、ワード線WL1、WL2を駆動するための電圧が出力される。

【0118】

n型MOSトランジスタNM14のゲート端子には、電位VCCが供給されている。このため、n型MOSトランジスタNM14は、ノーマリーオンのMOSトランジスタとなる。n型MOSトランジスタNM14のソース端子は、n型MOSトランジスタNM15のドレイン端子に接続されている。このn型MOSトランジスタNM15のゲート端子は、レベル変換回路C13におけるn型MOSトランジスタNM13のゲート端子に接続されている。また、n型MOSトランジスタNM15のソース端子は、電位VWLLの供給線に接続されている。

【0119】

以上のような構成のロウデコーダRDECとワード線ドライバWDDV1を用いて、図35Bに示す電位VWLH、VWLLを生成し、ワード線WL1、WL2に供給する。なお、図35Cにおいては、各MOSトランジスタでバックゲート接続がなされているが、これは必ずしも必要なものではない。

【0120】

なお、このワード線ドライバWDDV1の出力バッファ回路C14は、ノーマリーオンのMOSトランジスタPM15、NM14を備えているが、これは、MOSトランジスタPM14、NM15に、直接、電位VWLHと電位VWLLの電位差が印加しないようにするためである。すなわち、ノーマリーオンのMOSトランジスタPM15、NM14により、そのしきい値落ちをする分の電圧だけ、電位差が減少する。したがって、直接この電位差が、MOSトランジスタPM14、PM15に印加されてもよいのであれば、MOSトランジスタPM15、NM14は、図35Dに示すように、省略することも可能である。

【0121】

これら図35C又は図35Dに示したロウデコーダRDECとワード線ドライバWDDV1とを、メモリセルアレイMCAに配置したレイアウト図を、図35Eに示す。この図35Eに示すように、ワード線ドライバWDDV1のレイアウトピッチが、ワード線WL1、WL2の配線ピッチと一致する場合は、メモリセルアレイMCAの片側に、ロウデコーダRDECとワード線ドライバWDDV1とを配置することができる。

【0122】

これに対して、ワード線ドライバWDDV1のレイアウト面積が大きくなり、ワード線ドライバWDDV1のレイアウトピッチを、ワード線WL1、WL2の配線ピッチに一致させることができない場合、図35Fに示すようなレイアウトが考えられる。すなわち、メモリセルアレイMCAの両側にロウデコーダRDECとワード線ドライバWDDV1とを配置し、例えば、メモリセルアレイMCAの左側のロウデコーダRDECとワード線ドライバWDDV1で、奇数番目のワード線WL1、WL2のデコードと駆動を行い、メモリセルアレイMCAの右側のロウデコーダRDECとワード線ドライバWDDV1で、偶数番目のワード線WL1、WL2のデコードと駆動を行うようにする。

【0123】

次に、図35Aに対応するロウデータとワード線ドライバの回路構成を説明する。図35Gは、ロウデコーダの一例と、図35Aに示したワード線WL1、WL2の電圧波形を生成するためのワード線ドライバWDDV2の一例を示す図である。

【0124】

この図35Gに示すように、ロウデコーダRDECは、NAND回路C10により構成されており、ワード線ドライバWDDV2は、インバータ回路C11と、レベル変換回路C22と、レベル変換回路C23と、出力バッファ回路C24と、レベル変換回路C25と、出力バッファ回路C26とにより構成されている。ここでの電圧の高低関係は、図35Aの例に従って、VWL1H>VWL2H>VSS>VWL1L>VWL2Lである。

【0125】

図35Cと異なる点のみ説明すると、レベル変換回路C22は基本的に図35Cのレベル変換回路C12と同様の構成であり、p型MOSトランジスタPM20、PM21と、n型MOSトランジスタNM20、NM21とを備えている。但し、p型MOSトランジスタPM20、PM21のソース端子は、電位VWL1Hの供給線に接続されている。

【0126】

レベル変換回路C23も、基本的に図35Cのレベル変換回路C13と同様の構成であり、p型MOSトランジスタPM22、PM23と、n型MOSトランジスタNM22、NM23とを備えている。但し、n型MOSトランジスタNM22、NM23のソース端子は、電位VWL1Lの供給線に接続されている。

【0127】

出力バッファ回路C24も、基本的に図35Cの出力バッファ回路C14と同様の構成であり、直列的に接続されたp型MOSトランジスタPM24、PM25と、n型MOSトランジスタNM24、NM25とを備えている。但し、p型MOSトランジスタPM24のソース端子は、電位VWL1Hの供給線に接続されており、n型MOSトランジスタNM25のソース端子は、電位VWL1Lの供給線に接続されている。

【0128】

これに加えて、図35Gのワード線ドライバWDDV2は、レベル変換回路C25と出力バッファ回路C26とを備えている。レベル変換回路C25の構成はレベル変換回路C23の構成と同様であり、p型MOSトランジスタPM26、PM27と、n型MOSトランジスタNM26、NM27とを備えている。但し、n型MOSトランジスタNM26、NM27のソース端子は、電位VWL2Lの供給線に接続されている。

【0129】

出力バッファ回路C26は、出力バッファ回路C24と同様の構成であるが、p型MOSトランジスタPM28とn型MOSトランジスタNM28の2つのMOSトランジスタにより構成されている。そして、p型MOSトランジスタPM28のソース端子は、電位VWL2Hの供給線に接続されており、n型MOSトランジスタNM28のソース端子は、電位VWL2Lの供給線に接続されている。

【0130】

ノーマリーオンのMOSトランジスタが挿入されていないのは、図35Aからも分かるように、電位VWL2Hと電位VWL2Lとの電位差はそれほど大きくないので、この電位差が直接MOSトランジスタPM28、NM28に印加されても、問題が生じないからである。

【0131】

この構成から分かるように、出力バッファ回路C24の出力は、電位VWL1Hと電位VWL1Lとの間で振幅し、これにより、第1のワード線WL1が駆動される。また、出力バッファ回路C26の出力は、電位VWL2Hと電位VWL2Lとの間で、出力バッファ回路C24の出力と同期して振幅し、これにより、第2のワード線WL2が駆動される。なお、図35Gにおいては、各MOSトランジスタでバックゲート接続がなされているが、これは必ずしも必要なものではない。

【0132】

また、図35Dに示したワード線ドライバWDDV1と同様に、図35Hに示すようにワード線ドライバWDDV2においても、p型MOSトランジスタPM25とn型MOSトランジスタNM24とを、省くことも可能である。

【0133】

これら図35G又は図35Hに示したロウデコーダRDECとワード線ドライバWDDV2とを、メモリセルアレイMCAに配置したレイアウト図を、図35Iに示す。図35G及び図35Hに示したワード線ドライバWDDV2においては、第1のワード線WL1と第2のワード線WL2を異なる電位で同期的に駆動する関係上、そのレイアウト面積が図35C及び図35Dに示したワード線ドライバWDDV1よりも大きくなってしまう。したがって、ワード線WL1、WL2の配線ピッチに、ワード線ドライバWDDV2のレイアウトピッチを一致させることは困難であると考えられる。このため、図35Iに示したレイアウトにおいては、メモリセルアレイMCAの両側に、ロウデコーダRDECとワード線ドライバWDDV2とを配置している。すなわち、メモリセルアレイMCAの左側のロウデコーダRDECとワード線ドライバWDDV2で、奇数番目のワード線WL1、WL2のデコードと駆動を行い、メモリセルアレイMCAの右側のロウデコーダRDECとワード線ドライバWDDV2で、偶数番目のワード線WL1、WL2のデコードと駆動を行う。

【0134】

また、図35Jに示すように、例えば、第1のワード線WL1用のワード線ドライバWDDV3を、メモリセルアレイMCAの左側に配置し、第2のワード線WL2のワード線ドライバWDDV4を、メモリセルアレイMCAの右側に配置するようにしてもよい。このように配置することにより、電源配線の引き回しを楽にすることができる。すなわち、第1のワード線WL1用のワード線ドライバWDDV3のあるメモリセルアレイMCAの左側にのみ、電位VWL1Hと電位VWL1Lの電位供給線を配線し、第2のワード線WL2用のワード線ドライバWDDV4のあるメモリセルアレイMCAの右側にのみ、電位VWL2Hと電位VWL2Lの電位供給線を配線すればよい。

【0135】

但し、このレイアウトの場合、ワード線ドライバWDDV3とワード線ドライバWDDV4の双方に、個別にロウデコーダRDECが必要になる。そのようなワード線ドライバWDDV3の例を図35Kに示し、ワード線ドライバWDDV4の例を図35Lに示す。

【0136】

図35Kに示すように、第1のワード線WL1用のワード線ドライバWDDV3は、インバータ回路C11を介してロウデコーダRDECに接続されたレベル変換回路C22と、直接ロウデコーダRDECに接続されたレベル変換回路C23と、出力バッファ回路C24とを備えている。これらの構成は上述した図35Gのワード線ドライバWDDV2と同様である。

【0137】

一方、図35Lに示すように、第2のワード線WL2用のワード線ドライバWDDV4は、ロウデコーダRDECと、インバータ回路C11と、レベル変換回路C25と、出力バッファ回路C26とを備えて構成されている。レベル変換回路C25と出力バッファ回路C26の構成は、上述した図35Gのワード線ドライバWDDV2と同様である。但し、ワード線ドライバWDDV4はメモリセルアレイMCAの右側に設けられているため、ロウデコーダRDECをワード線ドライバWDDV3と共用することができないため、独自にロウデコーダRDECとインバータ回路C11とを設けている。

【0138】

ワード線ドライバWDDV3のロウデコーダRDECと、WDD4のロウデコーダRDECとには、ロウアドレス信号RADDとWLENとが同期して入力されるので、結果的に、異なる電圧振幅で同期したワード線駆動電位が出力される。

【0139】

なお、図35K及び図35Lにおいては、各MOSトランジスタでバックゲート接続がなされているが、これは必ずしも必要なものではない。また、図35Kに示したワード線ドライバWDDV3においても、図35Mに示すように、p型MOSトランジスタPM25とn型MOSトランジスタNM24とを、省くことも可能である。

【0140】

【発明の効果】

以上述べたようにこの発明によれば、一つのメモリセルは、フローティングの半導体層を持つ単純な一つのトランジスタにより形成され、セルサイズを4F2と小さくすることができる。トランジスタのソースは固定電位に接続され、ドレインに接続されたビット線とゲートに接続されたワード線の制御のみによって、読み出し,書き換え及びリフレッシュの制御が行われる。トランジスタのチャネルボディに対向する第2のゲートを設け、この第2のゲートが対向する表面部には高濃度層を設けることにより、第2のゲートをチャネルボディに容量結合させることによって、“0”,“1”データのしきい値電圧差を大きくすることができる。

【図面の簡単な説明】

【図1】この発明の基本コンセプトによるメモリセルの基本構造を示す断面図である。

【図2】同メモリセルの等価回路である。

【図3】同メモリセルを用いてDRAMのメモリセルアレイを構成した場合のレイアウトである。

【図4A】図3のA−A’断面図である。

【図4B】図3のB−B’断面図である。

【図5】同メモリセルのワード線電位とチャネルボディ電位の関係を示す図である。

【図6】同メモリセルの読み出し方式を説明するための図である。

【図7】同メモリセルの他の読み出し方式を説明するための図である。

【図8】同DRAMの“1”データ読み出し/リフレッシュの動作波形を示す図である。

【図9】同DRAMの“0”データ読み出し/リフレッシュの動作波形を示す図である。

【図10】同DRAMの“1”データ読み出し/“0”データ書き込みの動作波形を示す図である。

【図11】同DRAMの“0”データ読み出し/“1”データ書き込みの動作波形を示す図である。

【図12】同DRAMの他の読み出し方式による“1”データ読み出し/リフレッシュの動作波形を示す図である。

【図13】同DRAMの他の読み出し方式による“0”データ読み出し/リフレッシュの動作波形を示す図である。

【図14】同DRAMの他の読み出し方式による“1”データ読み出し/“0”データ書き込みの動作波形を示す図である。

【図15】同DRAMの他の読み出し方式による“0”データ読み出し/“1”データ書き込みの動作波形を示す図である。

【図16】同メモリセルの“0”書き込み/読み出しのシミュレーションによるチャネルボディ電位変化を示す図である。

【図17】同メモリセルの“1”書き込み/読み出しのシミュレーションによるチャネルボディ電位変化を示す図である。

【図18】同シミュレーションによる“0”,“1”データの読み出し時のドレイン電流−ゲート電圧特性を示す図である。

【図19A】この発明の実施の形態1によるメモリセルの構造を示す断面図である。

【図19B】図19Aに示すメモリセルをマトリクス配列したメモリセルアレイの等価回路を示す図である。

【図19C】図19Aに示すメモリセルをマトリクス配列したメモリセルアレイのレイアウトを示す図である。

【図19D】図19CのA−A’断面図である。

【図19E】図19CのB−B’断面図である。

【図19F】実施の形態1によるメモリセルの変形例を示す斜視図である。

【図19G】図19FのメモリセルのA−A’断面図である。

【図19H】図19FのメモリセルのB−B’断面図である。

【図19I】図19Fに示すメモリセルをマトリクス配列したメモリセルアレイのレイアウトを示す図である。

【図19J】図19IのA−A’断面図である。

【図19K】図19IのB−B’断面図である。

【図19L】図19IのC−C’断面図である。

【図19M】実施の形態1によるメモリセルの別の変形例を示す斜視図である。

【図19N】図19MのメモリセルのB−B’断面図である。

【図20】実施の形態2によるメモリセルの構造を示す断面図である。

【図21】実施の形態3によるメモリセルアレイの平面図である。

【図22】図21のA−A’断面図である。

【図23】実施の形態4によるメモリセルアレイの平面図である。

【図24】図23のA−A’断面図である。

【図25A】実施の形態5によるメモリセルの構造を示す断面図である。

【図25B】図25Aに示すメモリセルにおいて、ドレイン領域に正の電位を印加し、ゲートに正の電位を印加し、ソース領域をグランドに接続した場合における、メモリセルの状態を示す模式図である。

【図25C】図25Aに示すメモリセルにおいて、ドレイン領域に負の電位を印加し、ゲートに正の電位を印加し、ソース領域をグランドに接続した場合における、メモリセルの状態を示す模式図である。

【図26】同実施の形態のメモリセルの特性を示す図である。

【図27】実施の形態6によるメモリセルの構造を示す断面図である。

【図28】実施の形態6によるメモリセルの別の構造を示す断面図である。

【図29A】SGT構造のメモリセルにゲートオフセット構造を適用した場合のメモリセルアレイの平面図である(実施の形態6)。

【図29B】図29AによるメモリセルアレイのA−A’断面図である。

【図30A】実施の形態3において、ゲートオフセット構造を導入した場合のメモリセルアレイの平面図である(実施の形態6)。

【図30B】図30AによるメモリセルアレイのA−A’断面図である。

【図30C】実施の形態4において、ゲートオフセット構造を導入した場合のメモリセルアレイの平面図である(実施の形態6)。

【図30D】図30CによるメモリセルアレイのA−A’断面図である。

【図31】MISFETのGIDL電流を示す特性図である(実施の形態7)。

【図32】GIDL電流を用いた“1”書き込み/読み出しの動作波形図である。

【図33】実施の形態8によるメモリセルアレイの平面図である。

【図34A】図33のA−A’断面図である。

【図34B】図33のB−B’断面図である。

【図35A】第1のゲートと第2のゲートとを異なる電位で同期駆動した場合における、メモリセルの書き込み動作を示す波形図である(実施の形態9)。

【図35B】第1のゲートと第2のゲートとを同電位で駆動した場合における、メモリセルの書き込み動作を示す波形図である(実施の形態9)。

【図35C】図35Bの書き込み動作波形を生成するためのワード線ドライバとロウデコーダの回路構成の一例を示す図である。

【図35D】図35Cに示したワード線ドライバの変形例を示す図である。

【図35E】図35C又は図35Dに示したロウデコーダとワード線ドライバとを、メモリセルアレイに対して配置した場合のレイアウトの一例を示す図である(片側配置)。

【図35F】図35C又は図35Dに示したロウデコーダとワード線ドライバとを、メモリセルアレイに対して配置した場合のレイアウトの一例を示す図である(両側配置)。

【図35G】図35Aの書き込み動作波形を生成するためのワード線ドライバとロウデコーダの回路構成の一例を示す図である。

【図35H】図35Gに示したワード線ドライバの変形例を示す図である。

【図35I】図35G又は図35Hに示したロウデコーダとワード線ドライバとを、メモリセルアレイに対して配置した場合のレイアウトの一例を示す図である(第1のワード線と第2のワード線とからなる対のワード線に対して、左右交互にロウデコーダとワード線ドライバとを設けた場合)。

【図35J】図35G又は図35Hに示したロウデコーダとワード線ドライバとを、メモリセルアレイに対して配置した場合のレイアウトの一例を示す図である(片側に第1のワード線用のロウデコーダとワード線ドライバとを設け、もう片側に第2のワード線のロウデコーダとワード線ドライバとを設けた場合)。

【図35K】図35Jに示したレイアウトを採用する場合における、第1のワード線用のロウデコーダとワード線ドライバの回路構成の一例を示す図である。

【図35L】図35Jに示したレイアウトを採用する場合における、第2のワード線用のロウデコーダとワード線ドライバの回路構成の一例を示す図である。

【図35M】図35Kに示したワード線ドライバの変形例を示す図である。

【符号の説明】

10 シリコン基板

11 シリコン酸化膜

12 p型シリコン層

13 第1のゲート

14 ドレイン拡散層

15 ソース拡散層

20 第2のゲート

Claims (25)

- メモリセルを構成するための複数のMISトランジスタを有する半導体メモリ装置であって、各MISトランジスタは、

半導体層と、

前記半導体層に形成されたソース領域と、

前記半導体層に前記ソース領域と離れて形成されたドレイン領域であって、前記ソース領域と前記ドレイン領域との間の前記半導体層が、フローティング状態のチャネルボディとなる、ドレイン領域と、

前記チャネルボディにチャネルを形成するための第1のゲートと、

前記チャネルボディの電位を容量結合により制御するための第2のゲートと、

前記チャネルボディの前記第2のゲート側に形成された高濃度領域であって、前記チャネルボディと同じ導電型で前記チャネルボディの不純物濃度よりも高い不純物濃度を有する、高濃度領域と、

を備え、

前記MISトランジスタは、前記チャネルボディを第1の電位に設定した第1データ状態と、前記チャネルボディを第2の電位に設定した第2データ状態とをダイナミックに記憶する、

ことを特徴とする半導体メモリ装置。 - 前記MISトランジスタのドレイン領域がビット線に接続されており、前記MISトランジスタの第1のゲートが第1のワード線に接続されており、前記MISトランジスタのソース領域がソース線に接続されており、

前記ソース領域と前記ドレイン領域は、n型の半導体層で構成されており、前記ソース領域と前記ドレイン領域との間の前記チャネルボディは、p型の半導体層で構成されており、

前記ソース線の電位が0Vに固定された状態で、前記第1のワード線を正の電位にし、前記ビット線を正の電位にすることにより、前記MISトランジスタに前記第1データ状態を書き込み、前記第1のワード線を正の電位にし、前記ビット線を負の電位にすることにより、前記MISトランジスタに前記第2データ状態を書き込む、書き込み手段を、さらに備えることを特徴とする請求項1記載の半導体メモリ装置。 - 前記第1のゲートと前記第2のゲートとは、別個に形成されていることを特徴とする請求項1記載の半導体メモリ装置。

- 前記MISトランジスタが複数個マトリクス配列され、第1の方向に並ぶMISトランジスタのドレイン領域がビット線に、第2の方向に並ぶMISトランジスタの第1のゲートが第1のワード線に、前記MISトランジスタのソース領域が固定電位に、前記第2の方向に並ぶ前記MISトランジスタの第2のゲートが第2のワード線にそれぞれ接続されてメモリセルアレイが構成されている、

ことを特徴とする請求項3記載の半導体メモリ装置。 - 前記MISトランジスタが複数個マトリクス配列され、第1の方向に並ぶMISトランジスタのドレイン領域がビット線に、第2の方向に並ぶMISトランジスタの第1のゲートがワード線に、前記MISトランジスタのソース領域が第1の固定電位に、前記MISトランジスタの第2のゲートは全MISトランジスタの共通プレートとして第2の固定電位にそれぞれ接続されてメモリセルアレイが構成されている、

ことを特徴とする請求項3記載の半導体メモリ装置。 - 前記半導体層は、半導体基板上に絶縁膜により分離されて形成されたものであり、

前記第1のゲートは、前記半導体層の上部に第1のワード線として連続的に配設され、前記第2のゲートは、前記半導体層の下部に前記第1のワード線と並行する第2のワード線として連続的に配設されている、

ことを特徴とする請求項3記載の半導体メモリ装置。 - 前記半導体層は、半導体基板上に形成された柱状半導体であり、

前記第1のゲートは、前記柱状半導体層の一つの側面に対向するように形成され、前記第2のゲートは、前記柱状半導体層の前記第1のゲートと反対側の側面に形成された前記高濃度領域に対向するように形成され、前記ドレイン領域が前記柱状半導体の上面に、前記ソース領域が前記柱状半導体の下部に形成されている、

ことを特徴とする請求項3記載の半導体メモリ装置。 - 前記第1のゲートは、前記ソース領域に対する重なり量が正であり、前記ドレイン領域に対する重なり量が負である、ことを特徴とする請求項3記載の半導体メモリ装置。

- 前記第1のゲートは、前記ソース領域に対する重なり量が正であり、前記ドレイン領域に対する重なり量が負である、ことを特徴とする請求項5記載の半導体メモリ装置。

- 前記第1のゲートは、前記ソース領域に対する重なり量が正であり、前記ドレイン領域に対する重なり量が負である、ことを特徴とする請求項7記載の半導体メモリ装置。

- 前記第1のゲートと前記第2のゲートとを駆動する駆動回路であって、前記第2のゲートを、前記第1のゲートより低い電位で同期して駆動する、駆動回路を、さらに備えることを特徴とする請求項3記載の半導体メモリ装置。

- 前記第1のゲートと前記第2のゲートを同じ電位で同期して駆動する、駆動回路を、さらに備えることを特徴とする請求項3記載の半導体メモリ装置。

- 前記第1のゲートと前記第2のゲートとは、共通に形成された共通ゲートとして構成されている、ことを特徴とする請求項1記載の半導体メモリ装置。

- 前記高濃度領域は、前記チャネルボディにおける前記共通ゲート側表面の一部に形成されている、ことを特徴とする請求項13記載の半導体メモリ装置。

- 前記高濃度領域は、前記ソース領域と前記ドレイン領域とに接している、ことを特徴とする請求項14記載の半導体メモリ装置。

- 前記高濃度領域は、前記ソース領域と前記ドレイン領域とのいずれにも接していない、ことを特徴とする請求項14記載の半導体メモリ装置。

- 前記半導体層は、半導体基板上に形成された柱状半導体層であり、

前記共通ゲートは、前記柱状半導体層の周囲を取り囲むように形成され、前記柱状半導体層の一つ以上の側面に前記高濃度領域が形成され、前記ドレイン領域が前記柱状半導体の上面に、前記ソース領域が前記柱状半導体の下部に形成されている、

ことを特徴とする請求項13記載の半導体メモリ装置。 - 前記共通ゲートは、前記ソース領域に対する重なり量が正であり、前記ドレイン領域に対する重なり量が負である、ことを特徴とする請求項17記載の半導体メモリ装置。

- 前記半導体層は、半導体基板上に形成された凸型半導体層であり、

前記共通ゲートは、前記凸型半導体層の上面及び両側面に対向するように形成され、前記凸型半導体層の前記共通ゲートが対向する一つ以上の側面に前記高濃度領域が形成され、前記凸型半導体層に前記共通ゲートを挟んで前記ドレイン領域及び前記ソース領域が形成されている、

ことを特徴とする請求項13記載の半導体メモリ装置。 - 前記MISトランジスタのドレイン領域がビット線に接続されており、前記MISトランジスタの第1のゲートが第1のワード線に接続されており、前記MISトランジスタのソース領域がソース線に接続されており、

前記ソース領域と前記ドレイン領域は、n型の半導体層で構成されており、前記ソース領域と前記ドレイン領域との間の前記チャネルボディは、p型の半導体層で構成されており、

前記ソース線の電位が0Vに固定された状態で、前記第1のワード線を負の電位にし、前記ビット線を正の電位にすることにより、前記MISトランジスタに前記第1データ状態を書き込み、前記第1のワード線を正の電位にし、前記ビット線を負の電位にすることにより、前記MISトランジスタに前記第2データ状態を書き込む、書き込み手段を、さらに備えることを特徴とする請求項1記載の半導体メモリ装置。 - メモリセルを構成するための複数のMISトランジスタを有する半導体メモリ装置であって、各MISトランジスタは、

半導体層と、

前記半導体層に形成されたソース領域と、

前記半導体層に前記ソース領域と離れて形成されたドレイン領域であって、前記ソース領域と前記ドレイン領域との間の前記半導体層が、フローティング状態のチャネルボディとなる、ドレイン領域と、

前記チャネルボディにチャネルを形成するための第1のゲートと、

を備え、

前記第1のゲートは、前記ソース領域に対する重なり量が正であり、前記ドレイン領域に対する重なり量が負であるように配置して、前記第1のゲートを前記ドレイン領域に対してオフセットさせており、

前記MISトランジスタのドレイン領域がビット線に接続されており、前記MISトランジスタの第1のゲートが第1のワード線に接続されており、前記MISトランジスタのソース領域がソース線に接続されており、

前記ソース領域と前記ドレイン領域は、n型の半導体層で構成されており、前記ソース領域と前記ドレイン領域との間の前記チャネルボディは、p型の半導体層で構成されており、

前記ソース線の電位が0Vに固定された状態で、前記第1のワード線を正の電位にし、前記ビット線を正の電位にすることにより、前記MISトランジスタに前記第1データ状態を書き込み、前記第1のワード線を正の電位にし、前記ビット線を負の電位にすることにより、前記MISトランジスタに前記第2データ状態を書き込む、書き込み手段を、さらに備えることを特徴とする半導体メモリ装置。 - 前記MISトランジスタは、同じ電位を前記第1のゲートに与えた場合でも、前記ドレイン領域から前記ソース領域へ流れるチャネル電流の方が、前記ソース領域から前記ドレイン領域へ流れるチャネル電流よりも多い、ことを特徴とする請求項21記載の半導体メモリ装置。

- 前記MISトランジスタは、前記第1のゲートとは別に、前記チャネルボディの電位を容量結合により制御するための第2のゲートを、さらに備えることを特徴とする請求項21記載の半導体メモリ装置。

- 前記MISトランジスタは、前記チャネルボディにおける前記第2のゲート側の表面に形成され、且つ、前記チャネルボディと同じ導電型で前記チャネルボディよりも高い不純物濃度を有する高濃度領域を、さらに備えることを特徴とする請求項21記載の半導体メモリ装置。

- メモリセルを構成するための複数のMISトランジスタを有する半導体メモリ装置であって、各MISトランジスタは、

半導体層と、

前記半導体層に形成されたソース領域と、

前記半導体層に前記ソース領域と離れて形成されたドレイン領域であって、前記ソース領域と前記ドレイン領域との間の前記半導体層が、フローティング状態のチャネルボディとなる、ドレイン領域と、

前記チャネルボディにチャネルを形成するためのゲートと、

を備え、

前記MISトランジスタのドレイン領域がビット線に接続されており、前記MISトランジスタのゲートがワード線に接続されており、前記MISトランジスタのソース領域がソース線に接続されており、

前記ソース領域と前記ドレイン領域は、n型の半導体層で構成されており、前記ソース領域と前記ドレイン領域との間の前記チャネルボディは、p型の半導体層で構成されており、

前記ソース線の電位が0Vに固定された状態で、前記ワード線を負の電位にし、前記ビット線を正の電位にすることにより、前記MISトランジスタに前記第1データ状態を書き込み、前記ワード線を正の電位にし、前記ビット線を負の電位にすることにより、前記MISトランジスタに前記第2データ状態を書き込む、書き込み手段を、さらに備える、

ことを特徴とする半導体メモリ装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2001371802A JP4354663B2 (ja) | 2001-03-15 | 2001-12-05 | 半導体メモリ装置 |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2001074236 | 2001-03-15 | ||

| JP2001-74236 | 2001-03-15 | ||

| JP2001371802A JP4354663B2 (ja) | 2001-03-15 | 2001-12-05 | 半導体メモリ装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2002343886A JP2002343886A (ja) | 2002-11-29 |

| JP4354663B2 true JP4354663B2 (ja) | 2009-10-28 |

Family

ID=26611335

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2001371802A Expired - Fee Related JP4354663B2 (ja) | 2001-03-15 | 2001-12-05 | 半導体メモリ装置 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4354663B2 (ja) |

Families Citing this family (73)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| TWI230392B (en) | 2001-06-18 | 2005-04-01 | Innovative Silicon Sa | Semiconductor device |

| EP1357603A3 (en) | 2002-04-18 | 2004-01-14 | Innovative Silicon SA | Semiconductor device |

| EP1355316B1 (en) | 2002-04-18 | 2007-02-21 | Innovative Silicon SA | Data storage device and refreshing method for use with such device |

| US6861689B2 (en) * | 2002-11-08 | 2005-03-01 | Freescale Semiconductor, Inc. | One transistor DRAM cell structure and method for forming |

| JP2004297048A (ja) * | 2003-03-11 | 2004-10-21 | Semiconductor Energy Lab Co Ltd | 集積回路、該集積回路を有する半導体表示装置及び集積回路の駆動方法 |

| US7541614B2 (en) * | 2003-03-11 | 2009-06-02 | Semiconductor Energy Laboratory Co., Ltd. | Integrated circuit, semiconductor device comprising the same, electronic device having the same, and driving method of the same |

| US7085153B2 (en) | 2003-05-13 | 2006-08-01 | Innovative Silicon S.A. | Semiconductor memory cell, array, architecture and device, and method of operating same |

| US20040228168A1 (en) | 2003-05-13 | 2004-11-18 | Richard Ferrant | Semiconductor memory device and method of operating same |

| US6912150B2 (en) | 2003-05-13 | 2005-06-28 | Lionel Portman | Reference current generator, and method of programming, adjusting and/or operating same |

| US7335934B2 (en) | 2003-07-22 | 2008-02-26 | Innovative Silicon S.A. | Integrated circuit device, and method of fabricating same |

| US7184298B2 (en) | 2003-09-24 | 2007-02-27 | Innovative Silicon S.A. | Low power programming technique for a floating body memory transistor, memory cell, and memory array |

| JP2005158952A (ja) * | 2003-11-25 | 2005-06-16 | Toshiba Corp | 半導体装置及びその製造方法 |

| JP4559728B2 (ja) | 2003-12-26 | 2010-10-13 | 株式会社東芝 | 半導体記憶装置 |

| JP3898715B2 (ja) | 2004-09-09 | 2007-03-28 | 株式会社東芝 | 半導体装置およびその製造方法 |

| US7476939B2 (en) | 2004-11-04 | 2009-01-13 | Innovative Silicon Isi Sa | Memory cell having an electrically floating body transistor and programming technique therefor |

| US7251164B2 (en) | 2004-11-10 | 2007-07-31 | Innovative Silicon S.A. | Circuitry for and method of improving statistical distribution of integrated circuits |

| WO2006065698A2 (en) | 2004-12-13 | 2006-06-22 | William Kenneth Waller | Sense amplifier circuitry and architecture to write data into and/or read data from memory cells |

| US7301803B2 (en) | 2004-12-22 | 2007-11-27 | Innovative Silicon S.A. | Bipolar reading technique for a memory cell having an electrically floating body transistor |

| CN1897282A (zh) * | 2005-06-30 | 2007-01-17 | St微电子克鲁勒斯图股份公司 | 包括具有隔离体的一个mos晶体管的存储单元 |

| JP2007018588A (ja) * | 2005-07-06 | 2007-01-25 | Toshiba Corp | 半導体記憶装置および半導体記憶装置の駆動方法 |

| US7606066B2 (en) | 2005-09-07 | 2009-10-20 | Innovative Silicon Isi Sa | Memory cell and memory cell array having an electrically floating body transistor, and methods of operating same |

| US7355916B2 (en) | 2005-09-19 | 2008-04-08 | Innovative Silicon S.A. | Method and circuitry to generate a reference current for reading a memory cell, and device implementing same |

| US7683430B2 (en) | 2005-12-19 | 2010-03-23 | Innovative Silicon Isi Sa | Electrically floating body memory cell and array, and method of operating or controlling same |

| US7542345B2 (en) | 2006-02-16 | 2009-06-02 | Innovative Silicon Isi Sa | Multi-bit memory cell having electrically floating body transistor, and method of programming and reading same |

| US7492632B2 (en) | 2006-04-07 | 2009-02-17 | Innovative Silicon Isi Sa | Memory array having a programmable word length, and method of operating same |

| US7606098B2 (en) | 2006-04-18 | 2009-10-20 | Innovative Silicon Isi Sa | Semiconductor memory array architecture with grouped memory cells, and method of controlling same |

| US7933142B2 (en) | 2006-05-02 | 2011-04-26 | Micron Technology, Inc. | Semiconductor memory cell and array using punch-through to program and read same |

| US8069377B2 (en) | 2006-06-26 | 2011-11-29 | Micron Technology, Inc. | Integrated circuit having memory array including ECC and column redundancy and method of operating the same |

| US7542340B2 (en) | 2006-07-11 | 2009-06-02 | Innovative Silicon Isi Sa | Integrated circuit including memory array having a segmented bit line architecture and method of controlling and/or operating same |

| US7932547B2 (en) | 2006-07-27 | 2011-04-26 | Hynix Semiconductor Inc. | Nonvolatile ferroelectric memory device using silicon substrate, method for manufacturing the same, and refresh method thereof |

| KR100720230B1 (ko) | 2006-07-27 | 2007-05-23 | 주식회사 하이닉스반도체 | 실리콘 기판을 이용한 불휘발성 강유전체 메모리 장치, 그형성 방법 및 그 리프레쉬 방법 |

| KR101406604B1 (ko) | 2007-01-26 | 2014-06-11 | 마이크론 테크놀로지, 인코포레이티드 | 게이트형 바디 영역으로부터 격리되는 소스/드레인 영역을 포함하는 플로팅-바디 dram 트랜지스터 |

| US8518774B2 (en) | 2007-03-29 | 2013-08-27 | Micron Technology, Inc. | Manufacturing process for zero-capacitor random access memory circuits |

| US8064274B2 (en) | 2007-05-30 | 2011-11-22 | Micron Technology, Inc. | Integrated circuit having voltage generation circuitry for memory cell array, and method of operating and/or controlling same |

| US8085594B2 (en) | 2007-06-01 | 2011-12-27 | Micron Technology, Inc. | Reading technique for memory cell with electrically floating body transistor |

| KR100894683B1 (ko) | 2007-08-28 | 2009-04-24 | 경북대학교 산학협력단 | 고성능 단일 트랜지스터 플로팅 바디 dram 소자 및 그제조 방법 |

| KR101357304B1 (ko) * | 2007-09-11 | 2014-01-28 | 삼성전자주식회사 | 커패시터리스 디램 및 그의 제조 및 동작방법 |

| WO2009039169A1 (en) | 2007-09-17 | 2009-03-26 | Innovative Silicon S.A. | Refreshing data of memory cells with electrically floating body transistors |

| US8536628B2 (en) | 2007-11-29 | 2013-09-17 | Micron Technology, Inc. | Integrated circuit having memory cell array including barriers, and method of manufacturing same |

| US8349662B2 (en) | 2007-12-11 | 2013-01-08 | Micron Technology, Inc. | Integrated circuit having memory cell array, and method of manufacturing same |

| US8773933B2 (en) | 2012-03-16 | 2014-07-08 | Micron Technology, Inc. | Techniques for accessing memory cells |

| US8014195B2 (en) | 2008-02-06 | 2011-09-06 | Micron Technology, Inc. | Single transistor memory cell |

| US8189376B2 (en) | 2008-02-08 | 2012-05-29 | Micron Technology, Inc. | Integrated circuit having memory cells including gate material having high work function, and method of manufacturing same |

| JP5779702B2 (ja) * | 2008-02-15 | 2015-09-16 | ユニサンティス エレクトロニクス シンガポール プライベート リミテッドUnisantis Electronics Singapore Pte Ltd. | 半導体装置及びその製造方法 |

| US7957206B2 (en) | 2008-04-04 | 2011-06-07 | Micron Technology, Inc. | Read circuitry for an integrated circuit having memory cells and/or a memory cell array, and method of operating same |

| US7947543B2 (en) | 2008-09-25 | 2011-05-24 | Micron Technology, Inc. | Recessed gate silicon-on-insulator floating body device with self-aligned lateral isolation |

| US7933140B2 (en) | 2008-10-02 | 2011-04-26 | Micron Technology, Inc. | Techniques for reducing a voltage swing |

| US7924630B2 (en) | 2008-10-15 | 2011-04-12 | Micron Technology, Inc. | Techniques for simultaneously driving a plurality of source lines |

| KR101497542B1 (ko) * | 2008-10-21 | 2015-03-02 | 삼성전자주식회사 | 반도체 소자의 동작 방법 |

| US8223574B2 (en) | 2008-11-05 | 2012-07-17 | Micron Technology, Inc. | Techniques for block refreshing a semiconductor memory device |

| US8213226B2 (en) | 2008-12-05 | 2012-07-03 | Micron Technology, Inc. | Vertical transistor memory cell and array |

| US8319294B2 (en) | 2009-02-18 | 2012-11-27 | Micron Technology, Inc. | Techniques for providing a source line plane |

| KR101073643B1 (ko) | 2009-02-19 | 2011-10-14 | 서울대학교산학협력단 | 고성능 단일 트랜지스터 플로팅 바디 dram 소자 및 그 제조 방법 |

| US8710566B2 (en) | 2009-03-04 | 2014-04-29 | Micron Technology, Inc. | Techniques for forming a contact to a buried diffusion layer in a semiconductor memory device |

| CN102365628B (zh) | 2009-03-31 | 2015-05-20 | 美光科技公司 | 用于提供半导体存储器装置的技术 |

| KR101080200B1 (ko) * | 2009-04-14 | 2011-11-07 | 주식회사 하이닉스반도체 | 반도체 메모리 장치 및 그 리프레쉬 제어 방법 |

| US8139418B2 (en) | 2009-04-27 | 2012-03-20 | Micron Technology, Inc. | Techniques for controlling a direct injection semiconductor memory device |

| US8508994B2 (en) | 2009-04-30 | 2013-08-13 | Micron Technology, Inc. | Semiconductor device with floating gate and electrically floating body |

| US8498157B2 (en) | 2009-05-22 | 2013-07-30 | Micron Technology, Inc. | Techniques for providing a direct injection semiconductor memory device |

| US8537610B2 (en) | 2009-07-10 | 2013-09-17 | Micron Technology, Inc. | Techniques for providing a semiconductor memory device |

| US9076543B2 (en) | 2009-07-27 | 2015-07-07 | Micron Technology, Inc. | Techniques for providing a direct injection semiconductor memory device |

| US8199595B2 (en) | 2009-09-04 | 2012-06-12 | Micron Technology, Inc. | Techniques for sensing a semiconductor memory device |

| US8174881B2 (en) | 2009-11-24 | 2012-05-08 | Micron Technology, Inc. | Techniques for reducing disturbance in a semiconductor device |

| FR2953636B1 (fr) * | 2009-12-08 | 2012-02-10 | Soitec Silicon On Insulator | Procede de commande d'une cellule memoire dram sur seoi disposant d'une seconde grille de controle enterree sous la couche isolante |

| US8310893B2 (en) | 2009-12-16 | 2012-11-13 | Micron Technology, Inc. | Techniques for reducing impact of array disturbs in a semiconductor memory device |

| US8416636B2 (en) | 2010-02-12 | 2013-04-09 | Micron Technology, Inc. | Techniques for controlling a semiconductor memory device |

| US8411513B2 (en) | 2010-03-04 | 2013-04-02 | Micron Technology, Inc. | Techniques for providing a semiconductor memory device having hierarchical bit lines |

| US8576631B2 (en) | 2010-03-04 | 2013-11-05 | Micron Technology, Inc. | Techniques for sensing a semiconductor memory device |

| US8369177B2 (en) | 2010-03-05 | 2013-02-05 | Micron Technology, Inc. | Techniques for reading from and/or writing to a semiconductor memory device |

| WO2011115893A2 (en) | 2010-03-15 | 2011-09-22 | Micron Technology, Inc. | Techniques for providing a semiconductor memory device |

| US8411524B2 (en) | 2010-05-06 | 2013-04-02 | Micron Technology, Inc. | Techniques for refreshing a semiconductor memory device |

| US8531878B2 (en) | 2011-05-17 | 2013-09-10 | Micron Technology, Inc. | Techniques for providing a semiconductor memory device |

| US9559216B2 (en) | 2011-06-06 | 2017-01-31 | Micron Technology, Inc. | Semiconductor memory device and method for biasing same |

-

2001

- 2001-12-05 JP JP2001371802A patent/JP4354663B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2002343886A (ja) | 2002-11-29 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4354663B2 (ja) | 半導体メモリ装置 | |

| KR100525138B1 (ko) | 반도체 메모리 장치 | |

| KR100466559B1 (ko) | 반도체 메모리 장치 | |

| JP4364227B2 (ja) | 半導体記憶装置 | |

| JP4053738B2 (ja) | 半導体メモリ装置 | |

| JP4713783B2 (ja) | 半導体メモリ装置 | |

| JP4064607B2 (ja) | 半導体メモリ装置 | |

| US6882008B1 (en) | Semiconductor integrated circuit device | |

| US20090213675A1 (en) | Semiconductor memory device | |

| TWI813133B (zh) | 半導體元件記憶裝置 | |

| JP2007018588A (ja) | 半導体記憶装置および半導体記憶装置の駆動方法 | |

| JP2009026448A (ja) | メモリセル構造、メモリセルアレイ、メモリ装置、メモリ制御器、メモリシステム及びこれらを動作する方法 | |

| TWI794046B (zh) | 半導體元件記憶裝置 | |

| TW202305798A (zh) | 半導體元件記憶裝置 | |

| JP2009093708A (ja) | 半導体記憶装置およびその駆動方法 | |

| JP2002260381A (ja) | 半導体メモリ装置 | |

| JP4745276B2 (ja) | 半導体メモリ装置 | |

| KR100892731B1 (ko) | 1-트랜지스터형 디램 구동 방법 | |

| TWI806354B (zh) | 半導體元件記憶裝置 | |

| US7724569B2 (en) | 1-transistor type DRAM driving method with an improved write operation margin | |

| JP2000091452A (ja) | 半導体記憶装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20040913 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20070524 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20071204 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080117 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20090515 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20090612 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20090703 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20090730 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120807 Year of fee payment: 3 |

|

| LAPS | Cancellation because of no payment of annual fees |