JP2010183473A - 増幅器 - Google Patents

増幅器 Download PDFInfo

- Publication number

- JP2010183473A JP2010183473A JP2009026988A JP2009026988A JP2010183473A JP 2010183473 A JP2010183473 A JP 2010183473A JP 2009026988 A JP2009026988 A JP 2009026988A JP 2009026988 A JP2009026988 A JP 2009026988A JP 2010183473 A JP2010183473 A JP 2010183473A

- Authority

- JP

- Japan

- Prior art keywords

- bias voltage

- transistor

- gate

- node

- amplifier

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F1/00—Details of amplifiers with only discharge tubes, only semiconductor devices or only unspecified devices as amplifying elements

- H03F1/08—Modifications of amplifiers to reduce detrimental influences of internal impedances of amplifying elements

- H03F1/22—Modifications of amplifiers to reduce detrimental influences of internal impedances of amplifying elements by use of cascode coupling, i.e. earthed cathode or emitter stage followed by earthed grid or base stage respectively

- H03F1/223—Modifications of amplifiers to reduce detrimental influences of internal impedances of amplifying elements by use of cascode coupling, i.e. earthed cathode or emitter stage followed by earthed grid or base stage respectively with MOSFET's

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F1/00—Details of amplifiers with only discharge tubes, only semiconductor devices or only unspecified devices as amplifying elements

- H03F1/34—Negative-feedback-circuit arrangements with or without positive feedback

- H03F1/342—Negative-feedback-circuit arrangements with or without positive feedback in field-effect transistor amplifiers

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F1/00—Details of amplifiers with only discharge tubes, only semiconductor devices or only unspecified devices as amplifying elements

- H03F1/56—Modifications of input or output impedances, not otherwise provided for

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F2200/00—Indexing scheme relating to amplifiers

- H03F2200/27—A biasing circuit node being switched in an amplifier circuit

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F2200/00—Indexing scheme relating to amplifiers

- H03F2200/294—Indexing scheme relating to amplifiers the amplifier being a low noise amplifier [LNA]

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Amplifiers (AREA)

- Transceivers (AREA)

- Transmitters (AREA)

- Circuits Of Receivers In General (AREA)

- Input Circuits Of Receivers And Coupling Of Receivers And Audio Equipment (AREA)

Abstract

増幅器の起動時間が長い。

【解決手段】

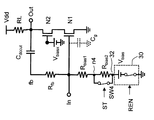

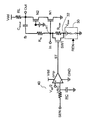

カスコード接続の増幅器において,入力端子と出力端子との間に設けられ抵抗素子と容量素子とを有するフィードバック経路と,イネーブル信号に応答してソース接地トランジスタのゲートバイアス電圧を生成するバイアス電圧生成回路と,バイアス電圧生成回路の出力ノードとソース接地トランジスタのゲートとの間に設けられた給電抵抗素子と,ゲートバイアス電圧出力ノードからフィードバック経路内のノードまでの抵抗値を,イネーブル信号の開始時に一次的に低下させるイネーブルスイッチとを有する。

【選択図】 図7

Description

Zin=Zf/(A−1)

ただし,Zfはフィードバック経路fbのインピーダンス,AはLNAの利得である。そして,利得Aは,トランジスタN1の相互コンダクタンスgmと負荷抵抗RLの積(A=gm×RL)である。

N2:第2のトランジスタ Out:出力端子

RL:負荷抵抗素子 fb:フィードバック経路

Rfb:フィードバック抵抗 Cdccut:容量素子

Rbias:給電抵抗 30:ゲートバイアス電圧生成回路

32:ゲートバイアス電圧出力端子 SW1:イネーブルスイッチ

REN:受信イネーブル信号

Claims (10)

- 入力端子にゲートが接続されソースが接地された第1のトランジスタと,

前記第1のトランジスタのドレインと電源との間に設けられた負荷抵抗素子と,

前記第1のトランジスタのドレインと前記負荷素子との間のノードに接続された出力端子と,

前記入力端子と出力端子との間に設けられ抵抗素子と容量素子とを有するフィードバック経路と,

イネーブル信号に応答して前記第1のトランジスタのゲートにゲートバイアス電圧を印加するバイアス電圧生成回路と,

前記バイアス電圧生成回路の前記ゲートバイアス電圧の出力ノードと前記第1のトランジスタのゲートとの間に設けられた給電抵抗素子と,

前記ゲートバイアス電圧の前記出力ノードから前記フィードバック経路内のノードまでの抵抗値を,前記イネーブル信号に応答して低下させるイネーブルスイッチとを有する増幅器。 - 請求項1において,

さらに,前記第1のトランジスタのドレインと前記負荷抵抗素子との間にカスコード接続され,ゲートに所定のバイアス電圧が供給されている第2のトランジスタを有する増幅器。 - 請求項1または2において,

前記イネーブルスイッチは,前記ゲートバイアス電圧の前記出力ノードと前記入力端子との間に設けられ,前記イネーブル信号に応答して一次的に導通し,その後の通常動作状態では非導通になる増幅器。 - 請求項1または2において,

前記イネーブルスイッチは,前記ゲートバイアス電圧の前記出力ノードと前記フィードバック経路内のノードとの間に設けられ,前記イネーブル信号に応答して一次的に導通し,その後の通常動作状態では非導通になる増幅器。 - 請求項1または2において,

前記イネーブルスイッチは,前記ゲートバイアス電圧の前記出力ノードと前記給電抵抗内のノードとの間に設けられ,前記イネーブル信号に応答して一次的に導通し,その後の通常動作状態では非導通になる増幅器。 - 請求項1または2において,

前記入力端子は帯域通過フィルタを介して高周波信号を入力し,

前記入力端子における入力インピーダンスが,前記帯域通過フィルタの出力インピーダンスと整合していることを特徴とする増幅器。 - 請求項3乃至6のいずれかにおいて,

さらに,前記イネーブル信号が供給される前は前記イネーブルスイッチを導通状態にし前記イネーブル信号が供給されてから所定時間経過後に前記イネーブルスイッチを非導通状態にするセットアップ信号を生成するセットアップ信号生成回路を有する増幅器。 - 入力端子にゲートが接続されソースが接地された第1のトランジスタと,

前記第1のトランジスタのドレイン側にカスコード接続され,ゲートに所定のバイアス電圧が供給されている第2のトランジスタと,

前記第2のトランジスタのドレインと電源との間に設けられた負荷抵抗素子と,

前記第2のトランジスタのドレインと前記負荷素子との間のノードに接続された出力端子と,

前記入力端子と出力端子との間に設けられ直列に接続された抵抗素子と容量素子とを有するフィードバック経路と,

イネーブル信号に応答して前記第1のトランジスタの前記ゲートにゲートバイアス電圧を印加するバイアス電圧生成回路と,

前記バイアス電圧生成回路の前記ゲートバイアス電圧の出力ノードと前記第1のトランジスタのゲートとの間に設けられた給電抵抗素子と,

前記ゲートバイアス電圧の前記出力ノードと,前記フィードバック経路内のノードとの間,または前記入力端子と前記第1のトランジスタのゲートの間の経路内のノードとの間に,前記イネーブル信号に応答して導通状態になり,通常動作状態で非導通状態になるイネーブルスイッチとを有する増幅器。 - 送受信端子と,

前記送受信端子に受信された受信信号を帯域フィルタを介して供給される受信側増幅器と,

出力信号を帯域フィルタを介して前記送受信端子に出力する送信側増幅器とを有する通信装置において,

前記受信側増幅器は,

前記受信信号を入力する入力端子と,

前記入力端子にゲートが接続されソースが接地された第1のトランジスタと,

前記第1のトランジスタのドレインと電源との間に設けられた負荷抵抗素子と,

前記第1のトランジスタのドレインと前記負荷素子との間のノードに接続された出力端子と,

前記入力端子と出力端子との間に設けられ抵抗素子と容量素子とを有するフィードバック経路と,

イネーブル信号に応答して前記第1のトランジスタのゲートにゲートバイアス電圧を印加するバイアス電圧生成回路と,

前記バイアス電圧生成回路の前記ゲートバイアス電圧の出力ノードと前記第1のトランジスタのゲートとの間に設けられた給電抵抗素子と,

前記ゲートバイアス電圧の前記出力ノードから前記フィードバック経路内のノードまでの抵抗値を,前記イネーブル信号に応答して低下させるイネーブルスイッチとを有する通信装置。 - 送受信端子と,

前記送受信端子に受信された受信信号を帯域フィルタを介して供給される受信側増幅器と,

出力信号を帯域フィルタを介して前記送受信端子に出力する送信側増幅器とを有する通信装置において,

前記受信側増幅器は,

前記受信信号を入力する入力端子と,

前記入力端子にゲートが接続されソースが接地された第1のトランジスタと,

前記第1のトランジスタのドレイン側にカスコード接続され,ゲートに所定のバイアス電圧が供給されている第2のトランジスタと,

前記第2のトランジスタのドレインと電源との間に設けられた負荷抵抗素子と,

前記第2のトランジスタのドレインと前記負荷素子との間のノードに接続された出力端子と,

前記入力端子と出力端子との間に設けられ直列に接続された抵抗素子と容量素子とを有するフィードバック経路と,

イネーブル信号に応答して前記第1のトランジスタのゲートにゲートバイアス電圧を印加するバイアス電圧生成回路と,

前記バイアス電圧生成回路の前記ゲートバイアス電圧の出力ノードと前記第1のトランジスタのゲートとの間に設けられた給電抵抗素子と,

前記ゲートバイアス電圧の前記出力ノードと,前記フィードバック経路内のノードとの間,または前記入力端子と前記第1のトランジスタのゲートの間の経路内のノードとの間に,前記イネーブル信号に応答して導通状態になり,通常動作状態で非導通状態になるイネーブルスイッチとを有する増幅器。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009026988A JP5245887B2 (ja) | 2009-02-09 | 2009-02-09 | 増幅器 |

| US12/702,349 US7956682B2 (en) | 2009-02-09 | 2010-02-09 | Amplifier |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009026988A JP5245887B2 (ja) | 2009-02-09 | 2009-02-09 | 増幅器 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010183473A true JP2010183473A (ja) | 2010-08-19 |

| JP5245887B2 JP5245887B2 (ja) | 2013-07-24 |

Family

ID=42539939

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2009026988A Active JP5245887B2 (ja) | 2009-02-09 | 2009-02-09 | 増幅器 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US7956682B2 (ja) |

| JP (1) | JP5245887B2 (ja) |

Cited By (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPWO2018154659A1 (ja) * | 2017-02-22 | 2019-12-12 | 住友電気工業株式会社 | バイアス回路 |

| WO2020203507A1 (ja) * | 2019-04-01 | 2020-10-08 | パナソニックセミコンダクターソリューションズ株式会社 | モノリシック半導体装置およびハイブリッド半導体装置 |

| US11177842B1 (en) | 2020-05-15 | 2021-11-16 | Samsung Electro-Mechanics Co., Ltd. | Radio-frequency switching circuit with damage detection of DC blocking capacitor |

| US11431296B2 (en) | 2020-05-22 | 2022-08-30 | Samsung Electro-Mechanics Co., Ltd. | Amplifying circuit and amplifying device with start-up function |

Families Citing this family (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN103546139A (zh) * | 2012-07-12 | 2014-01-29 | 联咏科技股份有限公司 | 偏压与负载电路及快速偏压电路与方法 |

| EP2760130B1 (en) * | 2013-01-28 | 2015-07-01 | Nxp B.V. | Bias circuit |

| JP5854289B2 (ja) * | 2013-11-11 | 2016-02-09 | 株式会社村田製作所 | 電力増幅モジュール |

| US20160079925A1 (en) | 2014-09-16 | 2016-03-17 | Texas Instruments Incorporated | Programmable filter in an amplifier |

| CN107636957A (zh) * | 2015-05-20 | 2018-01-26 | 怀斯迪斯匹有限公司 | 超低功率和低噪声放大器 |

| GB2545487A (en) * | 2015-12-18 | 2017-06-21 | Nordic Semiconductor Asa | Radio frequency receiver |

| US9755595B1 (en) * | 2016-04-15 | 2017-09-05 | Avago Technologies General Ip (Singapore) Pte. Ltd. | Settling time reduction for low noise amplifier |

| US10476454B2 (en) | 2016-09-21 | 2019-11-12 | Murata Manufacturing Co., Ltd. | Power amplifier module |

| JP2018050200A (ja) | 2016-09-21 | 2018-03-29 | 株式会社村田製作所 | 電力増幅モジュール |

| KR102075951B1 (ko) * | 2017-09-29 | 2020-02-11 | 가부시키가이샤 무라타 세이사쿠쇼 | 전력 증폭 회로 |

| CN111130467B (zh) * | 2020-01-09 | 2024-03-01 | 苏州大学 | 功率放大电路的自激振荡抑制装置和方法 |

| FR3107796B1 (fr) * | 2020-02-27 | 2022-03-25 | St Microelectronics Alps Sas | Dispositif de génération de signaux radiofréquence en quadrature de phase, utilisable en particulier dans la technologie 5G |

| US11128266B1 (en) * | 2020-07-29 | 2021-09-21 | Nxp B.V. | Amplifiers with feedback circuits |

| US11456711B2 (en) * | 2020-08-31 | 2022-09-27 | Taiwan Semiconductor Manufacturing Company, Ltd. | Measurement method using radio frequency power amplifier |

| US20240178798A1 (en) * | 2022-11-29 | 2024-05-30 | Psemi Corporation | Amplifier with Improved Power Supply Rejection in Feedback Circuits |

Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0284764A (ja) * | 1987-12-28 | 1990-03-26 | Mitsubishi Electric Corp | 半導体装置 |

| JPH04361410A (ja) * | 1991-06-10 | 1992-12-15 | Matsushita Electric Ind Co Ltd | 広帯域増幅装置 |

| JPH07202596A (ja) * | 1993-12-28 | 1995-08-04 | Fujitsu Ltd | 信号発生回路 |

| JP2005175819A (ja) * | 2003-12-10 | 2005-06-30 | Sony Corp | 増幅器並びに通信装置 |

Family Cites Families (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4940949A (en) * | 1989-11-01 | 1990-07-10 | Avantek, Inc. | High efficiency high isolation amplifier |

| JPH08148953A (ja) | 1994-11-16 | 1996-06-07 | Sanyo Electric Co Ltd | 増幅器及び通信装置 |

| JPH11112381A (ja) | 1997-09-30 | 1999-04-23 | Canon Inc | 無線装置及び無線装置における増幅制御方法 |

| US6498533B1 (en) * | 2000-09-28 | 2002-12-24 | Koninklijke Philips Electronics N.V. | Bootstrapped dual-gate class E amplifier circuit |

| US6987422B2 (en) * | 2003-05-15 | 2006-01-17 | Agilent Technologies, Inc. | Equal phase multiple gain state amplifier |

| JP4821214B2 (ja) | 2005-08-26 | 2011-11-24 | 三菱電機株式会社 | カスコード接続回路 |

| DE102006028093B4 (de) * | 2006-06-19 | 2014-07-03 | Austriamicrosystems Ag | Verstärkeranordnung und Verfahren zum Verstärken eines Signals |

| US20080297262A1 (en) * | 2007-05-31 | 2008-12-04 | Duster Jon S | Increased gain high-frequency amplifier |

-

2009

- 2009-02-09 JP JP2009026988A patent/JP5245887B2/ja active Active

-

2010

- 2010-02-09 US US12/702,349 patent/US7956682B2/en active Active

Patent Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0284764A (ja) * | 1987-12-28 | 1990-03-26 | Mitsubishi Electric Corp | 半導体装置 |

| JPH04361410A (ja) * | 1991-06-10 | 1992-12-15 | Matsushita Electric Ind Co Ltd | 広帯域増幅装置 |

| JPH07202596A (ja) * | 1993-12-28 | 1995-08-04 | Fujitsu Ltd | 信号発生回路 |

| JP2005175819A (ja) * | 2003-12-10 | 2005-06-30 | Sony Corp | 増幅器並びに通信装置 |

Cited By (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPWO2018154659A1 (ja) * | 2017-02-22 | 2019-12-12 | 住友電気工業株式会社 | バイアス回路 |

| WO2020203507A1 (ja) * | 2019-04-01 | 2020-10-08 | パナソニックセミコンダクターソリューションズ株式会社 | モノリシック半導体装置およびハイブリッド半導体装置 |

| US12183817B2 (en) | 2019-04-01 | 2024-12-31 | Nuvoton Technology Corporation Japan | Monolithic semiconductor device and hybrid semiconductor device |

| US11177842B1 (en) | 2020-05-15 | 2021-11-16 | Samsung Electro-Mechanics Co., Ltd. | Radio-frequency switching circuit with damage detection of DC blocking capacitor |

| US11431296B2 (en) | 2020-05-22 | 2022-08-30 | Samsung Electro-Mechanics Co., Ltd. | Amplifying circuit and amplifying device with start-up function |

Also Published As

| Publication number | Publication date |

|---|---|

| US7956682B2 (en) | 2011-06-07 |

| US20100201449A1 (en) | 2010-08-12 |

| JP5245887B2 (ja) | 2013-07-24 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5245887B2 (ja) | 増幅器 | |

| JP6567531B2 (ja) | 広帯域バイアス回路および方法 | |

| JPWO2015002294A1 (ja) | 電力増幅モジュール | |

| US7933575B2 (en) | Circuit for settling DC offset in direct conversion receiver | |

| JP5109895B2 (ja) | 増幅回路及び受信装置 | |

| US8433259B2 (en) | Gyrator circuit, wide-band amplifier and radio communication apparatus | |

| JP2007028613A (ja) | 自動振幅制御機能を有する電圧制御発振機 | |

| US20100289583A1 (en) | Variable gain rf amplifier | |

| JP5238604B2 (ja) | 電圧変換回路および無線通信装置 | |

| JP2009272864A (ja) | 信号処理回路 | |

| EP3254374A1 (en) | High bandwidth amplifier | |

| US9124229B2 (en) | Methods and systems to provide low noise amplification | |

| US8279000B2 (en) | Radio-frequency amplifier | |

| JP5139963B2 (ja) | 差動増幅器 | |

| CN109525211B (zh) | 放大器和包括所述放大器的无线信号接收器 | |

| US10270411B2 (en) | Amplifier | |

| JP2004023532A (ja) | 受信機における自動利得調整回路 | |

| JP2009171350A (ja) | ラジオ受信機およびこれに用いる受信用半導体集積回路 | |

| JP2007274179A (ja) | 同調回路及びこれに用いる可変利得減衰器 | |

| JP2008035203A (ja) | 電力増幅回路およびそれを用いた送信機ならびに送受信機 | |

| JP2007221663A (ja) | 放送信号受信装置 | |

| TWI407705B (zh) | 電流形式的無線接收系統及無線接收方法 | |

| JP2016158152A (ja) | 半導体装置 | |

| JP2010034944A (ja) | 高周波増幅回路 | |

| JP2004215168A (ja) | エミッタ接地増幅回路、移動無線端末装置および無線基地局装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20111104 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20120814 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120821 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20121017 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20130312 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20130325 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5245887 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20160419 Year of fee payment: 3 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |