KR100246162B1 - 주변 회로 내의 트랜지스터 형성 방법 - Google Patents

주변 회로 내의 트랜지스터 형성 방법 Download PDFInfo

- Publication number

- KR100246162B1 KR100246162B1 KR1019970704922A KR19970704922A KR100246162B1 KR 100246162 B1 KR100246162 B1 KR 100246162B1 KR 1019970704922 A KR1019970704922 A KR 1019970704922A KR 19970704922 A KR19970704922 A KR 19970704922A KR 100246162 B1 KR100246162 B1 KR 100246162B1

- Authority

- KR

- South Korea

- Prior art keywords

- polysilicon layer

- peripheral

- etching

- patterning

- memory cell

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

- H10B12/01—Manufacture or treatment

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B10/00—Static random access memory [SRAM] devices

- H10B10/12—Static random access memory [SRAM] devices comprising a MOSFET load element

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B10/00—Static random access memory [SRAM] devices

- H10B10/18—Peripheral circuit regions

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

- H10B12/01—Manufacture or treatment

- H10B12/02—Manufacture or treatment for one transistor one-capacitor [1T-1C] memory cells

- H10B12/05—Making the transistor

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

- H10B12/01—Manufacture or treatment

- H10B12/09—Manufacture or treatment with simultaneous manufacture of the peripheral circuit region and memory cells

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10S—TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10S257/00—Active solid-state devices, e.g. transistors, solid-state diodes

- Y10S257/903—FET configuration adapted for use as static memory cell

- Y10S257/904—FET configuration adapted for use as static memory cell with passive components,, e.g. polysilicon resistors

Landscapes

- Engineering & Computer Science (AREA)

- Manufacturing & Machinery (AREA)

- Semiconductor Memories (AREA)

Abstract

Description

Claims (13)

- 스태틱 랜덤 액세스 메모리 장치(SRAM)의 주변 회로 내에 트랜지스터를 형성하는 방법에 있어서,a. 상기 SRAM의 메모리 셀 어레이 영역 및 주변 영역의 기판 상부에 적어도 하나의 폴리실리콘층을 형성하는 단계; 및b. 상기 메모리 셀 어레이 영역 내에 부하 저항을 형성하는 것과 동시에 상기 주변 영역 내의 상기 폴리실리콘층(들)을 패터닝하고 에칭하여 주변 트랜지스터 게이트를 형성하는 단계를 포함하는 트랜지스터 형성 방법.

- 제1항에 있어서, 상기 메모리 셀 어레이 영역 내의 상기 적어도 하나의 폴리실리콘층을 패터닝하고 에칭하여 부하 저항의 형성을 완료하는 단계를 더 포함하되, 상기 주변 영역 내의 상기 폴리실리콘층(들)을 패터닝하고 에칭하는 단계는 상기 메모리 셀 어레이 영역 내의 상기 폴리실리콘층(들)을 패터닝하고 에칭하는 단계와 동시에, 그 일부로서 실시되는 트랜지스터 형성 방법.

- 스태틱 랜덤 액세스 메모리 장치(SRAM)의 주변 회로 내에 트랜지스터를 형성하는 방법에 있어서,a. 상기 SRAM의 메모리 셀 어레이 영역 및 주변 영역의 기판 상부에 적어도 하나의 폴리실리콘층을 형성하는 단계; 및b. 상기 메모리 셀 어레이 영역 내에 비트 라인 콘택 랜딩 패드(bitline contact landing pad)를 형성하는 것과 동시에 상기 주변 영역 내의 상기 폴리실리콘층(들)을 패터닝하고 에칭하여 주변 트랜지스터 게이트를 형성하는 단계를 포함하는 트랜지스터 형성 방법.

- 제3항에 있어서, 상기 메모리 셀 어레이 영역 내의 상기 적어도 하나의 폴리실리콘층을 패터닝하고 에칭하여 비트 라인 콘택 랜딩 패드를 형성하는 단계를 더 포함하되, 상기 주변 영역 내의 상기 폴리실리콘층(들)을 패터닝하고 에칭하는 단계는 상기 메모리 셀 어레이 영역 내의 상기 폴리실리콘층(들)을 패터닝하고 에칭하는 단계와 동시에, 그 일부로서 실시되는 트랜지스터 형성 방법.

- 스태틱 랜덤 액세스 메모리 장치(SRAM)의 주변 회로 내에 트랜지스터를 형성하는 방법에 있어서,a. 상기 SRAM의 메모리 셀 어레이 영역 및 주변 영역의 기판 상부에 적어도 하나의 폴리실리콘층을 형성하는 단계; 및b. 상기 메모리 셀 어레이 영역 내에 접지 라인을 형성하는 것과 동시에 상기 주변 영역 내의 상기 폴리실리콘층(들)을 패터닝하고 에칭하여 주변 트랜지스터 게이트를 형성하는 단계를 포함하는 트랜지스터 형성 방법.

- 제5항에 있어서, 상기 메모리 셀 어레이 영역 내의 상기 적어도 하나의 폴리실리콘층을 패터닝하고 에칭하여 접지 라인을 형성하는 단계를 더 포함하되, 상기 주변 영역 내의 상기 폴리실리콘층(들)을 패터닝하고 에칭하는 단계는 상기 메모리 셀 어레이 영역 내의 상기 폴리실리콘층(들)을 패터닝하고 에칭하는 단계와 동시에, 그 일부로서 실시되는 트랜지스터 형성 방법.

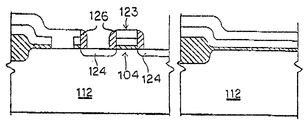

- 스태틱 랜덤 액세스 메모리 장치(SRAM)의 주변 회로 내에 트랜지스터를 형성하는 방법에 있어서,a. 상기 SRAM의 메모리 셀 어레이 영역 및 주변 영역의 기판 상부에 게이트 산화물층을 형성하는 단계;b. 원하는 매몰 콘택(buried contact) 위치에 상기 메모리 셀 어레이 영역 내의 상기 기판의 일부를 노출시키는 단계;c. 상기 노출된 기판 부분과 접촉되도록 상기 메모리 셀 어레이 영역 및 상기 주변 영역 내의 상기 기판 상부에 제1 폴리실리콘층을 형성하여 상기 매몰 콘택을 형성하는 단계;d. 상기 어레이 영역 내의 상기 제1 폴리실리콘층을 패터닝하고 에칭하여 메모리 트랜지스터 게이트들를 형성하고 상기 메모리 트랜지스터 게이트들에 인접한 상기 기판의 일부를 노출시키는 단계;e. 상기 어레이 영역 내의 상기 제1 폴리실리콘층 및 상기 기판의 노출 부분들 상부에 제1 절연층을 형성하는 단계;f. 상기 제1 절연층을 패터닝하고 에칭하여 원하는 비트 라인 콘택 랜딩 패드 위치에 상기 기판의 일부를 재노출시키는 단계;g. 상기 어레이 영역 내의 상기 제1 절연층 및 상기 재노출된 기판 부분들 상부 및 상기 주변 영역 내의 상기 제1 폴리실리콘층 상부에 제2 폴리실리콘층을 형성하는 단계;h. 상기 어레이 영역 내의 상기 제2 폴리실리콘층을 패터닝하고 에칭하여 비트 라인 콘택 랜딩 패드를 형성하는 단계;i. 상기 어레이 영역 내의 상기 제1 절연층 및 상기 제2 폴리실리콘층 상부에 제2 절연층을 형성하는 단계;j. 상기 메모리 셀 어레이 영역 내의 상기 제2 및 제1 절연층들을 패터닝하고 에칭하여 상기 매몰 콘택 상부의 원하는 노출 콘택(exhumed contact) 위치에 상기 제1 폴리실리콘층의 일부를 노출시키는 단계;k. 상기 어레이 영역 내의 상기 제2 절연층 및 상기 제1 폴리실리콘층의 노출 부분들 및 상기 주변 영역 내의 상기 제2 폴리실리콘층 상부에 제3 폴리실리콘층을 형성하는 단계; 및l. 상기 어레이 영역 내의 상기 제3 폴리실리콘층을 패터닝하고 에칭하여 상기 메몰 콘택에서 상기 기판과 접촉하는 상기 제2 폴리실리콘층과 접촉하는 상기 제3 폴리실리콘층을 포함하는 부하 저항을 형성하는 동시에, 상기 주변 영역 내의 상기 폴리실리콘층들을 패터닝하고 에칭하여 주변 트랜지스터 게이트를 형성하고 상기 주변 트랜지스터 게이트에 인접한 상기 기판의 일부를 노출시키는 단계를 포함하는 트랜지스터 형성 방법.

- 제7항에 있어서, 상기 주변 트랜지스터 게이트에 인접한 상기 기판의 노출 부분들 내에 불순물 도핑 영역들을 형성하여 상기 SRAM의 주변 영역에 주변 트랜지스터를 형성하는 단계를 더 포함하는 트랜지스터 형성 방법.

- 제7항에 있어서, 상기 단계들 (h)와 (l)은, 상기 주변 트랜지스터 게이트가 상기 어레이 영역 내의 상기 비트 라인 콘택 랜딩 패드의 형성과 동시에 형성되도록 조합되는 트랜지스터 형성 방법.

- 제8항에 있어서, 상기 주변 트랜지스터는 p 채널 트랜지스터인 트랜지스터 형성 방법.

- 다이내믹 랜덤 액세스 메모리 장치(DRAM)의 주변 회로 내에 트랜지스터를 형성하는 방법에 있어서,상기 DRAM의 메모리 셀 어레이 영역 및 주변 영역 내의 기판 상부에 게이트 산화물층, 및 상기 게이트 산화물층 상부의 적어도 하나의 폴리실리콘층을 형성하는 단계;상기 주변 영역 내의 상기 폴리실리콘층(들)을 패터닝하고 에칭하여 주변 트랜지스터 게이트를 형성하고 상기 주변 트랜지스터 게이트에 인접한 상기 기판의 일부를 노출시키는 단계; 및상기 노출된 기판 부분들 내에 불순물이 도핑된 소스 및 드레인 영역들을 형성하여 상기 DRAM의 주변 영역 내에 상기 주변 트랜지스터를 형성하는 단계를 포함하는 트랜지스터 형성 방법.

- 제11항에 있어서, 상기 주변 트랜지스터 게이트는 상기 메모리 셀 어레이 영역 내의 커패시터 전극의 형성과 동시에 형성되는 트랜지스터 형성 방법.

- 제12항에 있어서, 상기 메모리 셀 어레이 영역 내의 상기 적어도 하나의 폴리실리콘층을 패터닝하고 에칭하여 커패시터 전극을 형성하는 단계를 더 포함하되, 상기 주변 영역 내의 상기 폴리실리콘층(들)을 패터닝하고 에칭하는 단계는 상기 메모리 셀 어레이 영역 내의 상기 폴리실리콘층(들)을 패터닝하고 에칭하는 단계와 동시에, 그 일부로서 실시되는 트랜지스터 형성 방법.

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US37610395A | 1995-01-19 | 1995-01-19 | |

| US8/376103 | 1995-01-19 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR19980701531A KR19980701531A (ko) | 1998-05-15 |

| KR100246162B1 true KR100246162B1 (ko) | 2000-03-15 |

Family

ID=23483721

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1019970704922A Expired - Fee Related KR100246162B1 (ko) | 1995-01-19 | 1996-01-19 | 주변 회로 내의 트랜지스터 형성 방법 |

Country Status (6)

| Country | Link |

|---|---|

| US (3) | US6040209A (ko) |

| EP (1) | EP0804805B1 (ko) |

| JP (1) | JP3261435B2 (ko) |

| KR (1) | KR100246162B1 (ko) |

| DE (1) | DE69623440T2 (ko) |

| WO (1) | WO1996022612A1 (ko) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20210016641A (ko) * | 2018-08-23 | 2021-02-16 | 마이크론 테크놀로지, 인크 | 집적 회로 구성 |

Families Citing this family (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7064376B2 (en) * | 1996-05-24 | 2006-06-20 | Jeng-Jye Shau | High performance embedded semiconductor memory devices with multiple dimension first-level bit-lines |

| US20050036363A1 (en) * | 1996-05-24 | 2005-02-17 | Jeng-Jye Shau | High performance embedded semiconductor memory devices with multiple dimension first-level bit-lines |

| US5748547A (en) * | 1996-05-24 | 1998-05-05 | Shau; Jeng-Jye | High performance semiconductor memory devices having multiple dimension bit lines |

| EP0923116A1 (en) * | 1997-12-12 | 1999-06-16 | STMicroelectronics S.r.l. | Process for manufacturing integrated multi-crystal silicon resistors in MOS technology and integrated MOS device comprising multi-crystal silicon resistors |

| TW582095B (en) * | 2003-04-10 | 2004-04-01 | Nanya Technology Corp | Bit line contact and method for forming the same |

| KR100487563B1 (ko) * | 2003-04-30 | 2005-05-03 | 삼성전자주식회사 | 반도체 소자 및 그 형성 방법 |

| US7208369B2 (en) * | 2003-09-15 | 2007-04-24 | Taiwan Semiconductor Manufacturing Company, Ltd. | Dual poly layer and method of manufacture |

| KR100701697B1 (ko) * | 2005-06-29 | 2007-03-29 | 주식회사 하이닉스반도체 | 듀얼 폴리사이드 게이트를 갖는 씨모스 소자의 제조방법 |

Family Cites Families (22)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS53124084A (en) * | 1977-04-06 | 1978-10-30 | Hitachi Ltd | Semiconductor memory device containing floating type poly silicon layer and its manufacture |

| US4408385A (en) * | 1978-06-15 | 1983-10-11 | Texas Instruments Incorporated | Semiconductor integrated circuit with implanted resistor element in polycrystalline silicon layer |

| US4370798A (en) * | 1979-06-15 | 1983-02-01 | Texas Instruments Incorporated | Interlevel insulator for integrated circuit with implanted resistor element in second-level polycrystalline silicon |

| US5352620A (en) * | 1984-05-23 | 1994-10-04 | Hitachi, Ltd. | Method of making semiconductor device with memory cells and peripheral transistors |

| EP0272433B1 (de) * | 1986-11-18 | 1993-03-31 | Siemens Aktiengesellschaft | Integrierte Halbleiterschaltung mit als Dünnschichtstege auf den die aktiven Transistorbereiche trennenden Feldoxidbereichen angeordneten Lastwiderstände und Verfahren zu ihrer Herstellung |

| JPH02122563A (ja) * | 1988-10-31 | 1990-05-10 | Nec Corp | 半導体装置の製造方法 |

| JPH03259566A (ja) * | 1990-02-02 | 1991-11-19 | Sony Corp | メモリ装置の製造方法 |

| US5281838A (en) | 1990-03-13 | 1994-01-25 | Mitsubishi Denki Kabushiki Kaisha | Semiconductor device having contact between wiring layer and impurity region |

| US5276344A (en) * | 1990-04-27 | 1994-01-04 | Mitsubishi Denki Kabushiki Kaisha | Field effect transistor having impurity regions of different depths and manufacturing method thereof |

| JPH0834304B2 (ja) * | 1990-09-20 | 1996-03-29 | 富士通株式会社 | 半導体装置およびその製造方法 |

| JP2666549B2 (ja) * | 1990-09-27 | 1997-10-22 | 日本電気株式会社 | 半導体記憶装置及びその製造方法 |

| JPH04165670A (ja) * | 1990-10-30 | 1992-06-11 | Toshiba Corp | 半導体記憶装置とその製造方法 |

| JPH04186877A (ja) * | 1990-11-21 | 1992-07-03 | Fujitsu Ltd | 半導体装置の製造方法 |

| JPH04322459A (ja) * | 1991-04-23 | 1992-11-12 | Nec Corp | 半導体記憶装置およびその製造方法 |

| US5327002A (en) | 1991-05-15 | 1994-07-05 | Kawasaki Steel Corporation | SRAM with gate oxide films of varied thickness |

| JPH0521805A (ja) * | 1991-07-10 | 1993-01-29 | Fujitsu Ltd | 半導体装置の製造方法 |

| JPH05121700A (ja) * | 1991-08-28 | 1993-05-18 | Fujitsu Ltd | 半導体装置及びその製造方法 |

| JP3548984B2 (ja) * | 1991-11-14 | 2004-08-04 | 富士通株式会社 | 半導体装置の製造方法 |

| JP2705476B2 (ja) * | 1992-08-07 | 1998-01-28 | ヤマハ株式会社 | 半導体装置の製造方法 |

| US5500387A (en) * | 1994-02-16 | 1996-03-19 | Texas Instruments Incorporated | Method of making high performance capacitors and/or resistors for integrated circuits |

| JPH09270461A (ja) * | 1996-03-29 | 1997-10-14 | Mitsubishi Electric Corp | 半導体装置 |

| US5808335A (en) * | 1996-06-13 | 1998-09-15 | Vanguard International Semiconductor Corporation | Reduced mask DRAM process |

-

1996

- 1996-01-19 WO PCT/US1996/000615 patent/WO1996022612A1/en not_active Ceased

- 1996-01-19 KR KR1019970704922A patent/KR100246162B1/ko not_active Expired - Fee Related

- 1996-01-19 EP EP96904473A patent/EP0804805B1/en not_active Expired - Lifetime

- 1996-01-19 JP JP52236696A patent/JP3261435B2/ja not_active Expired - Fee Related

- 1996-01-19 DE DE69623440T patent/DE69623440T2/de not_active Expired - Lifetime

-

1997

- 1997-01-21 US US08/786,175 patent/US6040209A/en not_active Expired - Fee Related

-

1998

- 1998-10-14 US US09/173,038 patent/US6252268B1/en not_active Expired - Fee Related

-

1999

- 1999-12-07 US US09/456,140 patent/US6271073B1/en not_active Expired - Fee Related

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20210016641A (ko) * | 2018-08-23 | 2021-02-16 | 마이크론 테크놀로지, 인크 | 집적 회로 구성 |

| KR102359065B1 (ko) | 2018-08-23 | 2022-02-08 | 마이크론 테크놀로지, 인크 | 집적 회로 구성 |

Also Published As

| Publication number | Publication date |

|---|---|

| JPH10505712A (ja) | 1998-06-02 |

| US6040209A (en) | 2000-03-21 |

| US6252268B1 (en) | 2001-06-26 |

| WO1996022612A1 (en) | 1996-07-25 |

| DE69623440T2 (de) | 2003-08-07 |

| DE69623440D1 (de) | 2002-10-10 |

| EP0804805A1 (en) | 1997-11-05 |

| US6271073B1 (en) | 2001-08-07 |

| EP0804805B1 (en) | 2002-09-04 |

| JP3261435B2 (ja) | 2002-03-04 |

| KR19980701531A (ko) | 1998-05-15 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US8629533B2 (en) | Pillars for vertical transistors | |

| US4075045A (en) | Method for fabricating FET one-device memory cells with two layers of polycrystalline silicon and fabrication of integrated circuits containing arrays of the memory cells charge storage capacitors utilizing five basic pattern deliberating steps | |

| US4183040A (en) | MOS RAM with implant forming peripheral depletion MOSFET channels and capacitor bottom electrodes | |

| US4095251A (en) | Field effect transistors and fabrication of integrated circuits containing the transistors | |

| KR0128826B1 (ko) | 디램셀 제조방법 | |

| KR100246162B1 (ko) | 주변 회로 내의 트랜지스터 형성 방법 | |

| US5283204A (en) | Method of forming passivation oxidation for improving cell leakage and cell area | |

| US6479355B2 (en) | Method for forming landing pad | |

| US6080609A (en) | Method of making MOSFET structure | |

| KR930015002A (ko) | 반도체 메모리 장치 및 그 제조방법 | |

| JPH04216665A (ja) | 半導体メモリ素子の製造方法 | |

| US5691221A (en) | Method for manufacturing semiconductor memory device having a stacked capacitor | |

| KR100390891B1 (ko) | 고집적반도체소자의제조방법 | |

| KR0169599B1 (ko) | 반도체소자 및 그 제조방법 | |

| KR970011758B1 (ko) | 반도체 집적회로의 전도막 형성방법 | |

| KR100281038B1 (ko) | 반도체 메모리장치 제조방법 | |

| KR100223895B1 (ko) | Dram 셀 및 그 제조 방법 | |

| KR0156169B1 (ko) | 반도체 메모리장치 제조방법 | |

| KR0131741B1 (ko) | 반도체 기억장치 및 그 제조방법 | |

| KR930009589B1 (ko) | 고집적 모스소자의 커패시터 제조방법 | |

| KR0126114B1 (ko) | 반도체 메모리 장치 제조방법 | |

| KR19990005489A (ko) | 반도체 장치 제조방법 | |

| KR20000041808A (ko) | 반도체장치의 캐패시터 제조방법 | |

| KR19990003042A (ko) | 반도체 소자의 캐패시터 형성방법 | |

| KR19980026302A (ko) | 반도체 메모리 장치의 제조 방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A201 | Request for examination | ||

| PA0105 | International application |

St.27 status event code: A-0-1-A10-A15-nap-PA0105 |

|

| PA0201 | Request for examination |

St.27 status event code: A-1-2-D10-D11-exm-PA0201 |

|

| R17-X000 | Change to representative recorded |

St.27 status event code: A-3-3-R10-R17-oth-X000 |

|

| PG1501 | Laying open of application |

St.27 status event code: A-1-1-Q10-Q12-nap-PG1501 |

|

| R18-X000 | Changes to party contact information recorded |

St.27 status event code: A-3-3-R10-R18-oth-X000 |

|

| PN2301 | Change of applicant |

St.27 status event code: A-3-3-R10-R13-asn-PN2301 St.27 status event code: A-3-3-R10-R11-asn-PN2301 |

|

| R18-X000 | Changes to party contact information recorded |

St.27 status event code: A-3-3-R10-R18-oth-X000 |

|

| E701 | Decision to grant or registration of patent right | ||

| PE0701 | Decision of registration |

St.27 status event code: A-1-2-D10-D22-exm-PE0701 |

|

| GRNT | Written decision to grant | ||

| PR0701 | Registration of establishment |

St.27 status event code: A-2-4-F10-F11-exm-PR0701 |

|

| PR1002 | Payment of registration fee |

St.27 status event code: A-2-2-U10-U12-oth-PR1002 Fee payment year number: 1 |

|

| PG1601 | Publication of registration |

St.27 status event code: A-4-4-Q10-Q13-nap-PG1601 |

|

| PR1001 | Payment of annual fee |

St.27 status event code: A-4-4-U10-U11-oth-PR1001 Fee payment year number: 4 |

|

| PR1001 | Payment of annual fee |

St.27 status event code: A-4-4-U10-U11-oth-PR1001 Fee payment year number: 5 |

|

| PR1001 | Payment of annual fee |

St.27 status event code: A-4-4-U10-U11-oth-PR1001 Fee payment year number: 6 |

|

| PR1001 | Payment of annual fee |

St.27 status event code: A-4-4-U10-U11-oth-PR1001 Fee payment year number: 7 |

|

| PR1001 | Payment of annual fee |

St.27 status event code: A-4-4-U10-U11-oth-PR1001 Fee payment year number: 8 |

|

| PR1001 | Payment of annual fee |

St.27 status event code: A-4-4-U10-U11-oth-PR1001 Fee payment year number: 9 |

|

| PR1001 | Payment of annual fee |

St.27 status event code: A-4-4-U10-U11-oth-PR1001 Fee payment year number: 10 |

|

| PR1001 | Payment of annual fee |

St.27 status event code: A-4-4-U10-U11-oth-PR1001 Fee payment year number: 11 |

|

| FPAY | Annual fee payment |

Payment date: 20101124 Year of fee payment: 12 |

|

| PR1001 | Payment of annual fee |

St.27 status event code: A-4-4-U10-U11-oth-PR1001 Fee payment year number: 12 |

|

| R18-X000 | Changes to party contact information recorded |

St.27 status event code: A-5-5-R10-R18-oth-X000 |

|

| LAPS | Lapse due to unpaid annual fee | ||

| PC1903 | Unpaid annual fee |

St.27 status event code: A-4-4-U10-U13-oth-PC1903 Not in force date: 20111204 Payment event data comment text: Termination Category : DEFAULT_OF_REGISTRATION_FEE |

|

| PC1903 | Unpaid annual fee |

St.27 status event code: N-4-6-H10-H13-oth-PC1903 Ip right cessation event data comment text: Termination Category : DEFAULT_OF_REGISTRATION_FEE Not in force date: 20111204 |

|

| P22-X000 | Classification modified |

St.27 status event code: A-4-4-P10-P22-nap-X000 |

|

| P22-X000 | Classification modified |

St.27 status event code: A-4-4-P10-P22-nap-X000 |

|

| P22-X000 | Classification modified |

St.27 status event code: A-4-4-P10-P22-nap-X000 |