JP2004201320A - 高品質直列共振発振器 - Google Patents

高品質直列共振発振器 Download PDFInfo

- Publication number

- JP2004201320A JP2004201320A JP2003418164A JP2003418164A JP2004201320A JP 2004201320 A JP2004201320 A JP 2004201320A JP 2003418164 A JP2003418164 A JP 2003418164A JP 2003418164 A JP2003418164 A JP 2003418164A JP 2004201320 A JP2004201320 A JP 2004201320A

- Authority

- JP

- Japan

- Prior art keywords

- circuit

- signal

- oscillation

- output

- input terminal

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

- 230000010355 oscillation Effects 0.000 claims abstract description 80

- 238000000034 method Methods 0.000 claims abstract description 25

- 230000003321 amplification Effects 0.000 claims abstract description 13

- 238000003199 nucleic acid amplification method Methods 0.000 claims abstract description 13

- 230000000694 effects Effects 0.000 claims abstract description 10

- 239000013078 crystal Substances 0.000 claims description 69

- 239000003990 capacitor Substances 0.000 claims description 21

- 238000005516 engineering process Methods 0.000 claims description 14

- 230000008878 coupling Effects 0.000 claims description 6

- 238000010168 coupling process Methods 0.000 claims description 6

- 238000005859 coupling reaction Methods 0.000 claims description 6

- 230000008569 process Effects 0.000 claims description 4

- 230000008859 change Effects 0.000 claims description 3

- 230000000087 stabilizing effect Effects 0.000 claims description 3

- 230000001052 transient effect Effects 0.000 claims description 3

- 238000001914 filtration Methods 0.000 claims description 2

- 238000000926 separation method Methods 0.000 claims 3

- 238000010586 diagram Methods 0.000 abstract description 24

- 238000002955 isolation Methods 0.000 abstract description 4

- 230000008901 benefit Effects 0.000 description 10

- 238000013461 design Methods 0.000 description 9

- 239000010453 quartz Substances 0.000 description 9

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N silicon dioxide Inorganic materials O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 9

- 238000004088 simulation Methods 0.000 description 9

- 230000006870 function Effects 0.000 description 6

- 238000005259 measurement Methods 0.000 description 5

- 238000001514 detection method Methods 0.000 description 4

- 238000004519 manufacturing process Methods 0.000 description 4

- 239000010409 thin film Substances 0.000 description 4

- 238000013459 approach Methods 0.000 description 3

- 230000003071 parasitic effect Effects 0.000 description 3

- 230000010363 phase shift Effects 0.000 description 3

- 238000012546 transfer Methods 0.000 description 3

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 2

- 230000003139 buffering effect Effects 0.000 description 2

- 239000000919 ceramic Substances 0.000 description 2

- 238000005094 computer simulation Methods 0.000 description 2

- 230000009467 reduction Effects 0.000 description 2

- 229910052710 silicon Inorganic materials 0.000 description 2

- 239000010703 silicon Substances 0.000 description 2

- 238000012360 testing method Methods 0.000 description 2

- 238000004364 calculation method Methods 0.000 description 1

- 230000015556 catabolic process Effects 0.000 description 1

- 238000004891 communication Methods 0.000 description 1

- 238000010276 construction Methods 0.000 description 1

- 238000006731 degradation reaction Methods 0.000 description 1

- 230000001419 dependent effect Effects 0.000 description 1

- 230000001627 detrimental effect Effects 0.000 description 1

- 230000005669 field effect Effects 0.000 description 1

- 230000002452 interceptive effect Effects 0.000 description 1

- 239000000463 material Substances 0.000 description 1

- 230000004044 response Effects 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03B—GENERATION OF OSCILLATIONS, DIRECTLY OR BY FREQUENCY-CHANGING, BY CIRCUITS EMPLOYING ACTIVE ELEMENTS WHICH OPERATE IN A NON-SWITCHING MANNER; GENERATION OF NOISE BY SUCH CIRCUITS

- H03B5/00—Generation of oscillations using amplifier with regenerative feedback from output to input

- H03B5/30—Generation of oscillations using amplifier with regenerative feedback from output to input with frequency-determining element being electromechanical resonator

- H03B5/32—Generation of oscillations using amplifier with regenerative feedback from output to input with frequency-determining element being electromechanical resonator being a piezoelectric resonator

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03B—GENERATION OF OSCILLATIONS, DIRECTLY OR BY FREQUENCY-CHANGING, BY CIRCUITS EMPLOYING ACTIVE ELEMENTS WHICH OPERATE IN A NON-SWITCHING MANNER; GENERATION OF NOISE BY SUCH CIRCUITS

- H03B5/00—Generation of oscillations using amplifier with regenerative feedback from output to input

- H03B5/30—Generation of oscillations using amplifier with regenerative feedback from output to input with frequency-determining element being electromechanical resonator

- H03B5/32—Generation of oscillations using amplifier with regenerative feedback from output to input with frequency-determining element being electromechanical resonator being a piezoelectric resonator

- H03B5/36—Generation of oscillations using amplifier with regenerative feedback from output to input with frequency-determining element being electromechanical resonator being a piezoelectric resonator active element in amplifier being semiconductor device

Landscapes

- Oscillators With Electromechanical Resonators (AREA)

Abstract

【解決手段】安定した所定の発振周波数を有する発振信号を生成するための手段100と、発振生成手段を駆動し且つ発振生成手段とこの駆動手段の間のインピーダンスレベルを整合させるための手段と、発振生成手段の生成発振信号を増幅し且つ制御するための手段130と、増幅および制御手段を、閉ループ帰還方式で前記駆動手段に接続するための手段105と、駆動手段と前記増幅手段の間に結合された、安定した発振信号が維持されるよう、増幅手段の増幅率(利得)を制御するための手段140と、増幅手段の前記増幅発振信号を分離するための手段であって、増幅発振信号を前記分離手段の出力負荷の変化による影響から分離する手段150と、電源電圧のレベルに基づいて、駆動手段および前記分離手段のためのバイアス電流を生成する手段160と、を備える。

【選択図】 図1

Description

米国特許(Feistelらに対する第3,996,530号)に、電圧増幅段とインピーダンス整合段の間に挿入されたフィルタ回路網を後段に備える振幅制限増幅器を有するバトラー発振器が記述されている。このバトラー発振器は、最大周波数安定性を保証するために、電圧増幅段およびインピーダンス整合段の両方の線形モードでの動作を常時可能にし、それにより、電圧増幅段とインピーダンス整合段の間に接続された圧電性結晶の、比較的小さい定インピーダンス経路内への接続、およびひずみのない正弦波による駆動を保証している。本発明による回路は、バイポーラ技術を使用して実現されている。

ここでは[Vittozらの「弱い反転動作に基づくCMOSアナログ集積回路(CMOS Analog Integrated Circuits Based on Weak Inversion Operation)」、IEEE Journal of Solid−State Circuits、vol.SC−12、No.3、1977年6月、224〜231頁]として記載されているVittozらの論文に、自動利得制御回路が記述されているが、この回路の同調微小帯域動作の欠点は、本発明では回避されている。

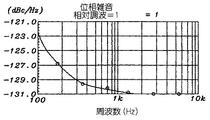

本発明のさらに他の目的は、位相雑音の小さい回路挙動に到達すること、つまりその周波数安定性を十分に高めることである。

本発明の他の目的は、定常状態動作における生成発振信号のひずみおよび位相雑音を最小化することである。

本発明のさらに他の目的は、回路を低コストCMOS技術におけるモノリシック集積回路として実施することによって、製造コストを低減することである。

本発明の好ましい実施形態について、第1段階の回路全体についての総合的な説明およびすべての機能回路ブロックについての簡単な説明と、第2段階の、正確な回路図に照らして行う前記機能回路ブロックの各々についての非常に詳細な説明の2段階に細分して説明する。

このブロックは、ここでは特定の事例として選択された水晶(XTAL)共振子を表しているが、一般的には任意のタイプの共振子(TFR、MEMS等)を使用することができ、また、通常、いわゆるオフチップ部品として集積回路に外部接続することができる。しかしながら、低コスト解決策のためには、回路の動作の安定性が幾分か悪くなるが、オンチップ集積共振子デバイスを使用することも可能である。

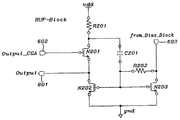

長方形の破線に囲まれた回路ブロック10は、発振器に必須の基本的な部分であり、発振器のコアとして設計されている。この回路は、Butlerによって最初に提案された[F.Butler、「直列共振水晶発振器(Series−Resonant Crystal Oscillators)」、Wireless Engineer、1946年6月、157〜160ページ]もので、ここでは修正されている。

自動利得制御のための回路ブロックには、以下に示す機能が含まれている。

a)発振器信号の定電圧振幅を維持する

b)周波数の不安定性すなわち位相雑音による周波数変調の副作用と考えることができる発振器信号の振幅変調を防止し、発振器の高速スタートアッププロセスを保証し、かつ、主増幅トランジスタの零入力電流(MOSFETの相互コンダクタンスgmによって決まる)を一定に維持する。相互コンダクタンスgmは、[S]をユニットとして、gm=ΔlD/ΔVGSで定義される。lDはDCドレイン電流であり、VGSは、電界効果トランジスタ(FET)のDCゲート−ソース電圧である。また、これは、gm=ld/VgsとしてAC量で表すこともできる。項を再配列すると、ld=gm *Vgs([S]=ジーメンス=1/オーム=1/[Ω])が得られる。

出力バッファBUFは、必要な出力電力を有する負荷を生成正弦波発振器信号に供給するためのものである。この回路ブロックのもう1つの主な目的は、発振器のコアと負荷を分離することである。このコンテキストにおいては、分離は、出力負荷の変動が生成発振器信号に影響しないことを意味している。バッファの出力インピーダンスを小さくし、かつ、必要な負荷を駆動するだけの十分な電力を引き渡す機能を持たせなければならないのは、この理由によるものである。また、システムへの余計な位相雑音の付加を回避するためには、バッファの直線性が良好であり、かつ、雑音が小さいことが肝要である。電気回路図については、図6を参照されたい。

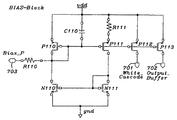

バイアス回路ブロックは基準電流を生成している。この基準電流は、ホワイトカスコードバッファWCB109をバイアスするため、および出力バッファBUF110をバイアスするためにさらに使用される。電気回路図については、図7を参照されたい。

L0、C0およびR0が水晶の直列共振周波数を決定し、

L0、C0、R0およびC1が並列共振周波数を決定し、また、

C2およびC3は、水晶のプレート寄生およびパーケージ寄生の接地に対する寄生容量を表している。

物理的現象をより明察し、かつ、感覚的に展開するために、水晶の製造者が提示しているコンポーネントおよびそれらの典型的な数値を示しておく。

C0 =5.188 [fF]

R0 =11.24 [Ω]

C1 =1 [pF]

C2、C3 =1 [pF]

(最後の2つの容量C2およびC3の影響は、それらが端子対X1−X0およびX2−X0に並列に接続されているため、無視されることが非常に多い。)

直列共振周波数におけるインピーダンスは純抵抗性であり、R0に等しい。直列共振周波数における位相シフトは、ゼロに等しい(発振の位相条件を満足するためには重要である)。13MHzより高い周波数に対する等価インピーダンスは、C1によって決まる容量性特性のインピーダンスである。そのコンテキストにおける最も重要なことは、インピーダンスの絶対値が減少していることであり、これを適切に考慮しない場合、例えばひずみによる高周波信号が水晶自身を介して送信されることになる。発振器のコアは、このような高周波成分が生成されないこと、あるいは送信されないこと、もしくは増幅されないことを保証しなければならない。つまり、高い周波数においては根本的に発振の可能性が存在しているが、発振器コア回路は、発振(振幅および位相−上記参照)のための少なくとも1つの条件が、妥当な安全限界内で満足しないことを保証しなければならない。

図中の破線は、ホワイトカスコードバッファWCB(図の左側のアイテム410)および共通ゲート増幅器CGA(図の右側のアイテム420)の2つのブロックを囲っている。水晶共振子400は、ホワイトカスコードバッファWCBの出力部と共通ゲート増幅器CGAの入力部の間に接続されている。バッファWCBおよび増幅器CGAは、XT1とXT2の間の電圧である信号に余計な位相シフトをもたらさないため(理想的な成分を保証している)、XTALが同じ位相を信号として維持している場合、発振のための位相条件のみが満足することになる。つまり、これは、水晶が直列共振モードで動作し、したがって純抵抗性インピーダンスを示している場合にのみ可能である。発振のための振幅条件の合致については、共通ゲート増幅器CGAの利得を制御することによって保証されている。

トランジスタ化(バイポーラ)されたオリジナルトポロジーによるエミッタフォロワがホワイトカスコードバッファWCBに置換され、低出力インピーダンスを提供している。また、バッファWCBと増幅器段CGAの間の結合が直接DC結合として実施されている。オリジナル回路のコンデンサは回避されている。オリジナル構造が固定利得であり、振幅制限器であるのに対し、増幅器利得のアナログおよび連続アクティブ制御が実施されている。また、ホワイトカスコードコンデンサ(Cwc)のサイズが有効に縮小されている。

自動利得制御AGCに使用されているトポロジーの主な利点は、主として、総電流消費が非常に小さいμA程度の電圧制御可能電流を生成する可能性である。もう1つの利点は、広範囲にわたる周波数レンジで動作する可能性である。

本発明による構造の最も重要な利点は、電流基準をセットアップしている間の電流損失が非常に小さいことである。ホワイトカスコードバッファWCBおよび出力バッファBUFのための基準電流は、3つのPMOSトランジスタP110、P112およびP113からなる電流ミラーシステムを使用して生成される。抵抗R110は、試験用にのみ使用される外部ピンBIAS_P703への接続を提供している。コンデンサC110は、PMOSトランジスタのすべてのゲートをAC接地することによって、発振器からもたらされる妨害を防止している。

図8Aを参照すると、発振器コア内で生成される信号(output_CGA;図4のアイテム401)をコンピュータシミュレーションした結果が示されている。驚くべきことに、上で既に言及したように、利得が固定され、かつ、信号がクリップされる回路の結果と比較すると、正弦波信号に非常に良好に近似している。

120 ホワイトカスコードバッファ

130 共通ゲート増幅器

140 自動利得制御

150 出力バッファ

160 バイアス回路

Claims (44)

- 安定した所定の発振周波数を有する発振信号を生成するための手段と、

前記発振生成手段を駆動し、且つ、前記発振生成手段とこの駆動手段の間のインピーダンスレベルを整合させるための手段と、

前記発振生成手段の生成発振信号を増幅し且つ制御するための手段と、

前記増幅および制御手段を、閉ループ帰還方式で前記駆動手段に接続するための手段と、

前記駆動手段と前記増幅手段の間に結合され、安定した発振信号が維持されるよう、前記増幅手段の増幅率(利得)を制御するための手段と、

前記増幅手段の前記増幅発振信号を分離するための手段であって、前記増幅発振信号を前記分離手段の出力負荷の変化による影響から分離する手段と、

電源電圧のレベルに基づいて、前記駆動手段および前記分離手段のためのバイアス電流を生成する手段と、

を備える共振子制御発振器出力信号を生成することができる回路。 - 前記発振生成手段は、所定の発振周波数を有する発振信号を生成する水晶共振子素子を有する共振子回路を備える、請求項1に記載の回路。

- 前記水晶共振子素子は直列共振モードで動作し、したがって共振周波数において純抵抗性インピーダンス値を示す、請求項2に記載の回路。

- 前記発振生成手段は、MEMS技術を使用して製造された共振子回路を備える、請求項1に記載の回路。

- 前記増幅手段は共通ゲート増幅器回路を備える、請求項1に記載の回路。

- 2つの共通ゲートNMOSトランジスタと、

2つのDC接地抵抗と、

1つのDC接地共通ゲートコンデンサと、

さらに1つの抵抗と、

アナログおよび増幅器回路の連続調整可能利得のための制御された基準電流源とを備える前記共通ゲート増幅器が組み込まれる、請求項5に記載の回路。 - 前記増幅手段は、1対の信号端子と同じくバイアス電流端子として使用される1つの制御端子とを備える、請求項1に記載の回路。

- 前記増幅手段が、

1つが信号入力端子であり、もう1つが制御入力端子である2つの入力端子、および1つの出力端子を備える、前記発振生成手段からその信号入力端子に供給され、かつ、その出力端子に伝達される前記生成発振信号を増幅するための共通ゲート増幅器回路であって、制御入力端子が前記制御手段の出力信号によって制御される共通ゲート増幅器回路と、

付加的に必要な電流基準のための1つのバイアス電流端子とを備える、請求項1に記載の回路。 - 前記制御手段は自動利得制御回路を備える、請求項1に記載の回路。

- 自己バイアス電流源のための2つのNMOSトランジスタおよび2つのPMOSトランジスタと、

フィルタリング、バイアスおよび減結合のための3つの抵抗および3つのコンデンサと、

増幅器利得制御電流を供給するためのさらに1つのPMOSトランジスタとを備える前記自動利得コントローラが組み込まれる、請求項9に記載の回路。 - 前記制御手段は、1つが信号入力用であり、他方が信号出力用である2つの信号端子を備える、請求項1に記載の回路。

- 前記制御手段は、1つの入力端子および1つの出力端子を備える自動利得制御回路を備え、前記入力端子は、前記増幅手段の出力端子と共に前記駆動手段の入力端子である他の2つの端子から接続され、また、前記出力端子は前記増幅手段の制御入力端子に接続される、請求項1に記載の回路。

- 前記バイアス手段は専用バイアス回路ブロックを備える、請求項1に記載の回路。

- 電流ミラーシステムを形成する、2つのDC接地NMOSトランジスタおよび3つのAC接地PMOSトランジスタと、

非線形弱反転モードで動作するさらに1つのPMOSトランジスタと、

1つの負帰還抵抗と、

1つのAC接地コンデンサとを備える前記バイアスブロックを実現する、請求項13に記載の回路。 - 前記バイアス手段は2つのバイアス電流出力端子を備える、請求項1に記載の回路。

- 前記バイアス手段は、

前記駆動手段のための電流基準をセットアップする一方の出力端子と、前記分離手段のための電流基準をセットアップする他方の出力端子との2つの出力端子を備えるバイアス回路ブロックを備える、請求項1に記載の回路。 - 前記駆動手段はホワイトカスコードバッファ回路を備える、請求項1に記載の回路。

- 2つのDC接地NMOSトランジスタと、

1つのカスコードNMOSトランジスタと、

2つの抵抗および1つのホワイトカスコードコンデンサと、

バイアスのための基準電流源とを備える前記ホワイトカスコードバッファを実現する、請求項17に記載の回路。 - 使用可能周波数レンジを拡張し、かつ、チップ面積を節約するために、前記ホワイトカスコードコンデンサは有効に最小化される、請求項18に記載の回路。

- 回路の動作のための前記使用可能周波数レンジは、1MHzから約50MHzまで拡張される、請求項19に記載の回路。

- 前記駆動手段は、1対の信号端子および1つのバイアス電流端子を備える、請求項1に記載の回路。

- 前記駆動手段は、

1つの信号入力端子および1つの信号出力端子を備え、その出力端子上で前記発振信号を生成するために発振生成手段を駆動するためのホワイトカスコードバッファ回路であって、入力端子が最初に前記接続手段を介して前記増幅手段の入力端子に接続され、次に前記制御手段の入力端子に接続されたホワイトカスコードバッファ回路と、

付加的に必要な電流基準のための1つのバイアス電流端子とを備える、請求項1に記載の回路。 - 前記分離手段は出力バッファ回路を備える、請求項1に記載の回路。

- 電流ミラー回路を形成する2つのDC接地NMOSトランジスタと、

信号出力を増幅するためのさらに1つのNMOSトランジスタと、

2つの抵抗および1つのホワイトカスコードコンデンサと、

バイアスのための基準電流源とを備える前記出力バッファを実現する、請求項23に記載の回路。 - 電流消費を最少化するために、電流ミラー内の電流比を可能な限り小さくする(例えば1:10)、請求項24に記載の回路。

- 使用可能周波数レンジを拡張し且つチップ面積を節約するために、前記ホワイトカスコードコンデンサは有効に最小化される、請求項24に記載の回路。

- 回路の動作のための前記使用可能周波数レンジが、1MHzから約50MHzまで拡張された、請求項26に記載の回路。

- 前記分離手段は、信号入力用の一方と信号出力用の他方の2つの信号端子、および1つのバイアス電流端子を備える、請求項1に記載の回路。

- 前記分離手段は、

1つの入力端子および1つの出力端子を備え、前記入力端子には前記増幅手段の出力端子の前記発振信号が供給され、出力端子自身が発振器回路全体の出力端子を形成している出力バッファ回路と、

付加的に必要な電流基準のための1つのバイアス電流端子とを備える、請求項1に記載の回路。 - 前記接続手段は、前記増幅手段の出力端子から、最初に前記駆動手段の入力端子まで次に前記利得制御手段の入力端子までの内部帰還ループとしての直接接続リードを備える、請求項1に記載の回路。

- 前記内部帰還ループ接続は直接DC結合として実現され、容量コンポーネントが実質的に回避される、請求項29に記載の回路。

- 前記発振生成手段、また前記駆動手段、さらに前記増幅手段は、

所定の発振周波数を有する発振信号を生成する水晶共振子素子を有する共振子回路と、

1つの信号入力と1つの制御入力をの2つの入力端子、前記発振生成手段から当該信号入力端子に供給されそして当該出力端子に伝送される前記生成発振信号を増幅するための1つの出力端子を備え、前記制御入力端子は前記制御手段の出力信号によって制御される、共通ゲート増幅器回路と、

1つの入力端子および1つの出力端子を備える、その出力端子上で前記発振信号を生成するために前記水晶共振子回路を駆動するためのホワイトカスコードバッファ回路であって、入力端子が最初に前記接続手段を介して前記共通ゲート増幅器回路の入力端子に接続され、次に前記制御手段の入力端子に接続されたホワイトカスコードバッファ回路と、

補助的に必要な電流基準のための1つの端子とを備える、請求項1に記載の回路。 - 前記水晶共振子素子は直列共振モードで動作し、したがって共振周波数において純抵抗性インピーダンス値を示す、請求項32に記載の回路。

- 前記記載の方法で共に結合され、このため1つの入力端子および2つの出力端子を示し、そして発振器コア回路として示される、前記増幅器の利得を制御するための前記入力端子と、制御出力端子として使用される一方の出力端子と、信号出力端子として使用される他方の出力端子とを備え、前記信号出力端子は、前記接続手段を介して帰還ループとして前記入力端子に内部接続されている、請求項32に記載の回路。

- 前記内部帰還ループ接続は直接DC結合として実現され、容量コンポーネントを実質的に回避するように、前記発振器コアを実現する、請求項34に記載の回路。

- モノリシック集積回路技術を使用して製造される、請求項1に記載の回路。

- モノリシック集積CMOS技術を使用して製造される、請求項36に記載の回路。

- 前記発振生成手段は、個別コンポーネントとしてオフチップで取り付けられる、請求項36に記載の回路。

- 前記発振生成手段は、集積コンポーネントとしてオンチップで取り付けられる、請求項36に記載の回路。

- 電子デバイスまたは電子技術を使用して安定した振幅制御発振信号を生成するための方法であって、

発振器周波数を決定するための水晶共振子素子を提供するステップと、

共振子素子を駆動するためのホワイトカスコードバッファ回路を提供するステップと、

発振信号を増幅するための共通ゲート増幅器回路を提供するステップと、

発振信号を安定化させるための自動利得制御回路を提供するステップと、

発振器回路を負荷の影響から分離するための出力バッファ回路を提供するステップと、

バイアス基準電流をバッファ回路に引き渡すためのバイアスブロック回路を提供するステップと、

発振の閉ループ生成を制御するステップとを含む方法。 - 発振の閉ループ生成を制御する前記ステップは、

水晶共振子素子の一方のパッドを前記ホワイトカスコードバッファ回路の前記出力端子に接続するステップと、

水晶共振子素子の他方のパッドを前記共通ゲート増幅器回路の前記信号入力端子に接続するステップと、

前記共通ゲート増幅器回路の前記出力端子を前記ホワイトカスコードバッファ回路の入力端子に接続するステップと、

前記ホワイトカスコードバッファ回路の入力端子および前記共通ゲート増幅器回路の出力端子を、それぞれ前記自動利得制御回路の前記入力端子に接続するステップと、

前記自動利得制御回路の出力端子を共通利得増幅器の前記制御入力端子に接続するステップと、

前記共通ゲート増幅器の前記出力端子を前記出力バッファの前記入力端子に接続するステップとを含む、請求項40に記載の方法。 - 発振の閉ループ生成を制御する前記ステップは、

十分な基準電流を前記バイアスブロック回路から前記ホワイトカスコードバッファ回路および前記出力バッファ回路にそれぞれ供給するステップをさらに含む、請求項40に記載の方法。 - 発振の閉ループ生成を制御する前記ステップは、

水晶発振器のスタートアップ時における過渡プロセスを有効に高速化するために、前記水晶発振器回路のスタートアップ時における前記共通ゲート増幅器の利得が確実に最大値に設定されるよう、前記自動制御回路の前記出力信号を調整するステップをさらに含む、請求項40に記載の方法。 - 発振の閉ループ生成を制御する前記ステップは、

前記水晶発振器回路の定常状態動作時における前記共通ゲート増幅器の利得が、前記発振器の振幅ひずみおよび位相雑音が最小化される適切な値に確実に設定されるよう、前記自動制御回路の前記出力信号を調整するステップをさらに含む、請求項40に記載の方法。

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| EP02368134A EP1432119A1 (en) | 2002-12-17 | 2002-12-17 | High quality serial resonance oscillator |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2004201320A true JP2004201320A (ja) | 2004-07-15 |

| JP4596770B2 JP4596770B2 (ja) | 2010-12-15 |

Family

ID=32309506

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2003418164A Expired - Fee Related JP4596770B2 (ja) | 2002-12-17 | 2003-12-16 | 高品質直列共振発振器 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US6741137B1 (ja) |

| EP (1) | EP1432119A1 (ja) |

| JP (1) | JP4596770B2 (ja) |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2010141889A (ja) * | 2008-12-09 | 2010-06-24 | Commissariat A L'energie Atomique & Aux Energies Alternatives | 結合共振器のアレイ、バンドパスフィルタおよび発振器 |

| US8570112B2 (en) | 2011-06-09 | 2013-10-29 | Panasonic Corporation | Oscillator with MEMS resonator |

| JP2014510921A (ja) * | 2011-03-31 | 2014-05-01 | コミサリア ア レネルジー アトミック エ オ ゼネルジー アルテルナティブ | 電気機械共振器を有する測定システム、該システムを製造するための方法、および、少なくとも2つの電気機械共振器を読み取るための方法 |

Families Citing this family (22)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7352107B2 (en) * | 2003-03-31 | 2008-04-01 | Suren Systems, Ltd. | Transconductance circuit for piezoelectric transducer |

| US7042134B2 (en) * | 2003-03-31 | 2006-05-09 | Suren Systems, Ltd. | Transconductance circuit for piezoelectric transducer |

| US7622845B2 (en) | 2003-03-31 | 2009-11-24 | Suren Systems, Ltd. | Piezoelectric transducer signal processing circuit |

| US7141910B2 (en) * | 2003-03-31 | 2006-11-28 | Suren Systems, Ltd. | Transconductance circuit for piezoelectric transducer |

| US6888418B2 (en) * | 2003-06-24 | 2005-05-03 | Stmicroelectronics, Inc. | Control circuit and method for a crystal oscillator using a timer |

| JP4071681B2 (ja) * | 2003-07-24 | 2008-04-02 | 株式会社東芝 | 電圧制御発振器、周波数シンセサイザ及び通信システム |

| US7271674B1 (en) * | 2003-08-15 | 2007-09-18 | Dsp Group Inc. | Automatic level control for radio frequency amplifiers |

| US7187245B1 (en) * | 2003-09-25 | 2007-03-06 | Cypress Semiconductor Corporation | Amplitude control for crystal oscillator |

| JP4470606B2 (ja) * | 2004-06-18 | 2010-06-02 | ソニー株式会社 | 高周波素子、並びに通信装置 |

| US7183868B1 (en) | 2004-09-09 | 2007-02-27 | Sandia Corporation | Triple inverter pierce oscillator circuit suitable for CMOS |

| US8035455B1 (en) | 2005-12-21 | 2011-10-11 | Cypress Semiconductor Corporation | Oscillator amplitude control network |

| US7737790B1 (en) * | 2009-04-09 | 2010-06-15 | Mediatek Inc. | Cascode amplifier and method for controlling current of cascode amplifier |

| WO2012017572A1 (ja) * | 2010-08-06 | 2012-02-09 | パナソニック株式会社 | 発振器 |

| US8228130B1 (en) | 2011-02-15 | 2012-07-24 | Texas Instruments Incorporated | Circuitry and method for precision amplitude control in quartz and MEMS oscillators |

| US8466754B1 (en) * | 2011-06-03 | 2013-06-18 | Rockwell Collins, Inc. | Low phase noise MEMS-based oscillator with bifurcation and parametric noise squeezing |

| TWI511916B (zh) * | 2012-06-28 | 2015-12-11 | Nat Univ Tsing Hua | 微機電共振震盪子結構及其驅動方法 |

| US8922287B2 (en) | 2013-01-30 | 2014-12-30 | Freescale Semiconductor, Inc. | Amplitude loop control for oscillators |

| CN107294513B (zh) * | 2016-03-30 | 2021-02-02 | 中芯国际集成电路制造(上海)有限公司 | 晶体振荡器电路 |

| CN106685419B (zh) * | 2016-12-20 | 2019-06-07 | 武汉邮电科学研究院 | 高精度的宽带分频器 |

| US10622945B1 (en) * | 2017-07-26 | 2020-04-14 | Sitime Corporation | Low Allan-Deviation oscillator |

| RU2748218C1 (ru) * | 2020-02-04 | 2021-05-21 | Алексей Валерьевич Голубев | Сверхмалошумящий кварцевый генератор |

| US12176855B2 (en) * | 2021-11-22 | 2024-12-24 | Qorvo Us, Inc. | Power amplifier having improved gate oxide integrity |

Citations (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US3979693A (en) * | 1975-08-29 | 1976-09-07 | Bell Telephone Laboratories, Incorporated | Crystal-controlled oscillator having sinusoidal and square-wave output signals |

| JPS526066A (en) * | 1975-06-30 | 1977-01-18 | Ibm | Hartley oscillator |

| JPS5783904A (en) * | 1980-09-19 | 1982-05-26 | Ebauches Electroniques Sa | Low consumption current oscillator circuit |

| JPS6314506A (ja) * | 1986-07-07 | 1988-01-21 | Eishitsuku Technol Kk | 電圧増幅回路 |

| JPH0836434A (ja) * | 1994-07-22 | 1996-02-06 | Oki Micro Design Miyazaki:Kk | バイアス回路 |

| JPH1075127A (ja) * | 1996-06-11 | 1998-03-17 | Micronas Oy | 低ノイズ増幅器 |

| JP2001119254A (ja) * | 1999-10-15 | 2001-04-27 | Rf Chips Technology Inc | 利得可変増幅回路および通信機器 |

| WO2001082467A2 (en) * | 2000-04-20 | 2001-11-01 | The Regents Of The University Of Michigan | Method and apparatus for generating a signal having at least one desired output frequency utilizing a bank of vibrating micromechanical devices |

| JP2002016439A (ja) * | 2000-06-27 | 2002-01-18 | Toyo Commun Equip Co Ltd | 圧電発振器 |

Family Cites Families (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CA1010121A (en) * | 1975-03-20 | 1977-05-10 | Allistair Towle | Stabilized crystal controlled oscillator |

| JP3542886B2 (ja) | 1997-04-18 | 2004-07-14 | 有限会社バイテックス | 温度補償水晶発振器 |

| US5834983A (en) * | 1997-09-30 | 1998-11-10 | Hewlett-Packard Company | Wideband oscillator with automatic bias control |

| US6052036A (en) | 1997-10-31 | 2000-04-18 | Telefonaktiebolaget L M Ericsson | Crystal oscillator with AGC and on-chip tuning |

| US6194973B1 (en) | 1998-05-29 | 2001-02-27 | Intel Corporation | Oscillator with automatic gain control |

| US6278338B1 (en) | 2000-05-01 | 2001-08-21 | Silicon Wave Inc. | Crystal oscillator with peak detector amplitude control |

-

2002

- 2002-12-17 EP EP02368134A patent/EP1432119A1/en not_active Withdrawn

-

2003

- 2003-01-06 US US10/336,872 patent/US6741137B1/en not_active Expired - Lifetime

- 2003-12-16 JP JP2003418164A patent/JP4596770B2/ja not_active Expired - Fee Related

Patent Citations (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS526066A (en) * | 1975-06-30 | 1977-01-18 | Ibm | Hartley oscillator |

| US3979693A (en) * | 1975-08-29 | 1976-09-07 | Bell Telephone Laboratories, Incorporated | Crystal-controlled oscillator having sinusoidal and square-wave output signals |

| JPS5783904A (en) * | 1980-09-19 | 1982-05-26 | Ebauches Electroniques Sa | Low consumption current oscillator circuit |

| JPS6314506A (ja) * | 1986-07-07 | 1988-01-21 | Eishitsuku Technol Kk | 電圧増幅回路 |

| JPH0836434A (ja) * | 1994-07-22 | 1996-02-06 | Oki Micro Design Miyazaki:Kk | バイアス回路 |

| JPH1075127A (ja) * | 1996-06-11 | 1998-03-17 | Micronas Oy | 低ノイズ増幅器 |

| JP2001119254A (ja) * | 1999-10-15 | 2001-04-27 | Rf Chips Technology Inc | 利得可変増幅回路および通信機器 |

| WO2001082467A2 (en) * | 2000-04-20 | 2001-11-01 | The Regents Of The University Of Michigan | Method and apparatus for generating a signal having at least one desired output frequency utilizing a bank of vibrating micromechanical devices |

| JP2002016439A (ja) * | 2000-06-27 | 2002-01-18 | Toyo Commun Equip Co Ltd | 圧電発振器 |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2010141889A (ja) * | 2008-12-09 | 2010-06-24 | Commissariat A L'energie Atomique & Aux Energies Alternatives | 結合共振器のアレイ、バンドパスフィルタおよび発振器 |

| JP2014510921A (ja) * | 2011-03-31 | 2014-05-01 | コミサリア ア レネルジー アトミック エ オ ゼネルジー アルテルナティブ | 電気機械共振器を有する測定システム、該システムを製造するための方法、および、少なくとも2つの電気機械共振器を読み取るための方法 |

| US8570112B2 (en) | 2011-06-09 | 2013-10-29 | Panasonic Corporation | Oscillator with MEMS resonator |

Also Published As

| Publication number | Publication date |

|---|---|

| EP1432119A1 (en) | 2004-06-23 |

| US6741137B1 (en) | 2004-05-25 |

| JP4596770B2 (ja) | 2010-12-15 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4596770B2 (ja) | 高品質直列共振発振器 | |

| JP4536364B2 (ja) | 高品質並列共振発振器 | |

| TW512585B (en) | Crystal oscillator with peak detector amplitude control | |

| JP6321001B2 (ja) | 一定の高調波成分を有する自己バイアス振幅制御発振器 | |

| CN102868362B (zh) | 温度补偿电路以及合成器 | |

| JPH104318A (ja) | 温度補償型水晶発振器 | |

| JP5800985B2 (ja) | 低ノイズ発振器 | |

| WO2007095451A1 (en) | High gain, high frequency cmos oscillator circuit and method | |

| JPH08506462A (ja) | 低ノイズ発振器およびトラッキングフィルタ | |

| US20060061425A1 (en) | Average controlled (AC) resonator driver | |

| JP3760100B2 (ja) | 電圧制御発振器 | |

| US7688154B1 (en) | Amplitude regulated crystal oscillator | |

| JP2002515664A (ja) | 発振器を含む集積回路 | |

| US7038550B2 (en) | Smart current controlled (SCC) resonator driver | |

| JP2002026650A (ja) | 発振器 | |

| US7928810B2 (en) | Oscillator arrangement and method for operating an oscillating crystal | |

| JP4042207B2 (ja) | 圧電発振器 | |

| JP4524179B2 (ja) | ピアース型発振回路 | |

| JP2001217649A (ja) | 圧電発振回路 | |

| JP2001077626A (ja) | バッファ回路付き発振器 | |

| JPH066594Y2 (ja) | オ−バ−ト−ン水晶発振回路 | |

| JP2002026660A (ja) | 電圧制御水晶発振器 | |

| JPS6019370Y2 (ja) | 発振回路 | |

| JP2002185253A (ja) | 発振回路 | |

| JPH10303643A (ja) | 電圧制御発振回路 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20061215 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070215 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20090807 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20090820 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20091120 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20091126 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100222 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20100823 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20100921 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131001 Year of fee payment: 3 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |