JP4686830B2 - 固体撮像素子及びその駆動方法 - Google Patents

固体撮像素子及びその駆動方法 Download PDFInfo

- Publication number

- JP4686830B2 JP4686830B2 JP2000257463A JP2000257463A JP4686830B2 JP 4686830 B2 JP4686830 B2 JP 4686830B2 JP 2000257463 A JP2000257463 A JP 2000257463A JP 2000257463 A JP2000257463 A JP 2000257463A JP 4686830 B2 JP4686830 B2 JP 4686830B2

- Authority

- JP

- Japan

- Prior art keywords

- gate

- overflow

- electrode

- transfer

- layer

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10F—INORGANIC SEMICONDUCTOR DEVICES SENSITIVE TO INFRARED RADIATION, LIGHT, ELECTROMAGNETIC RADIATION OF SHORTER WAVELENGTH OR CORPUSCULAR RADIATION

- H10F39/00—Integrated devices, or assemblies of multiple devices, comprising at least one element covered by group H10F30/00, e.g. radiation detectors comprising photodiode arrays

- H10F39/10—Integrated devices

- H10F39/12—Image sensors

- H10F39/18—Complementary metal-oxide-semiconductor [CMOS] image sensors; Photodiode array image sensors

- H10F39/186—Complementary metal-oxide-semiconductor [CMOS] image sensors; Photodiode array image sensors having arrangements for blooming suppression

- H10F39/1865—Overflow drain structures

Landscapes

- Solid State Image Pick-Up Elements (AREA)

- Transforming Light Signals Into Electric Signals (AREA)

Description

【発明の属する技術分野】

本発明は、転送レジスタに対してオーバーフロードレインが設けられた固体撮像素子及びその駆動方法に係わる。

【0002】

【従来の技術】

従来、CCD固体撮像素子の転送レジスタにおいてオーバーフロー制御を行う場合には、転送レジスタのストレージ電極を形成する下層の多結晶シリコン層の横に上層の多結晶シリコン層とバリア用インプラによって、オーバーフローバリアを形成していた。

【0003】

この従来のオーバーフロー制御を行う構造の概略構成図(平面図)を図5に示す。

転送レジスタ50の上に、第1層の転送電極51と第2層の転送電極52とが交互に配置されている。

第1層の転送電極51はストレージ電極St1,St2となり、第2層の転送電極52はトランスファー電極Tr1,Tr2となる。

ストレージ電極St1及びトランスファー電極Tr1には、それぞれの駆動パルスφSt1,φTr1として第1相の駆動パルスφ1が印加される。

ストレージ電極St2及びトランスファー電極Tr2には、それぞれの駆動パルスφSt2,φTr2として第2相の駆動パルスφ2が印加される。

【0004】

そして、図5のほぼ中央の第1相のストレージ電極St1の側方に、オーバーフローコントロールゲートOFCG及びオーバーフロードレインOFDが設けられている。

【0005】

また、図5のY−Y´における断面図を図6に示す。

オーバーフローコントロールゲートOFCGは、図5及び図6に示すように、ゲート電極54とN- 領域56とから構成されている。

ゲート電極54は、トランスファー電極Tr1,Tr2を構成する第2層の転送電極52と同じ第2層の多結晶シリコン層により形成されている。このゲート電極54には、駆動パルスφOFCGが印加される。

N- 領域56は、半導体基板1のP型ウエル領域2内に、N型不純物をイオン注入して形成されている。

オーバーフロードレインOFDは、半導体基板1のP型ウエル領域2内に高濃度N型不純物をイオン注入して形成されたN++領域55により構成される。

尚、図中3は、ストレージ電極St1,St2の下に形成されたN+ 領域を示し、この領域3に転送中の電荷が蓄積される。

【0006】

さらに、図5のY−Y´におけるポテンシャル断面図を図7に示す。

図7に示すように、ゲート電極54及びN- 領域56によるオーバーフローコントロールゲートOFCGがバリアとなっており、このバリアを越えた電荷をオーバーフロードレインOFDに捨てている。

【0007】

この構成において、オーバーフローコントロールゲートOFCGのバリアの高さに影響する因子としては、オーバーフローコントロールゲートOFCGのゲート電極54の第1相のストレージ電極St1と重なっていない部分の長さL1即ちオーバーフローコントロールゲートOFCGの実効長と、N- 領域56の不純物濃度とが挙げられる。

【0008】

また、図5の構成における駆動パルスのタイミングチャートを図8に示す。

第1相のストレージ電極St1の駆動パルスφSt1及び第1相のトランスファー電極Tr1の駆動パルスφTr1は、共に同じ駆動パルス(第1相の駆動パルスφ1)が印加される。

一方、第2相のストレージ電極St2の駆動パルスφSt2及び第2相のトランスファー電極Tr2の駆動パルスφTr2は、共に同じ駆動パルス(第2相の駆動パルスφ2)が印加される。

第1相の駆動パルスφ1と第2相の駆動パルスφ2とは互いに逆相である。

【0009】

そして、オーバーフローコントロールゲートOFCGの駆動パルスφOFCGは、第1相の駆動パルスφ1と同相の駆動パルスとなっている。

【0010】

これにより、次のように電荷の転送及びオーバーフローの動作がなされる。

第1相の駆動パルスφ1がハイレベルHiで第1相のストレージ電極St1に電荷があるときには、オーバーフローコントロールゲートOFCGの駆動パルスφOFCGもハイレベルHiであり、オーバーフローバリアの高さが低くなり所定量でオーバーフローさせることが可能になる。

一方、第1相の駆動パルスφ1がローレベルLoで第1相のストレージ電極St1から隣の第2相の電極Tr2,St2へ電荷が転送されるときには、オーバーフローコントロールゲートOFCGの駆動パルスφOFCGもローレベルLoであり、オーバーフローバリアの高さが高くなって、転送中の電荷がバリアを越えないようにすることができる。

【0011】

【発明が解決しようとする課題】

しかしながら、この従来の構成の場合、下層の第1層の多結晶シリコン層から成る第1相のストレージ電極St1と、上層の第2層の多結晶シリコン層から成るオーバーフローコントロールOFCGゲートのゲート電極54との間に合わせずれが生じると、オーバーフローコントロールゲートOFCGの実効長L1が変化してしまう。

この実効長L1が変化するとオーバーフローコントロールゲートOFCGによるバリアの高さも変化してしまう。また、転送チャネル50のバリアの高さを規定するトランスファー電極Tr1の実効長Lとの関係も変化する。

【0012】

また、N- 領域56とゲート電極54との合わせズレや、下層の多結晶シリコン層51や上層の多結晶シリコン層52,54の線幅のばらつき等によっても、オーバーフローコントロールゲートOFCGによるバリアの高さが変化する。

【0013】

そして、合わせズレ等のばらつきが大きいと、オーバーフローコントロールゲートOFCGのバリア高さとトランスファー電極Tr1のバリア高さの差が、小さくなったり大きくなり過ぎたりして、適切なオーバーフロー制御ができない場合があった。

このことが、細かな制御を行う場合や固体撮像素子を微細化する際に問題となっていた。

【0014】

上述した問題の解決のために、本発明においては、適切なオーバーフロー制御を行うことができる固体撮像素子及びその駆動方法を提供するものである。

【0015】

【課題を解決するための手段】

本発明の固体撮像素子は、転送レジスタにオーバーフローコントロールゲート及びオーバーフロードレインが設けられ、転送レジスタにおいては、第1層の転送電極と第2層の転送電極とが交互に配置され、オーバーフローコントロールゲートは、ゲート電極と、このゲート電極の下のN − 領域とにより構成され、オーバーフロードレインは、N ++ 領域により構成され、オーバーフローコントロールゲートのゲート電極が、転送レジスタの第2層の転送電極と一体化して形成され、オーバーフローコントロールゲートとオーバーフロードレインとの間にゲートが設けられ、このゲートは第1層の転送電極と同じ層により形成され、このゲートの下にN + 領域が形成され、オーバーフローコントロールゲートのゲート電極が転送レジスタ側及びオーバーフロードレイン側においてそれぞれ下層の第1層の転送電極上及びゲート上に重ねて形成されているものである。

本発明の固体撮像素子の駆動方法は、転送レジスタにオーバーフローコントロールゲート及びオーバーフロードレインが設けられ、転送レジスタにおいては、第1層の転送電極と第2層の転送電極とが交互に配置され、オーバーフローコントロールゲートは、ゲート電極と、このゲート電極の下のN − 領域とにより構成され、オーバーフロードレインは、N ++ 領域により構成され、オーバーフローコントロールゲートのゲート電極が、転送レジスタの第2層の転送電極と一体化して形成され、オーバーフローコントロールゲートとオーバーフロードレインとの間にゲートが設けられ、このゲートは第1層の転送電極と同じ層により形成され、このゲートの下にN + 領域が形成され、オーバーフローコントロールゲートのゲート電極が、転送レジスタ側及びオーバーフロードレイン側においてそれぞれ下層の第1層の転送電極上及びゲート上に重ねて形成されている固体撮像素子に対して、オーバーフローコントロールゲートのゲート電極には、転送レジスタの電極に印加される駆動パルスを印加し、オーバーフロードレイン側のゲートには、常にオン状態とする駆動パルスを印加するものである。

【0016】

上述の本発明の固体撮像素子の構成によれば、オーバーフローコントロールゲートのゲート電極が転送レジスタ側及びオーバーフロードレイン側においてそれぞれ下層の第1層の転送電極上及びゲート上に重ねて形成されていることにより、オーバーフローコントロールゲートの実効長が、転送レジスタ側及びオーバーフロードレイン側の下層の第1層の転送電極及びゲートの間隔により規定される。

上述の本発明の固体撮像素子の駆動方法によれば、オーバーフローコントロールゲートのゲート電極には、転送レジスタの電極に印加される駆動パルスを印加し、オーバーフロードレイン側のゲートには、常にオン状態とする駆動パルスを印加することにより、オーバーフロードレイン側のゲートが常にオン状態となっていて、オーバーフローコントロールゲートによるバリアを超えた電荷を妨げることなくオーバーフロードレインに排出することができる。

【0017】

【発明の実施の形態】

本発明は、転送レジスタにオーバーフローコントロールゲート及びオーバーフロードレインが設けられ、転送レジスタにおいては、第1層の転送電極と第2層の転送電極とが交互に配置され、オーバーフローコントロールゲートは、ゲート電極と、このゲート電極の下のN − 領域とにより構成され、オーバーフロードレインは、N ++ 領域により構成され、オーバーフローコントロールゲートのゲート電極が、転送レジスタの第2層の転送電極と一体化して形成され、オーバーフローコントロールゲートとオーバーフロードレインとの間にゲートが設けられ、このゲートは第1層の転送電極と同じ層により形成され、このゲートの下にN + 領域が形成され、オーバーフローコントロールゲートのゲート電極が転送レジスタ側及びオーバーフロードレイン側においてそれぞれ下層の第1層の転送電極上及びゲート上に重ねて形成されている固体撮像素子である。

本発明は、転送レジスタにオーバーフローコントロールゲート及びオーバーフロードレインが設けられ、転送レジスタにおいては、第1層の転送電極と第2層の転送電極とが交互に配置され、オーバーフローコントロールゲートは、ゲート電極と、このゲート電極の下のN − 領域とにより構成され、オーバーフロードレインは、N ++ 領域により構成され、オーバーフローコントロールゲートのゲート電極が、転送レジスタの第2層の転送電極と一体化して形成され、オーバーフローコントロールゲートとオーバーフロードレインとの間にゲートが設けられ、このゲートは第1層の転送電極と同じ層により形成され、このゲートの下にN + 領域が形成され、オーバーフローコントロールゲートのゲート電極が、転送レジスタ側及びオーバーフロードレイン側においてそれぞれ下層の第1層の転送電極上及びゲート上に重ねて形成されている固体撮像素子に対して、オーバーフローコントロールゲートのゲート電極には、転送レジスタの電極に印加される駆動パルスを印加し、オーバーフロードレイン側のゲートには、常にオン状態とする駆動パルスを印加する固体撮像素子の駆動方法である。

【0018】

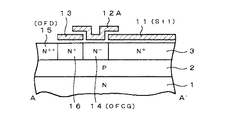

図1は本発明の一実施の形態として、CCD固体撮像素子の転送レジスタの要部の拡大平面図を示す。

転送レジスタ10の上に、第1層の転送電極11と第2層の転送電極12とが交互に配置されている。

第1層の転送電極11はストレージ電極St1,St2となり、第2層の転送電極12はトランスファー電極Tr1,Tr2となる。

ストレージ電極St1及びトランスファー電極Tr1には、それぞれの駆動パルスφSt1,φTr1として第1相の駆動パルスφ1が印加される。

ストレージ電極St2及びトランスファー電極Tr2には、それぞれの駆動パルスφSt2,φTr2として第2相の駆動パルスφ2が印加される。

【0019】

本実施の形態では、特に図1のほぼ中央の第1相のストレージ電極St1の側方に、オーバーフローコントロールゲートOFCG及びオーバーフロードレインOFDが設けられ、さらにこれらオーバーフローコントロールゲートOFCG及びオーバーフロードレインOFDの間にゲート13が設けられている。

【0020】

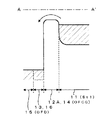

また、図1のA−A´における断面図を図2に示す。尚、図2において、半導体基板1、P型ウエル領域2、並びにストレージ電極St1,St2用のN+ 領域3は、図6と同様であるので同一符号を付している。

オーバーフローコントロールゲートOFCGは、図1及び図2に示すように、第1相のトランスファー電極Tr1を構成している第2層の転送電極12をL字状に延長した部分12Aから成るゲート電極とN- 領域14とから構成されている。

ゲート電極12Aが第1相のトランスファー電極Tr1と導通しているため、このゲート電極12Aには第1相のトランスファー電極Tr1の駆動パルスφTr1が印加される。

N- 領域14は、半導体基板1のP型ウエル領域2内に、N型不純物をイオン注入して形成されている。

オーバーフロードレインOFDは、半導体基板1のP型ウエル領域2内に高濃度N型不純物をイオン注入して形成されたN++領域15により構成される。

【0021】

また、オーバーフローコントロールゲートOFCG及びオーバーフロードレインOFDの間のゲート13は、第1相のストレージ電極St1と同じ第1層の多結晶シリコン層により形成される。

このゲート13には駆動パルスφGが印加される。

【0022】

そして、オーバーフローコントロールゲートOFCGのゲート電極12Aは、転送レジスタ10側において第1層の多結晶シリコン層によるストレージ電極St1上にある。この点は図5の構成と同様である。

さらに、オーバーフローコントロールゲートOFCGのゲート電極12Aは、オーバーフロードレインOFD側においても、第1層の多結晶シリコン層によるゲート13上にある。この点が図5の構成とは異なっている。

【0023】

これにより、それぞれ第1層の多結晶シリコン層により形成されるゲート13及び第1相のストレージ電極St1の間隔によって、その上の第2層の多結晶シリコン層により形成されるオーバーフローコントロールゲートOFCGの実効長L2が規定される。

【0024】

さらに、図1のA−A´におけるポテンシャル断面図を図3に示す。

図3に示すように、ゲート電極12A及びN- 領域14によるオーバーフローコントロールゲートOFCGがバリアとなっており、このバリアを越えた電荷をオーバーフロードレインOFDに捨てることができる。

【0025】

この構成において、オーバーフローバリアの高さに影響する因子としては、オーバーフローコントロールゲートOFCGのゲート電極12Aの下層の電極St1及び13と重なっていない部分の長さL2即ちオーバーフローコントロールゲートOFCGの実効長と、N- 領域14の不純物濃度とが挙げられる。

【0026】

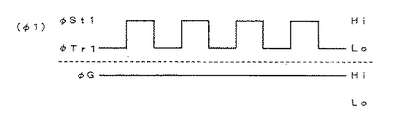

図1の構成における駆動パルスのタイミングチャートを図4に示す。

第1相のストレージ電極St1の駆動パルスφSt1及び第1相のトランスファー電極Tr1の駆動パルスφTr1は、共に同じ駆動パルス(第1相の駆動パルスφ1)が印加される。

そして、第1相のトランスファー電極Tr1と導通されたオーバーフローコントロールゲートOFCGのゲート電極12Aも、同じ駆動パルスφTr1(φ1)により動作する。

【0027】

また、ゲート電極13の駆動パルスφGは、常にハイレベルHiとされる。

従って、ゲート13は常にオン状態となっていて、オーバーフローコントロールゲートOFCGによるバリアを超えた電荷を妨げることなくオーバーフロードレインOFDに排出することができる。

尚、第2相の駆動パルスφ2は、図8と同様であるので、この図4では省略している。

【0028】

これにより、次のように電荷の転送及びオーバーフローの動作がなされる。

第1相の駆動パルスφ1がハイレベルHiであるときには、第1相のストレージ電極St1に電荷があり、かつオーバーフローコントロールゲートOFCGのゲート電極12AもハイレベルHiであり、オーバーフローバリアの高さが低くなり所定量でオーバーフローさせることが可能になる。

一方、第1相の駆動パルスφ1がローレベルLoであるときには、第1相のストレージ電極St1から隣の第2相の電極Tr2,St2へ電荷が転送され、オーバーフローコントロールゲートOFCGのゲート電極12AもローレベルLoであり、オーバーフローバリアの高さが高くなって、転送中の電荷がバリアを越えないようにすることができる。

【0029】

そして、オーバーフローコントロールゲートOFCGの実効長L2となる両側の第1層の電極St1,13の間隔L2を、第1相のトランスファー電極Tr1の実効長L3即ちストレージ電極St1,St2の間隔よりも狭くすることにより、トランスファー電極Tr1のバリア高さよりもオーバーフローコントロールゲートOFCGのバリア高さを低く設定することができる。

【0030】

本実施の形態の構成では、オーバーフローコントロールゲートOFCGのバリアの高さを規定する実効長L2のばらつき要因としては、両側の第1層の電極13,St1の間隔だけである。

そして、オーバーフローコントロールゲートOFCGも、トランスファー電極Tr1も、いずれも両側の第1層の電極の間隔及び不純物濃度でバリアの高さが設定される。

従って、オーバーフローコントロールゲートOFCGの両側の第1層の電極13及びSt1の間隔やN- 領域14の不純物濃度がばらついても、オーバーフローコントロールゲートOFCG及びトランスファー電極Tr1が等しくバリアが高くなる(低くなる)方向に動く。即ち例えば一方の間隔が狭くなったときは、他方の間隔も同様に狭くなる。

これにより、第1層の電極の間隔や不純物濃度にかかわらず、両者のバリアの関係が、ほぼ所定の差に保たれることになる。

【0031】

これにより、オーバーフローバリアの制御を非常に高い精度で行うことができる。

【0032】

上述の構成のオーバーフローコントロールゲートOFCG及びオーバーフロードレインOFDは、固体撮像素子において電荷転送を行う転送レジスタ10の途中に設ける。

例えばラインセンサでは、各転送レジスタにおいて、センサ(画素)のある部分と出力部との間の1カ所にオーバーフローコントロールゲートOFCG及びオーバーフロードレインOFDを設ける。尚、センサの両側で読み出して、出力部の手前で合流させる構成の場合には、合流する前に設けるようにする。

また、例えばエリアセンサでは、垂直転送レジスタから水平転送レジスタへの接続部や、水平転送レジスタの途中にオーバーフローコントロールゲートOFCG及びオーバーフロードレインOFDを設けることができる。

【0033】

上述の本実施の形態によれば、オーバーフローコントロールゲートOFCGの実効長L2が、両側の第1層の電極13,St1の間隔で規定されるので、オーバーフローコントロールゲートOFCGのバリア高さのばらつき要因を少なくすることができる。

そして、両側の第1層の電極13,St1の間隔がばらついても、トランスファー電極Tr1の実効長L3も連動して変化するため、オーバーフローコントロールゲートOFCGによるバリアの高さとトランスファー電極Tr1によるバリアの高さとの関係が所定の関係にほぼ保たれる。

【0034】

即ち本実施の形態の構成により、適切なオーバーフロー制御を行うことができる。

従って、細かい制御を行うことや、固体撮像素子の微細化を図ることが可能になる。

【0035】

また、上述の実施の形態では、オーバーフローコントロールゲートOFCGのゲート電極12Aと第1相のトランスファー電極Tr1とをL字状の一体化したパターンで形成しているため、コンタクト部を1つ設けるだけでオーバーフローコントロールゲートOFCG及びトランスファー電極Tr1を両方駆動させることが可能になる。

【0036】

従って、コンタクト部をそれぞれに設ける必要がなくなり、従来より電極の微細化を図ることが可能になる。そして、例えばL字の角部にコンタクト部を設ければ、コンタクト部オーバーフローコントロールゲートOFCG及びトランスファー電極Tr1の実効長L2及びL3をコンタクト部に係わらず自由に設定することが可能になる。

【0037】

尚、上述の実施の形態では、オーバーフローコントロールゲートOFCGのゲート電極12Aと第1相のトランスファー電極Tr1とを一体化したパターンで形成しているが、これらを図5の従来例のように別々に形成してもよい。この場合は、それぞれにコンタクト部を設けた上で、共に同じ第1相の駆動パルスφ1を印加するように構成する。

【0038】

上述の実施の形態は、2層2相駆動の場合であるが、3相や4相等他の駆動方式の転送レジスタに関しても同様に本発明を適用することができる。

そして、いずれの駆動方式の場合も、オーバーフローバリアの高さを下層の多結晶シリコン層の間隔によって規定することができる。

【0039】

本発明は、上述の実施の形態に限定されるものではなく、本発明の要旨を逸脱しない範囲でその他様々な構成が取り得る。

【0040】

【発明の効果】

上述の本発明によれば、オーバーフローコントロールゲートのバリア高さのばらつき要因を少なくすることができ、適切なオーバーフロー制御を行うことができる。

従って本発明により、細かい制御を行うことや、固体撮像素子の微細化を図ることが可能になる。

【図面の簡単な説明】

【図1】本発明の一実施の形態のCCD固体撮像素子の転送レジスタの要部の拡大平面図である。

【図2】図1のA−A´における断面図である。

【図3】図1のA−A´におけるポテンシャル断面図である。

【図4】図1の構成における駆動パルスのタイミングチャートである。

【図5】従来のCCD固体撮像素子の転送レジスタの要部の拡大平面図である。

【図6】図5のY−Y´における断面図である。

【図7】図5のY−Y´におけるポテンシャル断面図である。

【図8】図8の構成における駆動パルスのタイミングチャートである。

【符号の説明】

1 N型基板、2 P型ウエル領域、10 転送レジスタ、11 第1層の転送電極、12 第2層の転送電極、13 ゲート、OFCG オーバーフローコントロールゲート、OFD オーバーフロードレイン、St1,St2 ストレージ電極、Tr1,Tr2 トランスファー電極

Claims (2)

- 転送レジスタにオーバーフローコントロールゲート及びオーバーフロードレインが設けられ、

上記転送レジスタにおいては、第1層の転送電極と第2層の転送電極とが交互に配置され、

上記オーバーフローコントロールゲートは、ゲート電極と、該ゲート電極の下のN − 領域とにより構成され、

上記オーバーフロードレインは、N ++ 領域により構成され、

上記オーバーフローコントロールゲートの上記ゲート電極が、上記転送レジスタの上記第2層の転送電極と一体化して形成され、

上記オーバーフローコントロールゲートと、上記オーバーフロードレインとの間に、ゲートが設けられ、該ゲートは上記第1層の転送電極と同じ層により形成され、該ゲートの下にN + 領域が形成され、

上記オーバーフローコントロールゲートの上記ゲート電極が、上記転送レジスタ側及び上記オーバーフロードレイン側において、それぞれ下層の上記第1層の転送電極上及び上記ゲート上に重ねて形成されている

固体撮像素子。 - 転送レジスタにオーバーフローコントロールゲート及びオーバーフロードレインが設けられ、

上記転送レジスタにおいては、第1層の転送電極と第2層の転送電極とが交互に配置され、上記オーバーフローコントロールゲートは、ゲート電極と、該ゲート電極の下のN − 領域とにより構成され、上記オーバーフロードレインは、N ++ 領域により構成され、上記オーバーフローコントロールゲートの上記ゲート電極が、上記転送レジスタの上記第2層の転送電極と一体化して形成され、上記オーバーフローコントロールゲートと、上記オーバーフロードレインとの間に、ゲートが設けられ、該ゲートは上記第1層の転送電極と同じ層により形成され、該ゲートの下にN + 領域が形成され、

上記オーバーフローコントロールゲートの上記ゲート電極が、上記転送レジスタ側及び上記オーバーフロードレイン側において、それぞれ下層の上記第1層の転送電極上及び上記ゲート上に重ねて形成されている固体撮像素子に対して、

上記オーバーフローコントロールゲートのゲート電極には、上記転送レジスタの電極に印加される駆動パルスを印加し、

上記オーバーフロードレイン側の上記ゲートには、常にオン状態とする駆動パルスを印加する

固体撮像素子の駆動方法。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2000257463A JP4686830B2 (ja) | 2000-08-28 | 2000-08-28 | 固体撮像素子及びその駆動方法 |

| TW090119935A TW517386B (en) | 2000-08-28 | 2001-08-14 | Solid-state image pickup device |

| US09/931,464 US6512254B2 (en) | 2000-08-28 | 2001-08-17 | Solid-state image pickup device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2000257463A JP4686830B2 (ja) | 2000-08-28 | 2000-08-28 | 固体撮像素子及びその駆動方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2002076318A JP2002076318A (ja) | 2002-03-15 |

| JP2002076318A5 JP2002076318A5 (ja) | 2007-03-08 |

| JP4686830B2 true JP4686830B2 (ja) | 2011-05-25 |

Family

ID=18745916

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2000257463A Expired - Fee Related JP4686830B2 (ja) | 2000-08-28 | 2000-08-28 | 固体撮像素子及びその駆動方法 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US6512254B2 (ja) |

| JP (1) | JP4686830B2 (ja) |

| TW (1) | TW517386B (ja) |

Families Citing this family (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| EP1341377B1 (en) * | 2002-02-27 | 2018-04-11 | Canon Kabushiki Kaisha | Signal processing device for image pickup apparatus |

| US7492404B2 (en) * | 2004-08-27 | 2009-02-17 | Eastman Kodak Company | Fast flush structure for solid-state image sensors |

| US20080195116A1 (en) * | 2007-02-09 | 2008-08-14 | Karim Mansour | Circumcision clamp and surgical kit |

| JP7765306B2 (ja) * | 2022-02-24 | 2025-11-06 | 浜松ホトニクス株式会社 | 固体撮像素子 |

Family Cites Families (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS63296267A (ja) * | 1987-05-27 | 1988-12-02 | Mitsubishi Electric Corp | 電荷転送装置 |

| JP2666928B2 (ja) * | 1987-07-13 | 1997-10-22 | 株式会社東芝 | 電荷転送素子の出力検出器 |

| JPH084136B2 (ja) * | 1987-12-22 | 1996-01-17 | 日本電気株式会社 | 電荷転送装置 |

| JPH05251480A (ja) * | 1992-03-04 | 1993-09-28 | Sony Corp | 電荷電圧変換装置 |

| JPH06303527A (ja) * | 1993-04-09 | 1994-10-28 | Sony Corp | 電荷結合素子 |

| KR950002084A (ko) * | 1993-06-22 | 1995-01-04 | 오가 노리오 | 전하전송장치 |

-

2000

- 2000-08-28 JP JP2000257463A patent/JP4686830B2/ja not_active Expired - Fee Related

-

2001

- 2001-08-14 TW TW090119935A patent/TW517386B/zh not_active IP Right Cessation

- 2001-08-17 US US09/931,464 patent/US6512254B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| US6512254B2 (en) | 2003-01-28 |

| US20020060329A1 (en) | 2002-05-23 |

| TW517386B (en) | 2003-01-11 |

| JP2002076318A (ja) | 2002-03-15 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP3988239B2 (ja) | 固体撮像素子及びその製造方法 | |

| JPS634751B2 (ja) | ||

| JPH04337670A (ja) | Ccdシフトレジスタ | |

| JP2001326344A (ja) | Lodブルーミング抑圧構造を備えるフル・フレーム型イメージセンサ用高速掃き出し構造 | |

| KR101159032B1 (ko) | 고체 촬상 소자 | |

| JP4686830B2 (ja) | 固体撮像素子及びその駆動方法 | |

| JP2699841B2 (ja) | 固体撮像装置 | |

| JP2877047B2 (ja) | 固体撮像装置 | |

| JP4298061B2 (ja) | 固体撮像装置 | |

| JP3301176B2 (ja) | 電荷転送装置 | |

| JP4178638B2 (ja) | 固体撮像素子及びその駆動方法 | |

| JP3020537B2 (ja) | 電荷結合素子 | |

| US5910013A (en) | Process for manufacturing a solid-state pick-up device | |

| CN100365823C (zh) | 电荷传输器件 | |

| JPS61184876A (ja) | 電荷転送装置 | |

| JP2010073901A (ja) | 固体撮像装置、固体撮像装置の製造方法、及び電子機器 | |

| JP4797302B2 (ja) | 固体撮像素子及びその製造方法 | |

| JPH0436469B2 (ja) | ||

| JP2000114505A (ja) | Ccd固体撮像素子 | |

| JP2747328B2 (ja) | 電荷転送素子 | |

| JPH11266003A (ja) | 半導体装置およびその製造方法 | |

| JP2542902B2 (ja) | 固体撮像素子 | |

| JPH09312390A (ja) | 電荷転送装置とその製造方法 | |

| JPH08316459A (ja) | 電荷転送装置および固体撮像装置 | |

| JPH0231858B2 (ja) |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070119 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20070119 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20100129 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100302 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100407 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20110118 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20110131 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140225 Year of fee payment: 3 |

|

| LAPS | Cancellation because of no payment of annual fees |