JPWO2011093473A1 - 半導体装置 - Google Patents

半導体装置 Download PDFInfo

- Publication number

- JPWO2011093473A1 JPWO2011093473A1 JP2011551946A JP2011551946A JPWO2011093473A1 JP WO2011093473 A1 JPWO2011093473 A1 JP WO2011093473A1 JP 2011551946 A JP2011551946 A JP 2011551946A JP 2011551946 A JP2011551946 A JP 2011551946A JP WO2011093473 A1 JPWO2011093473 A1 JP WO2011093473A1

- Authority

- JP

- Japan

- Prior art keywords

- region

- conductivity type

- type

- main surface

- surface side

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/64—Double-diffused metal-oxide semiconductor [DMOS] FETs

- H10D30/66—Vertical DMOS [VDMOS] FETs

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/01—Manufacture or treatment

- H10D30/021—Manufacture or treatment of FETs having insulated gates [IGFET]

- H10D30/028—Manufacture or treatment of FETs having insulated gates [IGFET] of double-diffused metal oxide semiconductor [DMOS] FETs

- H10D30/0291—Manufacture or treatment of FETs having insulated gates [IGFET] of double-diffused metal oxide semiconductor [DMOS] FETs of vertical DMOS [VDMOS] FETs

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/64—Double-diffused metal-oxide semiconductor [DMOS] FETs

- H10D30/66—Vertical DMOS [VDMOS] FETs

- H10D30/662—Vertical DMOS [VDMOS] FETs having a drift region having a doping concentration that is higher between adjacent body regions relative to other parts of the drift region

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/64—Double-diffused metal-oxide semiconductor [DMOS] FETs

- H10D30/66—Vertical DMOS [VDMOS] FETs

- H10D30/668—Vertical DMOS [VDMOS] FETs having trench gate electrodes, e.g. UMOS transistors

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D62/00—Semiconductor bodies, or regions thereof, of devices having potential barriers

- H10D62/01—Manufacture or treatment

- H10D62/051—Forming charge compensation regions, e.g. superjunctions

- H10D62/058—Forming charge compensation regions, e.g. superjunctions by using trenches, e.g. implanting into sidewalls of trenches or refilling trenches

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D62/00—Semiconductor bodies, or regions thereof, of devices having potential barriers

- H10D62/10—Shapes, relative sizes or dispositions of the regions of the semiconductor bodies; Shapes of the semiconductor bodies

- H10D62/102—Constructional design considerations for preventing surface leakage or controlling electric field concentration

- H10D62/103—Constructional design considerations for preventing surface leakage or controlling electric field concentration for increasing or controlling the breakdown voltage of reverse-biased devices

- H10D62/105—Constructional design considerations for preventing surface leakage or controlling electric field concentration for increasing or controlling the breakdown voltage of reverse-biased devices by having particular doping profiles, shapes or arrangements of PN junctions; by having supplementary regions, e.g. junction termination extension [JTE]

- H10D62/109—Reduced surface field [RESURF] PN junction structures

- H10D62/111—Multiple RESURF structures, e.g. double RESURF or 3D-RESURF structures

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D62/00—Semiconductor bodies, or regions thereof, of devices having potential barriers

- H10D62/10—Shapes, relative sizes or dispositions of the regions of the semiconductor bodies; Shapes of the semiconductor bodies

- H10D62/13—Semiconductor regions connected to electrodes carrying current to be rectified, amplified or switched, e.g. source or drain regions

- H10D62/149—Source or drain regions of field-effect devices

- H10D62/151—Source or drain regions of field-effect devices of IGFETs

- H10D62/156—Drain regions of DMOS transistors

- H10D62/157—Impurity concentrations or distributions

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D62/00—Semiconductor bodies, or regions thereof, of devices having potential barriers

- H10D62/10—Shapes, relative sizes or dispositions of the regions of the semiconductor bodies; Shapes of the semiconductor bodies

- H10D62/17—Semiconductor regions connected to electrodes not carrying current to be rectified, amplified or switched, e.g. channel regions

- H10D62/393—Body regions of DMOS transistors or IGBTs

Landscapes

- Insulated Gate Type Field-Effect Transistor (AREA)

- Chemical & Material Sciences (AREA)

- Composite Materials (AREA)

- Electrodes Of Semiconductors (AREA)

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

Abstract

Description

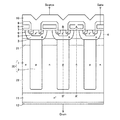

図1は、実施の形態1にかかる半導体装置を示す断面図である。図1に示す半導体装置は、第1主面側に素子活性部を有し、第2主面側にn+ドレイン領域(低抵抗層)11を有する。素子活性部には、例えばプレーナ型MOSFETの表面構造として、pベース領域(第2導電型ベース領域)3、n型表面領域(第1導電型表面領域)4、p+コンタクト領域5、n+ソース領域6、ゲート絶縁膜7、ゲート電極8、層間絶縁膜9およびソース電極10が設けられている。第2主面には、n+ドレイン領域11に接するドレイン電極12が設けられている。

図3は、実施の形態2にかかる半導体装置を示す断面図である。実施の形態1において、トレンチ構造を適用してもよい。

図4は、実施の形態3にかかる半導体装置を示す断面図である。図4では、並列pn層20のうち、1つのpn接合のみを示す(以下、図6および図8においても同様)。実施の形態1において、p型領域2の第1主面側の不純物濃度を、p型領域2の第2主面側の不純物濃度よりも高くしてもよい。

図6は、実施の形態4にかかる半導体装置を示す断面図である。実施の形態3において、p型高濃度領域23を、n型高濃度領域21の下端よりも第2主面側に深く設けてもよい。

図8は、実施の形態5にかかる半導体装置を示す断面図である。実施の形態4において、p型高濃度領域23のうち、n型高濃度領域21の下端よりも第2主面側に深く設けた領域を、n型高濃度領域21の下端よりも第1主面側のp型高濃度領域23よりも低い不純物濃度としてもよい。

図10は、実施の形態6にかかる半導体装置を示す断面図である。実施の形態3において、p型低濃度領域24は、第1主面側から第2主面側にかけて徐々に低くなる不純物濃度分布を有してもよい。

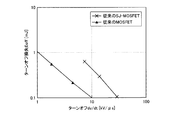

図12は、実施例1の半導体装置におけるターンオフ時の電気的特性を示す特性図である。図12は、ターンオフ損失とターンオフdv/dtとのトレードオフ関係を示すシミュレーション結果である(以下、図14、図21、図24、図27−1、図27−2、図29−1、図29−2および図30において同様)。実施の形態1に従い、n型高濃度領域21の不純物濃度をn型低濃度領域22の不純物濃度の1.2倍としたプレーナ型MOSFETを準備した(以下、第1実施例とする)。また、n型高濃度領域21の不純物濃度をn型低濃度領域22の不純物濃度の1.6倍としたプレーナ型MOSFETを準備した(以下、第2実施例とする)。

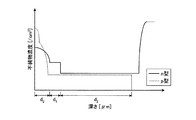

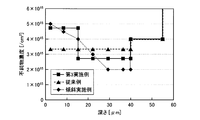

図13は、実施例2にかかる半導体装置のn型不純物濃度分布を示す特性図である。また、図14は、実施例2の半導体装置におけるターンオフ時の電気的特性を示す特性図である。まず、図13に示すように、実施の形態3に従い、プレーナ型MOSFETを準備した(以下、第3実施例とする)。第3実施例では、n型高濃度領域21の厚さおよび不純物濃度を、それぞれ8.0μmおよび4.7×1015cm-3とした。n型低濃度領域22の不純物濃度を、例えば2.7×1015/cm3とした。p型領域2の厚さを、37μmとした。p型高濃度領域23の厚さおよび不純物濃度は、n型高濃度領域21と同様である。p型低濃度領域24の不純物濃度は、n型低濃度領域22と同じである。比較として、実施例1と同様に、従来例を準備した。また、n型領域1の第1主面側から第2主面側にかけて、n型不純物濃度を徐々に低くしたプレーナ型MOSFETを準備した(以下、傾斜実施例とする)。第3実施例、従来例および傾斜実施例ともに、n型領域1の全体の不純物量は同じである。そして、各試料において、ターンオフ損失およびターンオフdv/dtを測定した。

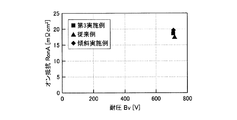

図19は、実施例3にかかる半導体装置における耐圧とオン抵抗との関係を示す特性図である。図19は、耐圧とオン抵抗とのトレードオフ関係を示すシミュレーション結果である。まず、実施例2と同様に、第3実施例を準備した。比較として、実施例1と同様に、従来例を準備した。実施例2と同様に、傾斜実施例を準備した。そして、各試料において、耐圧およびオン抵抗を測定した。図19に示す結果では、半導体装置の性能を決定する指標は、耐圧が高く、かつオン抵抗が低いことである。つまり、グラフの右下に近づくほど、半導体装置の性能は高くなり、オン抵抗と耐圧とのトレードオフ関係が改善されている(以下、図26および図28−1においても同様)。

図20は、実施例4にかかる半導体装置における電気的特性を示す特性図である。また、図21は、実施例4にかかる半導体装置におけるターンオフ時の電気的特性を示す特性図である。図20は、アバランシェ突入後の電流−電圧特性について示すシミュレーション結果である(以下、図23において同様)。まず、実施例2と同様に、第3実施例を準備した。また、実施の形態4に従い、プレーナ型MOSFETを準備した(以下、第4実施例とする)。第4実施例では、n型高濃度領域21の厚さを9μmとした。p型高濃度領域23の厚さを16μmとした。n型高濃度領域21およびp型高濃度領域23の不純物濃度を5.0×1015/cm3とした。n型低濃度領域22およびp型低濃度領域24の不純物濃度を3.0×1015/cm3とした。それ以外の構成は、第3実施例と同様である。そして、第3実施例および第4実施例において、アバランシェ突入後の電流−電圧波形を観測した。また、各試料において、ターンオフ損失およびターンオフdv/dtを測定した。

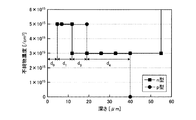

図22は、実施例5にかかる半導体装置のp型不純物濃度分布を示す特性図である。また、図23は、実施例5にかかる半導体装置における電気的特性を示す特性図である。また、図24は、実施例5にかかる半導体装置におけるターンオフ時の電気的特性を示す特性図である。まず、図22に示すように第1深さd0の下端から第2主面側にかけて、実施の形態5に従い、p型中濃度領域25(第4深さd3)の不純物濃度を、3.0×1015/cm3、3.5×1015/cm3、4.0×1015/cm3、4.5×1015/cm3、5.0×1015/cm3とした、5つのプレーナ型MOSFETを準備した(以下、第5実施例〜第9実施例とする)。また、第5実施例〜第9実施例では、p型高濃度領域23の厚さ(第2深さd1)を9μmとした。p型中濃度領域25の厚さ(第4深さd3)を7μmとした。それ以外の構成は、第4実施例と同様である。また、比較として、実施例1と同様に、従来例を準備した。そして、第5実施例〜第9実施例において、アバランシェ突入後の電流−電圧波形を観測した。また、第5実施例〜第9実施例および従来例において、ターンオフ損失およびターンオフdv/dtを測定した。

図25は、実施例6にかかる半導体装置の不純物濃度分布を示す特性図である。また、図26は、実施例6にかかる半導体装置における電気的特性を示す特性図である。また、図27−1、図27−2は、実施例6にかかる半導体装置におけるターンオフ時の電気的特性を示す特性図である。まず、図25に示すように、実施の形態6に従い、p型低濃度領域24の不純物濃度を、第1主面側から第2主面側にかけて徐々に低くしたプレーナ型MOSFETを準備した(以下、第10実施例とする)。第10実施例では、n型高濃度領域21の不純物濃度を7.5×1015/cm3とした。n型低濃度領域22の不純物濃度を3.0×1015/cm3とした。つまり、n型高濃度領域21の不純物濃度を、n型低濃度領域22の不純物濃度の2.5倍とした。p型高濃度領域23の不純物濃度を1.5×1016/cm3とした。p型低濃度領域24の不純物濃度を、第1主面側で6.6×1015/cm3、第2主面側で5.4×1015/cm3とし、第1主面側から第2主面側にかけて0.3×1015/cm3ずつ減少する不純物濃度分布とした。p型領域2内の不純物濃度を変更するp型領域2の上端からの深さ(以下、濃度変更深さとする)、つまり、p型高濃度領域23の厚さを5μmとした。また、p型低濃度領域24の不純物濃度を、第1主面側で7.2×1015/cm3、第2主面側で4.8×1015/cm3とし、第1主面側から第2主面側にかけて0.6×1015/cm3ずつ減少する不純物濃度分布とし、その他は第10実施例と同様である第10−1実施例も準備した。更に、n型高濃度領域21の不純物濃度を3.6×1015/cm3とし、n型低濃度領域22の不純物濃度を3.0×1015/cm3とし、n型高濃度領域21の不純物濃度を、n型低濃度領域22の不純物濃度の1.2倍とし、p型高濃度領域23の不純物濃度を7.2×1015/cm3とし、p型低濃度領域24の不純物濃度を6.0×1015/cm3とし、p型高濃度領域23の不純物濃度をp型低濃度領域24の不純物濃度の1.2倍として、その他は第10実施例と同様である第10−2実施例も準備した。比較として、実施例1と同様に、従来例を準備した。また、p型低濃度領域24の不純物濃度分布が均一なプレーナ型MOSFETを準備した(以下、第1比較例とする)。第1比較例では、p型低濃度領域24の不純物濃度を6.0×1015/cm3とした。それ以外の構成は、第10実施例と同様である。そして、各試料において、耐圧およびオン抵抗を測定した。また、各試料において、ターンオフ損失およびターンオフdv/dtを測定した。なお、図25では、ネットドーピング(正味のキャリア濃度)で示している。つまり、半導体基板の全面にリンでn型領域を形成し、ボロンを導入してp型領域を形成しているので、図25におけるp型領域のネットドーピングは、ボロン濃度からリン濃度を差し引いた値である。

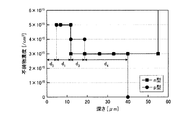

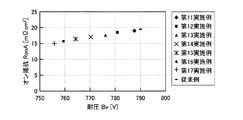

図28−1および図28−2は、実施例7にかかる半導体装置における電気的特性を示す特性図である。また、図29−1および図29−2は、実施例7にかかる半導体装置におけるターンオフ時の電気的特性を示す特性図である。まず、実施の形態6に従い、濃度変更深さ(n型高濃度領域21の厚さ)を1μm、5μm、10μm、15μm、20μm、25μm、30μmとした、7つのプレーナ型MOSFETを準備した(以下、第11実施例〜第17実施例とする)。第11実施例〜第17実施例では、p型高濃度領域23の厚さは、それぞれのn型高濃度領域21と同様である。n型高濃度領域21の不純物濃度を4.5×1015/cm3とした。n型領域1の第1主面側の不純物濃度を3.0×1015/cm3とした。p型高濃度領域23の不純物濃度を9.0×1015/cm3とし、p型低濃度領域24の不純物濃度を6.0×1015/cm3とした。それ以外の構成は、実施例6と同様である。また、第11実施例〜第17実施例の変形例として、濃度変更深さ(n型高濃度領域21の厚さ)を1μm、5μm、10μm、15μm、20μm、25μm、30μmとし、n型高濃度領域21の不純物濃度を7.5×1015/cm3とし、n型領域1の第1主面側の不純物濃度を3.0×1015/cm3とし、p型高濃度領域23の不純物濃度を1.5×1016/cm3とし、p型低濃度領域24の不純物濃度を6.0×1015/cm3とした濃度差2倍の7つのプレーナ型MOSFETを準備した(以下、第11−1実施例〜第17−1実施例とする)。比較として、実施例1と同様に、従来例を準備した。そして、各試料において、耐圧およびオン抵抗を測定した。また、各試料において、ターンオフ損失およびターンオフdv/dtを測定した。

図30は、実施例8にかかる半導体装置におけるターンオフ時の電気的特性を示す特性図である。まず、実施の形態6に従い、n型高濃度領域21の不純物濃度をn型低濃度領域22の不純物濃度の1.33倍、1.67倍、2倍、2.33倍とした、4つのプレーナ型MOSFETを準備した(以下、第18実施例〜第21実施例とする)。また、実施例6と同様に、n型高濃度領域21の不純物濃度をn型低濃度領域22の不純物濃度の2.5倍とした第10実施例を準備した。そして、各試料において、ターンオフ損失およびターンオフdv/dtを測定した。図30に示す結果より、n型高濃度領域21の不純物濃度の、n型低濃度領域22の不純物濃度に対する割合が高いほど、ターンオフ損失とターンオフdv/dtとのトレードオフ関係を改善することができることがわかった。また、第18実施例〜第21実施例では、ターンオフ損失とターンオフdv/dtとのトレードオフ関係をほぼ同様に改善することができる。また、第10実施例において、不純物濃度比を3倍とし、p型低濃度領域24の不純物濃度を、第1主面側から第2主面側にかけて0.45×1015/cm3ずつ減少する不純物濃度分布とした実施例で600Vの耐圧を確認した。これらより、n型高濃度領域21の不純物濃度の、n型低濃度領域22の不純物濃度に対する割合は、1.2倍以上3倍以下好ましくは2.5倍以下とすることがよいことがわかる。

SJ−MOSFETを製造する主な方法としては多段エピ方式とトレンチ埋め込み方式とがある。トレンチ埋め込み方式ではnエピ層に深掘りトレンチを1回形成してp型エピ層を埋め込むだけで並列pn構造をつくることができるので、多段エピ方式よりも簡便である。

図33は、実施の形態8にかかる半導体装置の製造工程を順に示した断面図である。まず、図31(a)〜(d)と同様な手順で製造を行う。ただし、続く工程ではまず、低濃度pエピ層47表面はエッチバックせずに、図33(a)に示すように深掘りトレンチ46内部に埋め込んだ低濃度pエピ層47の上に高濃度p層55を形成する。続いて、図33(b)に示すように化学機械研磨(CMP)などで表面の平坦化を行う。これより後の工程である図33(c)は前記実施の形態1のプレーナMOS構造を形成する工程と同じ工程に従い、最終デバイス形状が得られる。つまり、実施の形態8は、実施の形態7において図32(a)に示した低濃度pエピ層47のエッチバックを省いた製造方法であるので、実施の形態7よりも工程を簡便化することができる。

実施の形態7と実施の形態8ではn型表面領域43と高濃度p層48,55の深さが概ね等しかったが、アバランシェ耐量を上げるためには高濃度p層48,55がn型表面領域43よりも深くなるように形成すればよい。

なお、実施の形態9にかかる半導体装置の製造工程を、実施の形態2にかかる半導体装置を作製する製造方法に当てはめた場合の製造工程の断面図は図35のようになる。図35は、実施の形態10にかかる半導体装置の製造工程を順に示した断面図である。まず、図31(a)〜(c)と同様な手順で製造を行う。次に、図35(a)では図34(a)と同様に、深掘りトレンチ46内部に低濃度pエピ層47をエピタキシャル成長で埋め込む。続く図35(b)の工程では低濃度pエピ層47のエッチバックは行わず、低濃度pエピ層47の上に高濃度p層55を形成する。その後、図35(c)に示すようにCMPなどで表面の平坦化を行う。最終デバイス形状は図35(d)のようになる。

実施の形態9において高濃度p層48を深くする代わりにn型表面領域43と高濃度p層57の深さが概ね同じになるようにし、高濃度p層57と低濃度pエピ層47との間に中濃度p層56を設けてもかまわない。このような構造としたのが、実施の形態11である。

実施の形態10にかかる半導体装置の製造工程を、実施の形態8にかかる半導体装置の製造工程に用いた場合の製造工程の主要断面図は図38のようになる。図38は、実施の形態12にかかる半導体装置の製造工程を順に示した断面図である。まず、図31(a)〜(c)と同様な手順で製造を行う。次に、図38(a)のように深掘りトレンチ46内部に低濃度pエピ層47をエピタキシャル成長で埋め込む。さらに、図38(b)に示すように、低濃度pエピ層47の内部に中濃度p層58をエピタキシャル成長で埋め込む。続いて、図38(c)に示すように、低濃度pエピ層47の内部に高濃度p層59をエピタキシャル成長で埋め込む。その後、図38(d)に示すようにCMPなどで表面の平坦化を行う。最終デバイス形状は図38(e)のようになる。

2 p型領域

3 pベース領域

4 n型表面領域

5 p+コンタクト領域

6 n+ソース領域

7 ゲート絶縁膜

8 ゲート電極

9 層間絶縁膜

10 ソース電極

11 n+ドレイン領域

12 ドレイン電極

20 並列pn層

21 n型高濃度領域

22 n型低濃度領域

Claims (20)

- 第1主面側に設けられた素子活性部と、

第2主面側に設けられた低抵抗層と、

前記素子活性部と前記低抵抗層との間に設けられ、第1導電型領域および第2導電型領域が交互に配置された並列pn層と、

前記第2導電型領域の前記第1主面側に設けられ、当該第2導電型領域よりも高い不純物濃度を有する第2導電型ベース領域と、

前記第1導電型領域の前記第1主面側に設けられ、前記第2導電型ベース領域の前記第2主面側の端部よりも当該第2主面側に位置し、当該第1導電型領域の当該第2主面側の不純物濃度よりも高い不純物濃度を有する第1導電型高濃度領域と、

を備えることを特徴とする半導体装置。 - 前記第1導電型高濃度領域は、前記第2導電型ベース領域の前記第2主面側の端部から前記第2導電型領域の第2主面側の端部までの深さに位置する前記第1導電型領域のうち、当該第1導電型高濃度領域を除く領域の1.2倍以上3倍以下の不純物濃度を有することを特徴とする請求項1に記載の半導体装置。

- 前記第1導電型領域の前記第1主面側に設けられ、前記第1導電型高濃度領域の前記第1主面側の端部に接する第1導電型表面領域を、さらに備えることを特徴とする請求項1に記載の半導体装置。

- 前記第1導電型表面領域は、前記第2導電型ベース領域と同じ深さ、または前記第2導電型ベース領域よりも前記第1主面側に浅く設けられていることを特徴とする請求項3に記載の半導体装置。

- 前記第1導電型表面領域は、前記第1導電型高濃度領域よりも高い不純物濃度を有することを特徴とする請求項3に記載の半導体装置。

- 前記第1導電型高濃度領域は、前記第1導電型表面領域も含めて、前記第2導電型ベース領域の第2主面側の端部から前記第2導電型領域の第2主面側の端部までの深さに位置する前記第1導電型領域のうち、当該第1導電型高濃度領域を除く領域の1.2倍以上3倍以下の不純物濃度を有することを特徴とする請求項3に記載の半導体装置。

- 前記第1導電型高濃度領域は、前記第2導電型ベース領域の前記第2主面側の端部から前記第2導電型領域の第2主面側の端部までの深さに位置する前記第1導電型領域の厚さの1/3以下の厚さを有することを特徴とする請求項1に記載の半導体装置。

- 前記第1導電型高濃度領域は、前記第2導電型ベース領域の前記第2主面側の端部から前記第2導電型領域の第2主面側の端部までの深さに位置する前記第1導電型領域の厚さの1/8以上1/4以下の厚さを有することを特徴とする請求項1に記載の半導体装置。

- 前記第1導電型高濃度領域は、前記第2導電型領域のうち当該第1導電型高濃度領域の隣接する領域の1.2倍以上3倍以下の不純物濃度を有することを特徴とする請求項1に記載の半導体装置。

- 前記第2導電型領域のうち、前記第2主面側の不純物濃度よりも高い不純物濃度を有する前記第1主面側の第2導電型高濃度領域を、さらに備えることを特徴とする請求項1に記載の半導体装置。

- 前記第1導電型高濃度領域は、前記第2導電型ベース領域の前記第2主面側の端部から前記第2導電型領域の第2主面側の端部までの深さに位置する前記第1導電型領域のうち、当該第1導電型高濃度領域を除く領域の1.5倍以上3倍以下の不純物濃度を有することを特徴とする請求項10に記載の半導体装置。

- 前記第2導電型高濃度領域は、前記第2導電型領域の厚さの1/8以上1/2以下の厚さを有することを特徴とする請求項10に記載の半導体装置。

- 前記第2導電型高濃度領域は、前記第1導電型高濃度領域と同じ厚さを有することを特徴とする請求項10に記載の半導体装置。

- 前記第2導電型領域のうち前記第2導電型高濃度領域を除く領域は、前記第1導電型領域のうち前記第1導電型高濃度領域を除く領域と同じ不純物量を有することを特徴とする請求項10に記載の半導体装置。

- 前記第2導電型領域のうち前記第2導電型高濃度領域を除く領域は、前記第1主面側から前記第2主面側にかけて、不純物濃度が徐々に低くなっていることを特徴とする請求項10に記載の半導体装置。

- 前記第1導電型高濃度領域および前記第2導電型高濃度領域が、前記第1主面側から前記第2主面側にかけて、不純物濃度が徐々に低くなっていることを特徴とする請求項10に記載の半導体装置。

- 前記第2導電型高濃度領域は、前記第1導電型高濃度領域の前記第2主面側の端部よりも当該第2主面側に深く設けられていることを特徴とする請求項10に記載の半導体装置。

- 前記第2導電型高濃度領域のうち、前記第1導電型高濃度領域の前記第2主面側の端部よりも当該第2主面側に深く設けられている領域は、当該領域の隣接する前記第1導電型領域よりも高い不純物濃度を有し、かつ当該第2導電型高濃度領域よりも低い不純物濃度を有することを特徴とする請求項17に記載の半導体装置。

- 前記第2導電型高濃度領域のうち、前記第1導電型高濃度領域の前記第2主面側の端部よりも当該第2主面側に深く設けられている領域は、当該領域の隣接する前記第1導電型領域の1.2倍以上の不純物濃度を有することを特徴とする請求項17に記載の半導体装置。

- 前記第1導電型領域および前記第2導電型領域の平面形状は、ストライプ状、六方格子状または正方状であることを特徴とする請求項1〜19のいずれか一つに記載の半導体装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2011551946A JP5652407B2 (ja) | 2010-01-29 | 2011-01-28 | 半導体装置および半導体装置の製造方法 |

Applications Claiming Priority (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2010017901 | 2010-01-29 | ||

| JP2010017901 | 2010-01-29 | ||

| JP2011551946A JP5652407B2 (ja) | 2010-01-29 | 2011-01-28 | 半導体装置および半導体装置の製造方法 |

| PCT/JP2011/051831 WO2011093473A1 (ja) | 2010-01-29 | 2011-01-28 | 半導体装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JPWO2011093473A1 true JPWO2011093473A1 (ja) | 2013-06-06 |

| JP5652407B2 JP5652407B2 (ja) | 2015-01-14 |

Family

ID=44319451

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2011551946A Active JP5652407B2 (ja) | 2010-01-29 | 2011-01-28 | 半導体装置および半導体装置の製造方法 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US9087893B2 (ja) |

| EP (1) | EP2530721A4 (ja) |

| JP (1) | JP5652407B2 (ja) |

| CN (1) | CN102804386B (ja) |

| WO (1) | WO2011093473A1 (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9536943B2 (en) * | 2012-10-24 | 2017-01-03 | Renesas Electronics Corporation | Vertical power MOSFET |

Families Citing this family (36)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20120273916A1 (en) | 2011-04-27 | 2012-11-01 | Yedinak Joseph A | Superjunction Structures for Power Devices and Methods of Manufacture |

| JP5740108B2 (ja) | 2010-07-16 | 2015-06-24 | 株式会社東芝 | 半導体装置 |

| WO2012149195A1 (en) | 2011-04-27 | 2012-11-01 | Fairchild Semiconductor Corporation | Superjunction structures for power devices and methods of manufacture |

| CN102832245B (zh) * | 2011-11-29 | 2014-12-10 | 电子科技大学 | 一种具有优化雪崩击穿电流路径的超结mosfet器件 |

| TWI487110B (zh) * | 2012-01-05 | 2015-06-01 | 世界先進積體電路股份有限公司 | 半導體裝置及其製造方法 |

| JP5812029B2 (ja) | 2012-06-13 | 2015-11-11 | 株式会社デンソー | 炭化珪素半導体装置およびその製造方法 |

| CN104254920B (zh) | 2012-07-19 | 2017-03-08 | 富士电机株式会社 | 半导体装置及半导体装置的制造方法 |

| CN102881595B (zh) * | 2012-08-17 | 2015-10-28 | 西安龙腾新能源科技发展有限公司 | 一种超结高压功率器件的制造方法 |

| US9035376B2 (en) * | 2013-02-14 | 2015-05-19 | Fuji Electric Co., Ltd. | Semiconductor device and method of manufacturing the same |

| US8901623B2 (en) * | 2013-02-18 | 2014-12-02 | Infineon Technologies Austria Ag | Super junction semiconductor device with overcompensation zones |

| JP6135178B2 (ja) | 2013-02-25 | 2017-05-31 | 富士電機株式会社 | 超接合半導体装置の製造方法 |

| CN103199104B (zh) * | 2013-03-05 | 2016-04-27 | 矽力杰半导体技术(杭州)有限公司 | 一种晶圆结构以及应用其的功率器件 |

| JP2014187200A (ja) * | 2013-03-22 | 2014-10-02 | Toshiba Corp | 半導体装置の製造方法 |

| TWI488309B (zh) * | 2013-05-31 | 2015-06-11 | 碩頡科技股份有限公司 | 溝渠式閘極金氧半場效電晶體及其製造方法 |

| CN104241127A (zh) * | 2013-06-06 | 2014-12-24 | 硕颉科技股份有限公司 | 沟道式栅极金氧半场效晶体管及其制造方法 |

| CN103489908A (zh) * | 2013-09-16 | 2014-01-01 | 电子科技大学 | 一种能消除负阻效应的rc-igbt |

| JP5821925B2 (ja) * | 2013-10-21 | 2015-11-24 | トヨタ自動車株式会社 | バイポーラトランジスタ |

| DE102013112887B4 (de) * | 2013-11-21 | 2020-07-09 | Infineon Technologies Ag | Halbleitervorrichtung und Verfahren zum Herstellen einer Halbleitervorrichtung |

| JP6341074B2 (ja) * | 2014-01-24 | 2018-06-13 | 株式会社デンソー | 半導体装置の製造方法 |

| JP6324805B2 (ja) * | 2014-05-19 | 2018-05-16 | ルネサスエレクトロニクス株式会社 | 半導体装置およびその製造方法 |

| JP2015233089A (ja) * | 2014-06-10 | 2015-12-24 | 株式会社サイオクス | 化合物半導体素子用エピタキシャルウェハ及び化合物半導体素子 |

| JP6375743B2 (ja) * | 2014-07-15 | 2018-08-22 | 富士電機株式会社 | 半導体装置の製造方法 |

| JP6301861B2 (ja) | 2014-07-31 | 2018-03-28 | 株式会社東芝 | 半導体装置 |

| JP6782529B2 (ja) * | 2015-01-29 | 2020-11-11 | 富士電機株式会社 | 半導体装置 |

| JP2016174041A (ja) * | 2015-03-16 | 2016-09-29 | 株式会社東芝 | 半導体装置 |

| KR102117465B1 (ko) * | 2015-04-09 | 2020-06-02 | 삼성전기주식회사 | 반도체 소자 및 그 제조 방법 |

| JP6557123B2 (ja) * | 2015-11-26 | 2019-08-07 | ルネサスエレクトロニクス株式会社 | 半導体装置の製造方法 |

| CN107482061B (zh) * | 2016-06-08 | 2020-12-04 | 深圳尚阳通科技有限公司 | 超结器件及其制造方法 |

| JP2019054169A (ja) * | 2017-09-15 | 2019-04-04 | 株式会社東芝 | 半導体装置 |

| US10600649B2 (en) | 2017-09-21 | 2020-03-24 | General Electric Company | Systems and method for charge balanced semiconductor power devices with fast switching capability |

| JP2019161103A (ja) * | 2018-03-15 | 2019-09-19 | 株式会社東芝 | 半導体装置 |

| US11056586B2 (en) * | 2018-09-28 | 2021-07-06 | General Electric Company | Techniques for fabricating charge balanced (CB) trench-metal-oxide-semiconductor field-effect transistor (MOSFET) devices |

| KR102244200B1 (ko) * | 2019-11-29 | 2021-04-26 | 서강대학교산학협력단 | Mosfet 소자 및 그 제조 방법 |

| CN114914359A (zh) * | 2022-06-13 | 2022-08-16 | 北京智芯传感科技有限公司 | 一种纳秒级体负阻效应的微型半导体短路开关 |

| DE102022119520B4 (de) | 2022-08-03 | 2025-12-31 | Infineon Technologies Austria Ag | Verfahren zum herstellen eines superjunction-bauelements und superjunction-transistor-bauelement |

| CN119451149B (zh) * | 2025-01-08 | 2025-05-02 | 天狼芯半导体(成都)有限公司 | 一种绝缘栅双极型晶体管及其制备方法 |

Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS62150769A (ja) * | 1985-12-24 | 1987-07-04 | Fuji Electric Co Ltd | 半導体装置 |

| JP2000040822A (ja) * | 1998-07-24 | 2000-02-08 | Fuji Electric Co Ltd | 超接合半導体素子およびその製造方法 |

| JP2006066421A (ja) * | 2004-08-24 | 2006-03-09 | Toshiba Corp | 半導体装置およびその製造方法 |

| JP2007019146A (ja) * | 2005-07-06 | 2007-01-25 | Toshiba Corp | 半導体素子 |

| JP2007150142A (ja) * | 2005-11-30 | 2007-06-14 | Toshiba Corp | 半導体装置 |

| JP2008091450A (ja) * | 2006-09-29 | 2008-04-17 | Toshiba Corp | 半導体素子 |

Family Cites Families (27)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4803533A (en) * | 1986-09-30 | 1989-02-07 | General Electric Company | IGT and MOSFET devices having reduced channel width |

| CN1019720B (zh) | 1991-03-19 | 1992-12-30 | 电子科技大学 | 半导体功率器件 |

| DE4309764C2 (de) | 1993-03-25 | 1997-01-30 | Siemens Ag | Leistungs-MOSFET |

| US6097063A (en) | 1996-01-22 | 2000-08-01 | Fuji Electric Co., Ltd. | Semiconductor device having a plurality of parallel drift regions |

| JPH09266311A (ja) | 1996-01-22 | 1997-10-07 | Fuji Electric Co Ltd | 半導体装置及びその製造方法 |

| US6081009A (en) | 1997-11-10 | 2000-06-27 | Intersil Corporation | High voltage mosfet structure |

| US6563169B1 (en) * | 1999-04-09 | 2003-05-13 | Shindengen Electric Manufacturing Co., Ltd. | Semiconductor device with high withstand voltage and a drain layer having a highly conductive region connectable to a diffused source layer by an inverted layer |

| JP4240752B2 (ja) * | 2000-05-01 | 2009-03-18 | 富士電機デバイステクノロジー株式会社 | 半導体装置 |

| JP4635304B2 (ja) * | 2000-07-12 | 2011-02-23 | 富士電機システムズ株式会社 | 双方向超接合半導体素子およびその製造方法 |

| KR100485297B1 (ko) * | 2001-02-21 | 2005-04-27 | 미쓰비시덴키 가부시키가이샤 | 반도체 장치 및 그 제조 방법 |

| JP4839519B2 (ja) * | 2001-03-15 | 2011-12-21 | 富士電機株式会社 | 半導体装置 |

| JP4126915B2 (ja) * | 2002-01-30 | 2008-07-30 | 富士電機デバイステクノロジー株式会社 | 半導体装置 |

| JP4304433B2 (ja) | 2002-06-14 | 2009-07-29 | 富士電機デバイステクノロジー株式会社 | 半導体素子 |

| JP3634830B2 (ja) * | 2002-09-25 | 2005-03-30 | 株式会社東芝 | 電力用半導体素子 |

| DE10245049B4 (de) * | 2002-09-26 | 2007-07-05 | Infineon Technologies Ag | Kompensationshalbleiterbauelement |

| DE10346838A1 (de) * | 2002-10-08 | 2004-05-13 | International Rectifier Corp., El Segundo | Superjunction-Bauteil |

| US7166890B2 (en) | 2003-10-21 | 2007-01-23 | Srikant Sridevan | Superjunction device with improved ruggedness |

| JP4289123B2 (ja) * | 2003-10-29 | 2009-07-01 | 富士電機デバイステクノロジー株式会社 | 半導体装置 |

| JP4734021B2 (ja) | 2004-05-11 | 2011-07-27 | 昭和電工株式会社 | 熱交換器 |

| JP4068597B2 (ja) * | 2004-07-08 | 2008-03-26 | 株式会社東芝 | 半導体装置 |

| JP4768259B2 (ja) | 2004-12-21 | 2011-09-07 | 株式会社東芝 | 電力用半導体装置 |

| EP1696490A1 (en) * | 2005-02-25 | 2006-08-30 | STMicroelectronics S.r.l. | Charge compensation semiconductor device and relative manufacturing process |

| JP4939760B2 (ja) * | 2005-03-01 | 2012-05-30 | 株式会社東芝 | 半導体装置 |

| JP5369372B2 (ja) | 2005-11-28 | 2013-12-18 | 富士電機株式会社 | 半導体装置および半導体装置の製造方法 |

| DE102006055131A1 (de) | 2005-11-28 | 2007-06-06 | Fuji Electric Holdings Co., Ltd., Kawasaki | Halbleiterbauteil und Verfahren zu seiner Herstellung |

| US20080017897A1 (en) * | 2006-01-30 | 2008-01-24 | Kabushiki Kaisha Toshiba | Semiconductor device and method of manufacturing same |

| JP2007281034A (ja) * | 2006-04-03 | 2007-10-25 | Toshiba Corp | 電力用半導体素子 |

-

2011

- 2011-01-28 EP EP11737183.1A patent/EP2530721A4/en active Pending

- 2011-01-28 JP JP2011551946A patent/JP5652407B2/ja active Active

- 2011-01-28 WO PCT/JP2011/051831 patent/WO2011093473A1/ja not_active Ceased

- 2011-01-28 US US13/575,984 patent/US9087893B2/en active Active

- 2011-01-28 CN CN201180007576.5A patent/CN102804386B/zh active Active

Patent Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS62150769A (ja) * | 1985-12-24 | 1987-07-04 | Fuji Electric Co Ltd | 半導体装置 |

| JP2000040822A (ja) * | 1998-07-24 | 2000-02-08 | Fuji Electric Co Ltd | 超接合半導体素子およびその製造方法 |

| JP2006066421A (ja) * | 2004-08-24 | 2006-03-09 | Toshiba Corp | 半導体装置およびその製造方法 |

| JP2007019146A (ja) * | 2005-07-06 | 2007-01-25 | Toshiba Corp | 半導体素子 |

| JP2007150142A (ja) * | 2005-11-30 | 2007-06-14 | Toshiba Corp | 半導体装置 |

| JP2008091450A (ja) * | 2006-09-29 | 2008-04-17 | Toshiba Corp | 半導体素子 |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9536943B2 (en) * | 2012-10-24 | 2017-01-03 | Renesas Electronics Corporation | Vertical power MOSFET |

Also Published As

| Publication number | Publication date |

|---|---|

| EP2530721A4 (en) | 2017-11-29 |

| US9087893B2 (en) | 2015-07-21 |

| US20130026560A1 (en) | 2013-01-31 |

| CN102804386A (zh) | 2012-11-28 |

| CN102804386B (zh) | 2016-07-06 |

| WO2011093473A1 (ja) | 2011-08-04 |

| EP2530721A1 (en) | 2012-12-05 |

| JP5652407B2 (ja) | 2015-01-14 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5652407B2 (ja) | 半導体装置および半導体装置の製造方法 | |

| US20250267902A1 (en) | Superjunction silicon carbide semiconductor device having parallel pn column structure with crystal defects | |

| JP5002148B2 (ja) | 半導体装置 | |

| JP3964819B2 (ja) | 絶縁ゲート型半導体装置 | |

| CN102804385B (zh) | 半导体器件 | |

| JP4764987B2 (ja) | 超接合半導体素子 | |

| KR101396611B1 (ko) | 반도체 장치 | |

| JP2018107168A (ja) | 半導体装置および半導体装置の製造方法 | |

| WO2018164817A1 (en) | Vertical power mos-gated device with high dopant concentration n-well below p-well and with floating p-islands | |

| US20090273031A1 (en) | Semiconductor device | |

| CN111769158B (zh) | 一种具低反向恢复电荷的双沟道超结vdmos器件及制造方法 | |

| JP2010147477A (ja) | シリコンウェハ上にパワートランジスタデバイスを製造する方法 | |

| JP2014056942A (ja) | 電力用半導体装置 | |

| JP2012089824A (ja) | 半導体素子およびその製造方法 | |

| CN111933690B (zh) | 一种功率器件及其制作方法 | |

| JP2025107491A (ja) | 超接合半導体装置 | |

| CN107534053A (zh) | 半导体装置及其制造方法 | |

| JP2021168379A (ja) | フォワード・リカバリ電圧が低減された逆導通igbt | |

| CN114651335B (zh) | 绝缘栅双极晶体管 | |

| WO2017010164A1 (ja) | 電力用半導体装置 | |

| CN115064584A (zh) | 一种具有载流子存储层的沟槽栅igbt器件 | |

| JP2014154739A (ja) | 半導体装置 | |

| US9245986B2 (en) | Power semiconductor device and method of manufacturing the same | |

| CN112018174A (zh) | 一种半导体器件及其制作方法、家用电器 | |

| US20250280593A1 (en) | Semiconductor device |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20140128 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20140328 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20140805 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20140929 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20141021 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20141103 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5652407 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |