WO2024202425A1 - 絶縁スイッチ及びシーケンサ - Google Patents

絶縁スイッチ及びシーケンサ Download PDFInfo

- Publication number

- WO2024202425A1 WO2024202425A1 PCT/JP2024/001304 JP2024001304W WO2024202425A1 WO 2024202425 A1 WO2024202425 A1 WO 2024202425A1 JP 2024001304 W JP2024001304 W JP 2024001304W WO 2024202425 A1 WO2024202425 A1 WO 2024202425A1

- Authority

- WO

- WIPO (PCT)

- Prior art keywords

- circuit

- secondary coil

- coil

- signal

- switch

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Ceased

Links

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K17/00—Electronic switching or gating, i.e. not by contact-making and –breaking

- H03K17/51—Electronic switching or gating, i.e. not by contact-making and –breaking characterised by the components used

- H03K17/56—Electronic switching or gating, i.e. not by contact-making and –breaking characterised by the components used by the use, as active elements, of semiconductor devices

- H03K17/687—Electronic switching or gating, i.e. not by contact-making and –breaking characterised by the components used by the use, as active elements, of semiconductor devices the devices being field-effect transistors

- H03K17/689—Electronic switching or gating, i.e. not by contact-making and –breaking characterised by the components used by the use, as active elements, of semiconductor devices the devices being field-effect transistors with galvanic isolation between the control circuit and the output circuit

- H03K17/691—Electronic switching or gating, i.e. not by contact-making and –breaking characterised by the components used by the use, as active elements, of semiconductor devices the devices being field-effect transistors with galvanic isolation between the control circuit and the output circuit using transformer coupling

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K17/00—Electronic switching or gating, i.e. not by contact-making and –breaking

- H03K17/08—Modifications for protecting switching circuit against overcurrent or overvoltage

- H03K17/082—Modifications for protecting switching circuit against overcurrent or overvoltage by feedback from the output to the control circuit

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K17/00—Electronic switching or gating, i.e. not by contact-making and –breaking

- H03K17/51—Electronic switching or gating, i.e. not by contact-making and –breaking characterised by the components used

- H03K17/56—Electronic switching or gating, i.e. not by contact-making and –breaking characterised by the components used by the use, as active elements, of semiconductor devices

- H03K17/687—Electronic switching or gating, i.e. not by contact-making and –breaking characterised by the components used by the use, as active elements, of semiconductor devices the devices being field-effect transistors

- H03K17/689—Electronic switching or gating, i.e. not by contact-making and –breaking characterised by the components used by the use, as active elements, of semiconductor devices the devices being field-effect transistors with galvanic isolation between the control circuit and the output circuit

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K17/00—Electronic switching or gating, i.e. not by contact-making and –breaking

- H03K17/51—Electronic switching or gating, i.e. not by contact-making and –breaking characterised by the components used

- H03K17/74—Electronic switching or gating, i.e. not by contact-making and –breaking characterised by the components used by the use, as active elements, of diodes

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K19/00—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits

- H03K19/0175—Coupling arrangements; Interface arrangements

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L25/00—Baseband systems

- H04L25/02—Details ; arrangements for supplying electrical power along data transmission lines

Definitions

- This disclosure relates to an insulating switch and a sequencer using an insulating switch. This disclosure also relates to a signal transmission device.

- signal transmission devices that transmit signals between a primary circuit system and a secondary circuit system while electrically insulating the primary circuit system and the secondary circuit system have been used in various applications (such as power supplies or motor drive devices).

- Patent Document 2 As an example of related prior art, see Patent Document 2 by the same applicant as the present application.

- JP 2020-096051 A International Publication No. 2022/070944

- conventional signal transmission devices can cause problems in transmitting signals from the primary circuit system to the secondary circuit system if the power supply for the primary circuit system is unstable or insufficient.

- the insulating switch includes a switch unit configured to be controlled between a conductive state and a non-conductive state, a conduction circuit configured to control the switch unit to the conductive state, an adjustment circuit configured to adjust at least the switch unit from the conductive state to the non-conductive state, and a pulse supply circuit configured to receive a control signal and supply a pulse signal to at least one of the conduction circuit and the adjustment circuit.

- the conduction circuit includes a first insulating element having a first primary coil connected to the pulse supply circuit and a first secondary coil electromagnetically coupled to the first primary coil, and is configured to bring the switch unit into a conductive state by an induced current flowing at the rising edge of the pulse signal supplied to the first primary coil.

- the adjustment circuit includes a second insulating element having a second primary coil connected to the pulse supply circuit and a second secondary coil electromagnetically coupled to the second primary coil, and an adjustment element that adjusts the voltage of the control terminal of the switch unit by an induced current flowing in the second secondary coil at the rising edge of the pulse signal to bring the switch unit into the non-conductive state.

- the pulse supply circuit is configured to supply the pulse signal to the first primary coil when the control signal is at a first level, and to supply the pulse signal to the second primary coil from the point in time when the control signal switches from the first level to a second level different from the first level, and to set the switch unit to the conductive state when the control signal is at the first level.

- a signal transmission device configured to transmit a signal between a primary circuit system and a secondary circuit system while isolating the primary circuit system and the secondary circuit system, and includes a first insulating element configured to transmit a first signal from the secondary circuit system to the primary circuit system, a second insulating element configured to transmit a second signal from the primary circuit system to the secondary circuit system, a drive circuit provided in the secondary circuit system and configured to drive the first insulating element, a switch circuit provided in the primary circuit system and configured to switch the connection state between the first insulating element and the second insulating element in response to an input signal, and a receiving circuit configured to detect the second signal and generate an output signal in response to the input signal.

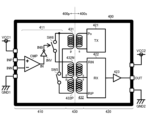

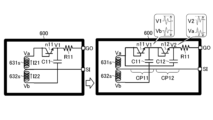

- FIG. 1 is a diagram showing a basic configuration of a signal transmission device.

- FIG. 2 is a diagram showing the basic structure of a transformer chip.

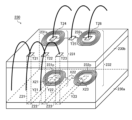

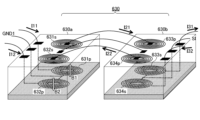

- FIG. 3 is a perspective view of a semiconductor device used as a two-channel type transformer chip.

- FIG. 4 is a plan view of the semiconductor device shown in FIG.

- FIG. 5 is a plan view showing a layer in which the low potential coil is formed in the semiconductor device of FIG.

- FIG. 6 is a plan view showing a layer in which a high potential coil is formed in the semiconductor device of FIG.

- FIG. 7 is a cross-sectional view taken along line VIII-VIII shown in FIG.

- FIG. 8 is an enlarged view (isolation structure) of the region XIII shown in FIG.

- FIG. 9 is a diagram illustrating an example of the layout of a transformer chip.

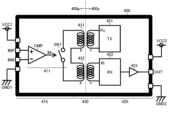

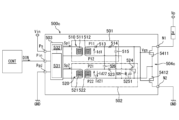

- FIG. 10 is a diagram showing a first embodiment of a signal transmission device.

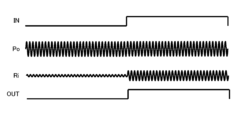

- FIG. 11 is a diagram illustrating a first operation example (intermittent) of the first embodiment.

- FIG. 12 is a diagram illustrating a second operation example (continuous) of the first embodiment.

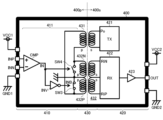

- FIG. 13 is a diagram showing a second embodiment of a signal transmission device.

- FIG. 14 is a diagram showing a third embodiment of a signal transmission device.

- FIG. 15 is a diagram illustrating an operation example of the third embodiment.

- FIG. 16 is a diagram showing a fourth embodiment of a signal transmission device.

- FIG. 17 is a diagram showing a fifth embodiment of a signal transmission device.

- FIG. 10 is a diagram showing a first embodiment of a signal transmission device.

- FIG. 11 is a diagram illustrating a first operation example (intermittent) of the first embodiment.

- FIG. 12 is a diagram illustrating

- FIG. 18 is a diagram showing a sixth embodiment of a signal transmission device.

- FIG. 19 is a diagram illustrating an operation example of the sixth embodiment.

- FIG. 20 is a diagram showing a seventh embodiment of a signal transmission device.

- FIG. 21 is a diagram showing an eighth embodiment of a signal transmission device.

- FIG. 22 is a diagram showing an operation example of the eighth embodiment.

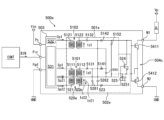

- FIG. 23 is a schematic circuit diagram of one form of an isolation switch according to an embodiment of the present disclosure.

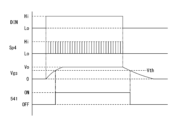

- FIG. 24 is a timing chart showing the operation of the isolation switch.

- FIG. 25 is a timing chart showing the operation of the isolation switch of the first modified example.

- FIG. 26 is a schematic circuit diagram of an isolation switch according to a second modified example.

- FIG. 27 is a timing chart showing the operation of the isolation switch of the second modified example.

- FIG. 28 is a schematic circuit diagram of an isolation switch according to a third modified example.

- FIG. 29 is a schematic circuit diagram of an isolation switch according to a fourth modified example.

- FIG. 30 is a schematic circuit diagram of an isolation switch according to a fifth modified example.

- FIG. 31 is a timing chart showing the operation of the isolation switch of the fifth modified example.

- FIG. 32 is a schematic circuit diagram of an isolation switch according to a sixth modified example.

- FIG. 331 is a schematic circuit diagram of another configuration example of the isolation switch of the sixth modified example.

- FIG. 34 is a schematic circuit diagram of an isolation switch according to a seventh modified example.

- FIG. 35 is a timing chart showing the operation of the isolation switch of the seventh modified example.

- FIG. 36 illustrates an additional embodiment of an isolation switch.

- FIG. 28 is a schematic circuit diagram of an isolation switch according to a third modified example.

- FIG. 29 is a schematic circuit diagram of an isolation switch according to a fourth modified example.

- FIG. 30 is a

- FIG. 37 is a diagram showing a first main part of an isolation switch according to an additional embodiment.

- FIG. 38 is a diagram showing an example of the operation of the first main part.

- FIG. 39 is a diagram showing a second main part of an isolation switch according to an additional embodiment.

- FIG. 40 is a diagram showing a third main part of an isolation switch according to an additional embodiment.

- FIG. 41 is a diagram showing a third tip in the third main portion.

- FIG. 42 is a diagram showing a modified example of the third main part.

- FIG. 43 is a diagram showing a third tip in a modified example of the third main part.

- FIG. 44 is a diagram showing a modified example of the second chip.

- FIG. 45 is a diagram showing an example of the operation of the second chip in the above modification.

- FIG. 45 is a diagram showing an example of the operation of the second chip in the above modification.

- FIG. 46 illustrates an additional embodiment of a signaling device.

- FIG. 47 is a diagram showing an example of the configuration of an isolated power supply circuit.

- FIG. 48 is a diagram showing a modified example of a signal transmission device according to an additional embodiment.

- FIG. 49 is a diagram showing a modified example of an isolated power supply circuit.

- FIG. 50 shows a modified example of an insulating element for percussion.

- connection includes mechanical connection as well as electrical connection, in other words, a state in which electricity flows.

- connection includes electrical connection.

- a line refers to a wiring through which an electrical signal is propagated or supplied.

- Ground potential refers to a reference conductive part having a reference potential of 0V (zero volts), or refers to the potential of 0V itself.

- the reference conductive part is formed of a conductor such as a metal.

- a potential of 0V is sometimes referred to as ground potential.

- a voltage indicated without any particular reference represents a potential seen from the ground potential.

- Level refers to the level of potential, and for any signal or voltage, the Hi level has a higher potential than the Lo level.

- Any digital signal has a signal level of Hi level or Lo level.

- a signal or voltage at Hi level strictly means that the signal or voltage level is at Hi level

- a signal or voltage at Lo level strictly means that the signal or voltage level is at Lo level.

- the level of a signal is sometimes expressed as a signal level

- the level of a voltage is sometimes expressed as a voltage level.

- the inverted signal of the signal is at Lo level

- the inverted signal of the signal is at Hi level.

- the Hi level may be referred to as the first level.

- the period during which the signal is Hi is called the Hi level period.

- the period during which the signal is Lo is called the Lo level period. The same applies to any voltage that has a Hi or Lo voltage level.

- a switching element can be in either an ON or OFF state.

- When a switching element is in the ON state there is electrical continuity between both ends of the switch.

- the period when a switching element is in the ON state is referred to as the ON period

- the period when a switching element is in the OFF state is referred to as the OFF period.

- switching to the ON state is sometimes referred to as turning ON

- switching to the OFF state is sometimes referred to as turning OFF.

- An example of a switching element may be a MOS (Metal Oxide Semiconductor) field effect transistor.

- MOS field effect transistor is a transistor whose gate structure consists of at least three layers: a layer made of a conductor or a semiconductor such as polysilicon with a low resistance value, an insulating layer, and a P-channel, N-channel, or intrinsic semiconductor layer.

- the gate structure of a MOS field effect transistor is not limited to a three-layer structure of metal, oxide, and semiconductor.

- MOS field effect transistors when in the ON state, the drain and source of the transistor are in a conductive state. Also, when in the OFF state, the drain and source of the transistor are in a non-conductive state (cut-off state). The same applies to transistors that are not classified as field effect transistors.

- MOS field effect transistor shown below the back gate is connected to the source unless otherwise specified. Note that in the following explanation, MOS field effect transistors may be simply referred to as MOS transistors.

- ⁇ Signal transmission device (basic configuration)> 1 is a diagram showing the basic configuration of a signal transmission device.

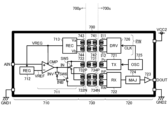

- the signal transmission device 200 of this configuration example is a semiconductor integrated circuit device (so-called insulated gate driver IC) that transmits a pulse signal from the primary circuit system 200p to the secondary circuit system 200s while isolating the primary circuit system 200p (VCC1-GND1 system) from the secondary circuit system 200s (VCC2-GND2 system) and drives the gate of a switch element (not shown) provided in the secondary circuit system 200s.

- the signal transmission device 200 is formed by sealing a controller chip 210, a driver chip 220, and a transformer chip 230 in a single package.

- the controller chip 210 is a semiconductor chip that operates by receiving a power supply voltage VCC1 (for example, up to 7 V based on GND1).

- the controller chip 210 includes, for example, a pulse transmission circuit 211 and buffers 212 and 213 integrated therein.

- the pulse transmission circuit 211 is a pulse generator that generates the transmission pulse signals S11 and S21 in response to the input pulse signal IN. More specifically, when the pulse transmission circuit 211 notifies that the input pulse signal IN is at a high level, it pulse drives the transmission pulse signal S11 (outputs a single or multiple transmission pulses), and when it notifies that the input pulse signal IN is at a low level, it pulse drives the transmission pulse signal S21. In other words, the pulse transmission circuit 211 pulse drives either the transmission pulse signal S11 or S21 in response to the logical level of the input pulse signal IN.

- the buffer 212 receives the transmission pulse signal S11 from the pulse transmission circuit 211 and pulse-drives the transformer chip 230 (specifically, the transformer 231).

- the buffer 213 receives the transmission pulse signal S21 from the pulse transmission circuit 211 and pulse-drives the transformer chip 230 (specifically, the transformer 232).

- the driver chip 220 is a semiconductor chip that operates by receiving a power supply voltage VCC2 (for example, up to 30 V based on GND2).

- the driver chip 220 includes, for example, buffers 221 and 222, a pulse receiving circuit 223, and a driver 224.

- the buffer 222 shapes the waveform of the received pulse signal S22 induced in the transformer chip 230 (specifically, the transformer 232) and outputs it to the pulse receiving circuit 223.

- the pulse receiving circuit 223 generates the output pulse signal OUT by driving the driver 224 in response to the received pulse signals S12 and S22 input via the buffers 221 and 222. More specifically, the pulse receiving circuit 223 drives the driver 224 so as to raise the output pulse signal OUT to a high level in response to the pulse drive of the received pulse signal S12, and to lower the output pulse signal OUT to a low level in response to the pulse drive of the received pulse signal S22. In other words, the pulse receiving circuit 223 switches the logical level of the output pulse signal OUT in response to the logical level of the input pulse signal IN.

- an RS flip-flop can be suitably used as the pulse receiving circuit 223.

- the driver 224 generates an output pulse signal OUT based on the drive control of the pulse receiving circuit 223.

- the transformer chip 230 uses transformers 231 and 232 to provide DC insulation between the controller chip 210 and the driver chip 220, and outputs the transmission pulse signals S11 and S21 input from the pulse transmission circuit 211 to the pulse reception circuit 223 as reception pulse signals S12 and S22, respectively.

- DC insulation means that the objects to be insulated are not connected by a conductor.

- the transformer 231 outputs a received pulse signal S12 from the secondary coil 231s in response to a transmitted pulse signal S11 input to the primary coil 231p.

- the transformer 232 outputs a received pulse signal S22 from the secondary coil 232s in response to a transmitted pulse signal S21 input to the primary coil 232p.

- the input pulse signal IN is separated into two transmission pulse signals S11 and S21 (corresponding to the rise signal and fall signal), and then transmitted from the primary circuit system 200p to the secondary circuit system 200s via the two transformers 231 and 232.

- the signal transmission device 200 of this configuration example has an independent transformer chip 230 equipped with only transformers 231 and 232, separate from the controller chip 210 and driver chip 220, and these three chips are sealed in a single package.

- the controller chip 210 and the driver chip 220 can both be formed using a general low to medium voltage process (withstands a few volts to a few tens of volts), eliminating the need to use a dedicated high voltage process (withstands a few kV), making it possible to reduce manufacturing costs.

- the signal transmission device 200 can be suitably used, for example, in a power supply device or a motor drive device for on-board equipment mounted in a vehicle.

- the above vehicles include not only engine vehicles, but also electric vehicles (BEVs [battery electric vehicles], HEVs [hybrid electric vehicles], PHEVs/PHVs (plug-in hybrid electric vehicles/plug-in hybrid vehicles), or xEVs such as FCEVs/FCVs (fuel cell electric vehicles/fuel cell vehicles)).

- FIG. 2 is a diagram showing the basic structure of the transformer chip 230.

- the transformer 231 includes a primary coil 231p and a secondary coil 231s that face each other in the vertical direction.

- the transformer 232 includes a primary coil 232p and a secondary coil 232s that face each other in the vertical direction.

- the primary coils 231p and 232p are both formed on the first wiring layer (lower layer) 230a of the transformer chip 230.

- the secondary coils 231s and 232s are both formed on the second wiring layer (upper layer in this figure) 230b of the transformer chip 230.

- the secondary coil 231s is disposed directly above the primary coil 231p and faces the primary coil 231p.

- the secondary coil 232s is disposed directly above the primary coil 232p and faces the primary coil 232p.

- the primary coil 231p is laid in a spiral shape starting from a first end connected to the internal terminal X21, surrounding the internal terminal X21 in a clockwise direction, and its second end corresponding to its end point is connected to the internal terminal X22.

- the primary coil 232p is laid in a spiral shape starting from a first end connected to the internal terminal X23, surrounding the internal terminal X23 in a counterclockwise direction, and its second end corresponding to its end point is connected to the internal terminal X22.

- the internal terminals X21, X22, and X23 are linearly arranged in the order shown.

- the internal terminal X21 is connected to the external terminal T21 of the second layer 230b via the conductive wiring Y21 and via Z21.

- the internal terminal X22 is connected to the external terminal T22 of the second layer 230b via the conductive wiring Y22 and via Z22.

- the internal terminal X23 is connected to the external terminal T23 of the second layer 230b via the conductive wiring Y23 and via Z23.

- the external terminals T21 to T23 are arranged in a straight line and are used for wire bonding with the controller chip 210.

- the secondary coil 231s is laid in a spiral shape starting from a first end connected to the external terminal T24, surrounding the external terminal T24 in a counterclockwise direction, and its second end corresponding to its end point is connected to the external terminal T25.

- the secondary coil 232s is laid in a spiral shape starting from a first end connected to the external terminal T26, surrounding the external terminal T26 in a clockwise direction, and its second end corresponding to its end point is connected to the external terminal T25.

- the external terminals T24, T25, and T26 are arranged linearly in the order shown in the figure, and are used for wire bonding with the driver chip 220.

- Secondary coils 231s and 232s are AC-connected to primary coils 231p and 232p by magnetic coupling, and are DC-insulated from primary coils 231p and 232p, respectively. That is, driver chip 220 is AC-connected to controller chip 210 via transformer chip 230, and is DC-insulated from controller chip 210 by transformer chip 230.

- FIG. 3 is a perspective view showing a semiconductor device 5 used as a two-channel transformer chip.

- FIG. 4 is a plan view of the semiconductor device 5 shown in FIG. 3.

- FIG. 5 is a plan view showing a layer in which a low-potential coil 22 (corresponding to a primary coil of a transformer) is formed in the semiconductor device 5 shown in FIG. 3.

- FIG. 6 is a plan view showing a layer in which a high-potential coil 23 (corresponding to a secondary coil of a transformer) is formed in the semiconductor device 5 shown in FIG. 3.

- FIG. 7 is a cross-sectional view taken along line VIII-VIII shown in FIG. 6.

- FIG. 8 is an enlarged view of region XIII shown in FIG. 7, showing an isolation structure 130.

- the semiconductor device 5 includes a semiconductor chip 41 having a rectangular parallelepiped shape.

- the semiconductor chip 41 includes at least one of silicon, a wide band gap semiconductor, and a compound semiconductor.

- a wide bandgap semiconductor is made of a semiconductor whose bandgap exceeds that of silicon (approximately 1.12 eV).

- the bandgap of a wide bandgap semiconductor is preferably 2.0 eV or more.

- the wide bandgap semiconductor may be SiC (silicon carbide).

- the compound semiconductor may be a III-V compound semiconductor.

- the compound semiconductor may include at least one of AlN (aluminum nitride), InN (indium nitride), GaN (gallium nitride), and GaAs (gallium arsenide).

- the semiconductor chip 41 includes a semiconductor substrate made of silicon.

- the semiconductor chip 41 may be an epitaxial substrate having a layered structure including a semiconductor substrate made of silicon and an epitaxial layer made of silicon.

- the conductivity type of the semiconductor substrate may be n-type or p-type.

- the epitaxial layer may be n-type or p-type.

- the semiconductor chip 41 has a first main surface 42 on one side, a second main surface 43 on the other side, and chip sidewalls 44A-44D connecting the first main surface 42 and the second main surface 43.

- the first main surface 42 and the second main surface 43 are formed in a quadrangular shape (rectangular in this embodiment) when viewed in a plan view from their normal direction Z (hereinafter simply referred to as "plan view").

- the chip sidewalls 44A to 44D include a first chip sidewall 44A, a second chip sidewall 44B, a third chip sidewall 44C, and a fourth chip sidewall 44D.

- the first chip sidewall 44A and the second chip sidewall 44B form the long sides of the semiconductor chip 41.

- the first chip sidewall 44A and the second chip sidewall 44B extend along the first direction X and face the second direction Y.

- the third chip sidewall 44C and the fourth chip sidewall 44D form the short sides of the semiconductor chip 41.

- the third chip sidewall 44C and the fourth chip sidewall 44D extend in the second direction Y and face the first direction X.

- the chip sidewalls 44A to 44D are made of ground surfaces.

- the semiconductor device 5 further includes an insulating layer 51 formed on the first main surface 42 of the semiconductor chip 41.

- the insulating layer 51 has an insulating main surface 52 and insulating side walls 53A-53D.

- the insulating main surface 52 is formed in a quadrangular shape (rectangular in this embodiment) that matches the first main surface 42 in a plan view.

- the insulating main surface 52 extends parallel to the first main surface 42.

- the insulating sidewalls 53A to 53D include a first insulating sidewall 53A, a second insulating sidewall 53B, a third insulating sidewall 53C, and a fourth insulating sidewall 53D.

- the insulating sidewalls 53A to 53D extend from the periphery of the insulating main surface 52 toward the semiconductor chip 41 and are continuous with the chip sidewalls 44A to 44D. Specifically, the insulating sidewalls 53A to 53D are formed flush with the chip sidewalls 44A to 44D.

- the insulating sidewalls 53A to 53D form a ground surface that is flush with the chip sidewalls 44A to 44D.

- the insulating layer 51 is made of a multi-layer insulating laminate structure including a bottom insulating layer 55, a top insulating layer 56, and a plurality of (11 in this embodiment) interlayer insulating layers 57.

- the bottom insulating layer 55 is an insulating layer that directly covers the first main surface 42.

- the top insulating layer 56 is an insulating layer that forms the insulating main surface 52.

- the plurality of interlayer insulating layers 57 are insulating layers interposed between the bottom insulating layer 55 and the top insulating layer 56.

- the bottom insulating layer 55 has a single-layer structure including silicon oxide.

- the top insulating layer 56 has a single-layer structure including silicon oxide.

- the thickness of the bottom insulating layer 55 and the top insulating layer 56 may each be 1 ⁇ m or more and 3 ⁇ m or less (for example, about 2 ⁇ m).

- the multiple interlayer insulating layers 57 each have a stacked structure including a first insulating layer 58 on the bottom insulating layer 55 side and a second insulating layer 59 on the top insulating layer 56 side.

- the first insulating layer 58 may include silicon nitride.

- the first insulating layer 58 is formed as an etching stopper layer for the second insulating layer 59.

- the thickness of the first insulating layer 58 may be 0.1 ⁇ m or more and 1 ⁇ m or less (for example, about 0.3 ⁇ m).

- the second insulating layer 59 is formed on the first insulating layer 58. It contains an insulating material different from that of the first insulating layer 58.

- the second insulating layer 59 may contain silicon oxide.

- the thickness of the second insulating layer 59 may be 1 ⁇ m or more and 3 ⁇ m or less (for example, about 2 ⁇ m). It is preferable that the thickness of the second insulating layer 59 exceeds the thickness of the first insulating layer 58.

- the total thickness DT of the insulating layers 51 may be 5 ⁇ m or more and 50 ⁇ m or less.

- the total thickness DT of the insulating layers 51 and the number of layers of the interlayer insulating layers 57 are arbitrary and are adjusted according to the dielectric strength voltage (dielectric breakdown resistance) to be achieved.

- the insulating materials of the bottom insulating layer 55, the top insulating layer 56 and the interlayer insulating layer 57 are arbitrary and are not limited to a specific insulating material.

- the semiconductor device 5 includes a first functional device 45 formed in an insulating layer 51.

- the first functional device 45 includes one or more (in this embodiment, multiple) transformers 21 (corresponding to the aforementioned transformer).

- the semiconductor device 5 is a multi-channel device including multiple transformers 21.

- the multiple transformers 21 are formed in the inner part of the insulating layer 51 at intervals from the insulating side walls 53A-53D.

- the multiple transformers 21 are formed at intervals in the first direction X.

- the multiple transformers 21 specifically include a first transformer 21A, a second transformer 21B, a third transformer 21C, and a fourth transformer 21D, which are formed in this order from the insulating side wall 53C side to the insulating side wall 53D side in a plan view.

- the multiple transformers 21A to 21D each have a similar structure.

- the structure of the first transformer 21A will be described as an example.

- the structures of the second transformer 21B, third transformer 21C, and fourth transformer 21D will be omitted as the description of the structure of the first transformer 21A applies mutatis mutandis.

- the first transformer 21A includes a low-potential coil 22 and a high-potential coil 23.

- the low-potential coil 22 is formed in an insulating layer 51.

- the high-potential coil 23 is formed in the insulating layer 51 so as to face the low-potential coil 22 in the normal direction Z.

- the low-potential coil 22 and the high-potential coil 23 are formed in a region sandwiched between the bottom insulating layer 55 and the top insulating layer 56 (i.e., multiple interlayer insulating layers 57).

- the low-potential coil 22 is formed on the bottom insulating layer 55 (semiconductor chip 41) side within the insulating layer 51, and the high-potential coil 23 is formed on the top insulating layer 56 (insulating main surface 52) side of the low-potential coil 22 within the insulating layer 51.

- the high-potential coil 23 faces the semiconductor chip 41 with the low-potential coil 22 in between.

- the low-potential coil 22 and the high-potential coil 23 may be positioned at any location. Furthermore, it is sufficient that the high-potential coil 23 faces the low-potential coil 22 with one or more interlayer insulating layers 57 in between.

- the distance between the low potential coil 22 and the high potential coil 23 (i.e., the number of layers of the interlayer insulating layer 57) is adjusted appropriately according to the dielectric strength and electric field strength between the low potential coil 22 and the high potential coil 23.

- the low potential coil 22 is formed in the third interlayer insulating layer 57 counting from the bottom insulating layer 55 side.

- the high potential coil 23 is formed in the first interlayer insulating layer 57 counting from the top insulating layer 56 side.

- the low-potential coil 22 is embedded in the interlayer insulating layer 57, penetrating the first insulating layer 58 and the second insulating layer 59.

- the low-potential coil 22 includes a first inner end 24, a first outer end 25, and a first spiral portion 26 wound in a spiral shape between the first inner end 24 and the first outer end 25.

- the first spiral portion 26 is wound in a spiral shape that extends in an elliptical shape (oval shape) in a plan view.

- the portion that forms the innermost periphery of the first spiral portion 26 defines a first inner region 66 that is elliptical in a plan view.

- the number of turns of the first spiral portion 26 may be 5 or more and 30 or less.

- the width of the first spiral portion 26 may be 0.1 ⁇ m or more and 5 ⁇ m or less.

- the width of the first spiral portion 26 is preferably 1 ⁇ m or more and 3 ⁇ m or less.

- the width of the first spiral portion 26 is defined by the width in a direction perpendicular to the spiral direction.

- the first winding pitch of the first spiral portion 26 may be 0.1 ⁇ m or more and 5 ⁇ m or less.

- the first winding pitch is preferably 1 ⁇ m or more and 3 ⁇ m or less.

- the first winding pitch is defined by the distance between two adjacent portions of the first spiral portion 26 in a direction perpendicular to the spiral direction.

- the winding shape of the first spiral portion 26 and the planar shape of the first inner region 66 are arbitrary and are not limited to the form shown in FIG. 5, etc.

- the first spiral portion 26 may be wound in a polygonal shape, such as a triangular shape or a rectangular shape, or in a circular shape in a planar view.

- the first inner region 66 may be partitioned into a polygonal shape, such as a triangular shape or a rectangular shape, or in a circular shape in a planar view, depending on the winding shape of the first spiral portion 26.

- the low potential coil 22 may include at least one of titanium, titanium nitride, copper, aluminum, and tungsten.

- the low potential coil 22 may have a laminated structure including a barrier layer and a main body layer.

- the barrier layer defines a recess space in the interlayer insulating layer 57.

- the barrier layer may include at least one of titanium and titanium nitride.

- the main body layer may include at least one of copper, aluminum, and tungsten.

- the high-potential coil 23 is embedded in the interlayer insulating layer 57, penetrating the first insulating layer 58 and the second insulating layer 59.

- the high-potential coil 23 includes a second inner end 27, a second outer end 28, and a second spiral portion 29 wound in a spiral shape between the second inner end 27 and the second outer end 28.

- the second spiral portion 29 is wound in a spiral shape extending in an elliptical shape (oval shape) in a planar view.

- the portion forming the innermost periphery of the second spiral portion 29 defines a second inner region 67 that is elliptical in a planar view.

- the second inner region 67 of the second spiral portion 29 faces the first inner region 66 of the first spiral portion 26 in the normal direction Z.

- the number of turns of the second spiral portion 29 may be 5 or more and 30 or less.

- the number of turns of the second spiral portion 29 relative to the number of turns of the first spiral portion 26 is adjusted according to the voltage value to be boosted. It is preferable that the number of turns of the second spiral portion 29 exceeds the number of turns of the first spiral portion 26.

- the number of turns of the second spiral portion 29 may be less than the number of turns of the first spiral portion 26, or may be equal to the number of turns of the first spiral portion 26.

- the width of the second spiral portion 29 may be 0.1 ⁇ m or more and 5 ⁇ m or less.

- the width of the second spiral portion 29 is preferably 1 ⁇ m or more and 3 ⁇ m or less.

- the width of the second spiral portion 29 is defined by the width in a direction perpendicular to the spiral direction.

- the width of the second spiral portion 29 is preferably equal to the width of the first spiral portion 26.

- the second winding pitch of the second spiral portion 29 may be 0.1 ⁇ m or more and 5 ⁇ m or less.

- the second winding pitch is preferably 1 ⁇ m or more and 3 ⁇ m or less.

- the second winding pitch is defined by the distance between two adjacent portions of the second spiral portion 29 in a direction perpendicular to the spiral direction.

- the second winding pitch is preferably equal to the first winding pitch of the first spiral portion 26.

- the winding shape of the second spiral portion 29 and the planar shape of the second inner region 67 are arbitrary and are not limited to the form shown in FIG. 6, etc.

- the second spiral portion 29 may be wound in a polygonal shape, such as a triangular shape or a rectangular shape, or in a circular shape in a planar view.

- the second inner region 67 may be partitioned into a polygonal shape, such as a triangular shape or a rectangular shape, or in a circular shape in a planar view, depending on the winding shape of the second spiral portion 29.

- the high-potential coil 23 is preferably formed from the same conductive material as the low-potential coil 22.

- the high-potential coil 23 preferably includes a barrier layer and a main body layer, similar to the low-potential coil 22.

- the semiconductor device 5 includes a plurality (12 in this figure) of low potential terminals 11 and a plurality (12 in this figure) of high potential terminals 12.

- the plurality of low potential terminals 11 are each electrically connected to the low potential coils 22 of the corresponding transformers 21A to 21D.

- the plurality of high potential terminals 12 are each electrically connected to the high potential coils 23 of the corresponding transformers 21A to 21D.

- the low-potential terminals 11 are formed on the insulating main surface 52 of the insulating layer 51. Specifically, the low-potential terminals 11 are formed in an area on the insulating sidewall 53B side at intervals in the second direction Y from the transformers 21A-21D, and are arranged at intervals in the first direction X.

- the low potential terminals 11 include a first low potential terminal 11A, a second low potential terminal 11B, a third low potential terminal 11C, a fourth low potential terminal 11D, a fifth low potential terminal 11E, and a sixth low potential terminal 11F.

- two of each of the low potential terminals 11A to 11F are formed.

- the number of low potential terminals 11A to 11F is arbitrary.

- the first low potential terminal 11A faces the first transformer 21A in the second direction Y in a plan view.

- the second low potential terminal 11B faces the second transformer 21B in the second direction Y in a plan view.

- the third low potential terminal 11C faces the third transformer 21C in the second direction Y in a plan view.

- the fourth low potential terminal 11D faces the fourth transformer 21D in the second direction Y in a plan view.

- the fifth low potential terminal 11E is formed in the area between the first low potential terminal 11A and the second low potential terminal 11B in a plan view.

- the sixth low potential terminal 11F is formed in the area between the third low potential terminal 11C and the fourth low potential terminal 11D in a plan view.

- the first low potential terminal 11A is electrically connected to the first inner end 24 of the first transformer 21A (low potential coil 22).

- the second low potential terminal 11B is electrically connected to the first inner end 24 of the second transformer 21B (low potential coil 22).

- the third low potential terminal 11C is electrically connected to the first inner end 24 of the third transformer 21C (low potential coil 22).

- the fourth low potential terminal 11D is electrically connected to the first inner end 24 of the fourth transformer 21D (low potential coil 22).

- the fifth low potential terminal 11E is electrically connected to the first outer end 25 of the first transformer 21A (low potential coil 22) and the first outer end 25 of the second transformer 21B (low potential coil 22).

- the sixth low potential terminal 11F is electrically connected to the first outer end 25 of the third transformer 21C (low potential coil 22) and the first outer end 25 of the fourth transformer 21D (low potential coil 22).

- the multiple high potential terminals 12 are formed on the insulating main surface 52 of the insulating layer 51 at intervals from the multiple low potential terminals 11. Specifically, the multiple high potential terminals 12 are formed in the area on the insulating side wall 53A side at intervals from the multiple low potential terminals 11 in the second direction Y, and are arranged at intervals in the first direction X.

- the multiple high potential terminals 12 are each formed in an area close to the corresponding transformer 21A-21D in a planar view.

- the high potential terminals 12 being close to the transformers 21A-21D means that the distance between the high potential terminal 12 and the transformer 21 in a planar view is less than the distance between the low potential terminal 11 and the high potential terminal 12.

- the multiple high potential terminals 12 are formed at intervals along the first direction X so as to face the multiple transformers 21A to 21D along the first direction X in a plan view. More specifically, the multiple high potential terminals 12 are formed at intervals along the first direction X so as to be located in the second inner region 67 of the high potential coil 23 and in the region between adjacent high potential coils 23 in a plan view. As a result, the multiple high potential terminals 12 are arranged in a row with the multiple transformers 21A to 21D in the first direction X in a plan view.

- the multiple high potential terminals 12 include a first high potential terminal 12A, a second high potential terminal 12B, a third high potential terminal 12C, a fourth high potential terminal 12D, a fifth high potential terminal 12E, and a sixth high potential terminal 12F.

- a first high potential terminal 12A a second high potential terminal 12B

- a third high potential terminal 12C a third high potential terminal 12C

- a fourth high potential terminal 12D a fifth high potential terminal 12E

- a sixth high potential terminal 12F a sixth high potential terminal 12F.

- two of each of the multiple high potential terminals 12A to 12F are formed.

- the number of multiple high potential terminals 12A to 12F is arbitrary.

- the first high potential terminal 12A is formed in the second inner region 67 of the first transformer 21A (high potential coil 23) in a plan view.

- the second high potential terminal 12B is formed in the second inner region 67 of the second transformer 21B (high potential coil 23) in a plan view.

- the third high potential terminal 12C is formed in the second inner region 67 of the third transformer 21C (high potential coil 23) in a plan view.

- the fourth high potential terminal 12D is formed in the second inner region 67 of the fourth transformer 21D (high potential coil 23) in a plan view.

- the fifth high potential terminal 12E is formed in the region between the first transformer 21A and the second transformer 21B in a plan view.

- the sixth high potential terminal 12F is formed in the region between the third transformer 21C and the fourth transformer 21D in a plan view.

- the first high potential terminal 12A is electrically connected to the second inner end 27 of the first transformer 21A (high potential coil 23).

- the second high potential terminal 12B is electrically connected to the second inner end 27 of the second transformer 21B (high potential coil 23).

- the third high potential terminal 12C is electrically connected to the second inner end 27 of the third transformer 21C (high potential coil 23).

- the fourth high potential terminal 12D is electrically connected to the second inner end 27 of the fourth transformer 21D (high potential coil 23).

- the fifth high potential terminal 12E is electrically connected to the second outer end 28 of the first transformer 21A (high potential coil 23) and the second outer end 28 of the second transformer 21B (high potential coil 23).

- the sixth high potential terminal 12F is electrically connected to the second outer end 28 of the third transformer 21C (high potential coil 23) and the second outer end 28 of the fourth transformer 21D (high potential coil 23).

- the semiconductor device 5 includes a first low potential wiring 31, a second low potential wiring 32, a first high potential wiring 33, and a second high potential wiring 34, each formed in an insulating layer 51.

- a plurality of first low potential wirings 31, a plurality of second low potential wirings 32, a plurality of first high potential wirings 33, and a plurality of second high potential wirings 34 are formed.

- the first low-potential wiring 31 and the second low-potential wiring 32 fix the low-potential coil 22 of the first transformer 21A and the low-potential coil 22 of the second transformer 21B to the same potential.

- the first low-potential wiring 31 and the second low-potential wiring 32 also fix the low-potential coil 22 of the third transformer 21C and the low-potential coil 22 of the fourth transformer 21D to the same potential.

- the first low-potential wiring 31 and the second low-potential wiring 32 fix all the low-potential coils 22 of the transformers 21A to 21D to the same potential.

- the first high-potential wiring 33 and the second high-potential wiring 34 fix the high-potential coil 23 of the first transformer 21A and the high-potential coil 23 of the second transformer 21B to the same potential.

- the first high-potential wiring 33 and the second high-potential wiring 34 also fix the high-potential coil 23 of the third transformer 21C and the high-potential coil 23 of the fourth transformer 21D to the same potential.

- the first high-potential wiring 33 and the second high-potential wiring 34 fix all the high-potential coils 23 of the transformers 21A to 21D to the same potential.

- the multiple first low potential wirings 31 are electrically connected to the corresponding low potential terminals 11A to 11D and the first inner ends 24 of the corresponding transformers 21A to 21D (low potential coils 22).

- the multiple first low potential wirings 31 have the same structure.

- the structure of the first low potential wiring 31 connected to the first low potential terminal 11A and the first transformer 21A will be described as an example.

- the structure of the other first low potential wirings 31 will be omitted, as the description of the structure of the first low potential wiring 31 connected to the first transformer 21A applies mutatis mutandis.

- the first low-potential wiring 31 includes a through wiring 71, a low-potential connection wiring 72, a lead-out wiring 73, a first connection plug electrode 74, a second connection plug electrode 75, one or more (in this embodiment, multiple) pad plug electrodes 76, and one or more (in this embodiment, multiple) substrate plug electrodes 77.

- the through wiring 71, the low-potential connection wiring 72, the draw-out wiring 73, the first connection plug electrode 74, the second connection plug electrode 75, the pad plug electrode 76, and the substrate plug electrode 77 are preferably each formed from the same conductive material as the low-potential coil 22, etc.

- the through wiring 71, the low-potential connection wiring 72, the draw-out wiring 73, the first connection plug electrode 74, the second connection plug electrode 75, the pad plug electrode 76, and the substrate plug electrode 77 preferably each include a barrier layer and a main body layer, similar to the low-potential coil 22, etc.

- the through wiring 71 penetrates the multiple interlayer insulating layers 57 in the insulating layer 51 and extends in a columnar shape extending along the normal direction Z.

- the through wiring 71 is formed in the region between the bottom insulating layer 55 and the top insulating layer 56 in the insulating layer 51.

- the through wiring 71 has an upper end on the top insulating layer 56 side and a lower end on the bottom insulating layer 55 side.

- the upper end of the through wiring 71 is formed in the same interlayer insulating layer 57 as the high potential coil 23 and is covered by the top insulating layer 56.

- the lower end of the through wiring 71 is formed in the same interlayer insulating layer 57 as the low potential coil 22.

- the through wiring 71 includes a first electrode layer 78, a second electrode layer 79, and a plurality of wiring plug electrodes 80.

- the first electrode layer 78, the second electrode layer 79, and the wiring plug electrodes 80 are each formed from the same conductive material as the low potential coil 22, etc.

- the first electrode layer 78, the second electrode layer 79, and the wiring plug electrodes 80 each include a barrier layer and a main body layer, similar to the low potential coil 22, etc.

- the first electrode layer 78 forms the upper end of the through wiring 71.

- the second electrode layer 79 forms the lower end of the through wiring 71.

- the first electrode layer 78 is formed in an island shape and faces the low potential terminal 11 (first low potential terminal 11A) in the normal direction Z.

- the second electrode layer 79 is formed in an island shape and faces the first electrode layer 78 in the normal direction Z.

- the multiple wiring plug electrodes 80 are embedded in multiple interlayer insulating layers 57 located in the region between the first electrode layer 78 and the second electrode layer 79.

- the multiple wiring plug electrodes 80 are stacked from the bottom insulating layer 55 toward the top insulating layer 56 so as to be electrically connected to each other, and electrically connect the first electrode layer 78 and the second electrode layer 79.

- the multiple wiring plug electrodes 80 each have a planar area less than the planar area of the first electrode layer 78 and the planar area of the second electrode layer 79.

- the number of layers of the multiple wiring plug electrodes 80 matches the number of layers of the multiple interlayer insulating layers 57. In this embodiment, six wiring plug electrodes 80 are embedded in each interlayer insulating layer 57, but the number of wiring plug electrodes 80 embedded in each interlayer insulating layer 57 is arbitrary. Of course, one or more wiring plug electrodes 80 may be formed penetrating the multiple interlayer insulating layers 57.

- the low-potential connection wiring 72 is formed in the first inner region 66 of the first transformer 21A (low-potential coil 22) in the same interlayer insulating layer 57 as the low-potential coil 22.

- the low-potential connection wiring 72 is formed in an island shape and faces the high-potential terminal 12 (first high-potential terminal 12A) in the normal direction Z. It is preferable that the low-potential connection wiring 72 has a planar area that exceeds the planar area of the wiring plug electrode 80.

- the low-potential connection wiring 72 is electrically connected to the first inner end 24 of the low-potential coil 22.

- the draw-out wiring 73 is formed in the interlayer insulating layer 57 in the region between the semiconductor chip 41 and the through wiring 71.

- the draw-out wiring 73 is formed in the first interlayer insulating layer 57 counting from the bottom insulating layer 55.

- the draw-out wiring 73 includes a first end on one side, a second end on the other side, and a wiring portion connecting the first end and the second end.

- the first end of the draw-out wiring 73 is located in the region between the semiconductor chip 41 and the lower end of the through wiring 71.

- the second end of the draw-out wiring 73 is located in the region between the semiconductor chip 41 and the low-potential connection wiring 72.

- the wiring portion extends along the first main surface 42 of the semiconductor chip 41 and extends in a band shape in the region between the first end and the second end.

- the first connection plug electrode 74 is formed in the interlayer insulating layer 57 in the region between the through wiring 71 and the draw-out wiring 73, and is electrically connected to first ends of the through wiring 71 and the draw-out wiring 73.

- the second connection plug electrode 75 is formed in the interlayer insulating layer 57 in the region between the low-potential connection wiring 72 and the draw-out wiring 73, and is electrically connected to second ends of the low-potential connection wiring 72 and the draw-out wiring 73.

- the multiple pad plug electrodes 76 are formed in the uppermost insulating layer 56 in a region between the low potential terminal 11 (first low potential terminal 11A) and the through wiring 71, and are electrically connected to the upper ends of the low potential terminal 11 and the through wiring 71, respectively.

- the multiple substrate plug electrodes 77 are formed in the lowermost insulating layer 55 in a region between the semiconductor chip 41 and the draw-out wiring 73. In this embodiment, the substrate plug electrodes 77 are formed in a region between the semiconductor chip 41 and the first ends of the draw-out wiring 73, and are electrically connected to the semiconductor chip 41 and the first ends of the draw-out wiring 73, respectively.

- the multiple first high potential wirings 33 are electrically connected to the corresponding high potential terminals 12A-12D and the second inner ends 27 of the corresponding transformers 21A-21D (high potential coils 23).

- the multiple first high potential wirings 33 each have a similar structure.

- the structure of the first high potential wiring 33 connected to the first high potential terminal 12A and the first transformer 21A will be described as an example.

- the structure of the other first high potential wirings 33 will be omitted, as the description of the structure of the first high potential wiring 33 connected to the first transformer 21A applies mutatis mutandis.

- the first high-potential wiring 33 includes a high-potential connection wiring 81 and one or more (in this embodiment, multiple) pad plug electrodes 82.

- the high-potential connection wiring 81 and the pad plug electrode 82 are preferably formed from the same conductive material as the low-potential coil 22, etc.

- the high-potential connection wiring 81 and the pad plug electrode 82 preferably include a barrier layer and a main body layer, similar to the low-potential coil 22, etc.

- the high-potential connection wiring 81 is formed in the second inner region 67 of the high-potential coil 23 in the same interlayer insulating layer 57 as the high-potential coil 23.

- the high-potential connection wiring 81 is formed in an island shape and faces the high-potential terminal 12 (first high-potential terminal 12A) in the normal direction Z.

- the high-potential connection wiring 81 is electrically connected to the second inner end 27 of the high-potential coil 23.

- the high-potential connection wiring 81 is formed at a distance from the low-potential connection wiring 72 in a plan view and does not face the low-potential connection wiring 72 in the normal direction Z. This increases the insulation distance between the low-potential connection wiring 72 and the high-potential connection wiring 81, and increases the dielectric strength of the insulating layer 51.

- the multiple pad plug electrodes 82 are formed in the uppermost insulating layer 56 in a region between the high potential terminal 12 (first high potential terminal 12A) and the high potential connection wiring 81, and are electrically connected to the high potential terminal 12 and the high potential connection wiring 81, respectively.

- the multiple pad plug electrodes 82 each have a planar area less than the planar area of the high potential connection wiring 81 in a plan view.

- the distance D1 between the low potential terminal 11 and the high potential terminal 12 is preferably greater than the distance D2 between the low potential coil 22 and the high potential coil 23 (D2 ⁇ D1).

- the distance D1 is preferably greater than the total thickness DT of the multiple interlayer insulating layers 57 (DT ⁇ D1).

- the ratio D2/D1 of the distance D2 to the distance D1 may be 0.01 or more and 0.1 or less.

- the distance D1 is preferably 100 ⁇ m or more and 500 ⁇ m or less.

- the distance D2 may be 1 ⁇ m or more and 50 ⁇ m or less.

- the distance D2 is preferably 5 ⁇ m or more and 25 ⁇ m or less.

- the values of the distance D1 and the distance D2 are arbitrary and are adjusted appropriately according to the dielectric strength voltage to be realized.

- the semiconductor device 5 includes a dummy pattern 85 embedded in the insulating layer 51 so as to be positioned around the transformers 21A to 21D in a plan view.

- the dummy pattern 85 is formed in a pattern (discontinuous pattern) different from the high potential coil 23 and the low potential coil 22, and is independent of the transformers 21A to 21D. In other words, the dummy pattern 85 does not function as a transformer 21A to 21D.

- the dummy pattern 85 is formed as a shield conductor layer that shields the electric field between the low potential coil 22 and the high potential coil 23 in the transformers 21A to 21D and suppresses electric field concentration on the high potential coil 23.

- the dummy pattern 85 is routed with a line density equal to the line density of the high potential coil 23 per unit area.

- the line density of the dummy pattern 85 being equal to the line density of the high potential coil 23 means that the line density of the dummy pattern 85 falls within a range of ⁇ 20% of the line density of the high potential coil 23.

- the depth position of the dummy pattern 85 inside the insulating layer 51 is arbitrary and is adjusted according to the electric field strength to be relaxed.

- the dummy pattern 85 is preferably formed in a region closer to the high potential coil 23 than to the low potential coil 22 in the normal direction Z. Note that the dummy pattern 85 being closer to the high potential coil 23 in the normal direction Z means that the distance between the dummy pattern 85 and the high potential coil 23 in the normal direction Z is less than the distance between the dummy pattern 85 and the low potential coil 22.

- the dummy pattern 85 is preferably formed in the same interlayer insulating layer 57 as the high-potential coil 23. In this case, electric field concentration on the high-potential coil 23 can be further appropriately suppressed.

- the dummy pattern 85 includes multiple dummy patterns with different electrical states.

- the dummy pattern 85 may include a high-potential dummy pattern.

- the depth position of the high-potential dummy pattern 86 inside the insulating layer 51 is arbitrary and is adjusted according to the electric field strength to be relaxed.

- the high-potential dummy pattern 86 is preferably formed in a region closer to the high-potential coil 23 than the low-potential coil 22 in the normal direction Z.

- the high-potential dummy pattern 86 being closer to the high-potential coil 23 in the normal direction Z means that the distance between the high-potential dummy pattern 86 and the high-potential coil 23 in the normal direction Z is less than the distance between the high-potential dummy pattern 86 and the low-potential coil 22.

- the dummy pattern 85 includes a floating dummy pattern formed in an electrically floating state within the insulating layer 51 so as to be positioned around the transformers 21A to 21D.

- the floating dummy pattern is routed in dense lines so as to partially cover and partially expose the area around the high-potential coil 23 in a plan view.

- the floating dummy pattern may be formed with ends or without ends.

- the depth position of the floating dummy pattern inside the insulating layer 51 is arbitrary and is adjusted according to the electric field strength to be mitigated.

- the number of floating lines is arbitrary and is adjusted according to the electric field to be mitigated.

- the floating dummy pattern may be composed of multiple floating lines.

- the semiconductor device 5 includes a second functional device 60 formed on the first main surface 42 of the semiconductor chip 41 in a device region 62.

- the second functional device 60 is formed using a surface portion of the first main surface 42 of the semiconductor chip 41 and/or a region above the first main surface 42 of the semiconductor chip 41, and is covered by an insulating layer 51 (lowest insulating layer 55).

- the second functional device 60 is shown in a simplified form by a dashed line drawn on the surface portion of the first main surface 42.

- the second functional device 60 is electrically connected to the low potential terminal 11 via a low potential wiring, and is electrically connected to the high potential terminal 12 via a high potential wiring.

- the low potential wiring has a structure similar to that of the first low potential wiring 31 (second low potential wiring 32), except that it is routed within the insulating layer 51 so as to be connected to the second functional device 60.

- the high potential wiring has a structure similar to that of the first high potential wiring 33 (second high potential wiring 34), except that it is routed within the insulating layer 51 so as to be connected to the second functional device 60.

- a specific description of the low potential wiring and high potential wiring related to the second functional device 60 will be omitted.

- the second functional device 60 may include at least one of a passive device, a semiconductor rectifier device, and a semiconductor switching device.

- the second functional device 60 may include a circuit network in which any two or more types of devices selected from the passive device, the semiconductor rectifier device, and the semiconductor switching device are selectively combined.

- the circuit network may form part or all of an integrated circuit.

- the passive device may include a semiconductor passive device.

- the passive device may include either or both of a resistor and a capacitor.

- the semiconductor rectifier device may include at least one of a pn junction diode, a PIN diode, a Zener diode, a Schottky barrier diode, and a fast recovery diode.

- the semiconductor switching device may include at least one of a BJT [Bipolar Junction Transistor], a MISFET [Metal Insulator Semiconductor Field Effect Transistor], an IGBT [Insulated Gate Bipolar Junction Transistor], and a JFET [Junction Field Effect Transistor].

- the semiconductor device 5 further includes a seal conductor 61 embedded in the insulating layer 51.

- the seal conductor 61 is embedded in the insulating layer 51 in a wall shape at a distance from the insulating side walls 53A to 53D in a plan view, and divides the insulating layer 51 into a device region 62 and an outer region 63.

- the seal conductor 61 prevents moisture and cracks from entering the device region 62 from the outer region 63.

- the device region 62 is an area including the first functional device 45 (multiple transformers 21), the second functional device 60, multiple low potential terminals 11, multiple high potential terminals 12, the first low potential wiring 31, the second low potential wiring 32, the first high potential wiring 33, the second high potential wiring 34, and the dummy pattern 85.

- the outer region 63 is an area outside the device region 62.

- the seal conductor 61 is electrically isolated from the device region 62. Specifically, the seal conductor 61 is electrically isolated from the first functional device 45 (multiple transformers 21), the second functional device 60, the multiple low potential terminals 11, the multiple high potential terminals 12, the first low potential wiring 31, the second low potential wiring 32, the first high potential wiring 33, the second high potential wiring 34, and the dummy pattern 85. More specifically, the seal conductor 61 is fixed in an electrically floating state. The seal conductor 61 does not form a current path leading to the device region 62.

- the seal conductor 61 is formed in a band shape along the insulating side walls 53 to 53D in a plan view.

- the seal conductor 61 is formed in a square ring shape (specifically, a rectangular ring shape) in a plan view.

- the seal conductor 61 defines a square-shaped (specifically, rectangular) device region 62 in a plan view.

- the seal conductor 61 also defines a square-shaped (specifically, rectangular) outer region 63 that surrounds the device region 62 in a plan view.

- the seal conductor 61 has an upper end on the insulating principal surface 52 side, a lower end on the semiconductor chip 41 side, and a wall extending in a wall shape between the upper end and the lower end.

- the upper end of the seal conductor 61 is formed at a distance from the insulating principal surface 52 to the semiconductor chip 41 side, and is located within the insulating layer 51.

- the upper end of the seal conductor 61 is covered by the uppermost insulating layer 56.

- the upper end of the seal conductor 61 may be covered by one or more interlayer insulating layers 57.

- the upper end of the seal conductor 61 may be exposed from the uppermost insulating layer 56.

- the lower end of the seal conductor 61 is formed at a distance from the semiconductor chip 41 toward the upper end side.

- the seal conductor 61 is embedded in the insulating layer 51 so as to be located on the semiconductor chip 41 side relative to the multiple low potential terminals 11 and multiple high potential terminals 12. Furthermore, the seal conductor 61 faces the first functional device 45 (multiple transformers 21), the first low potential wiring 31, the second low potential wiring 32, the first high potential wiring 33, the second high potential wiring 34, and the dummy pattern 85 in the insulating layer 51 in a direction parallel to the insulating principal surface 52.

- the seal conductor 61 may face a part of the second functional device 60 in the insulating layer 51 in a direction parallel to the insulating principal surface 52.

- the seal conductor 61 includes a plurality of seal plug conductors 64 and one or more (in this embodiment, multiple) seal via conductors 65.

- the number of seal via conductors 65 is arbitrary.

- the uppermost seal plug conductor 64 among the plurality of seal plug conductors 64 forms the upper end of the seal conductor 61.

- the plurality of seal via conductors 65 each form the lower end of the seal conductor 61.

- the seal plug conductor 64 and the seal via conductor 65 are preferably formed from the same conductive material as the low potential coil 22. In other words, the seal plug conductor 64 and the seal via conductor 65 preferably include a barrier layer and a main body layer, similar to the low potential coil 22, etc.

- the multiple seal plug conductors 64 are embedded in the multiple interlayer insulating layers 57, and are each formed in a square ring shape (specifically, a rectangular ring shape) surrounding the device region 62 in a planar view.

- the multiple seal plug conductors 64 are stacked from the bottom insulating layer 55 to the top insulating layer 56 so as to be connected to each other.

- the number of stacked layers of the multiple seal plug conductors 64 matches the number of stacked layers of the multiple interlayer insulating layers 57.

- one or more seal plug conductors 64 may be formed penetrating the multiple interlayer insulating layers 57.

- a single annular seal conductor 61 is formed by an assembly of multiple seal plug conductors 64, it is not necessary for all of the multiple seal plug conductors 64 to be formed in an annular shape.

- at least one of the multiple seal plug conductors 64 may be formed with ends.

- at least one of the multiple seal plug conductors 64 may be divided into multiple strip-shaped portions with ends.

- the multiple seal plug conductors 64 are formed in an endless (annular) shape.

- the multiple seal via conductors 65 are each formed in the area between the semiconductor chip 41 and the seal plug conductor 64 in the bottom insulating layer 55.

- the multiple seal via conductors 65 are formed at a distance from the semiconductor chip 41 and are connected to the seal plug conductor 64.

- the multiple seal via conductors 65 have a planar area less than the planar area of the seal plug conductor 64.

- the single seal via conductor 65 may have a planar area equal to or greater than the planar area of the seal plug conductor 64.

- the width of the sealing conductor 61 may be 0.1 ⁇ m or more and 10 ⁇ m or less.

- the width of the sealing conductor 61 is preferably 1 ⁇ m or more and 5 ⁇ m or less.

- the width of the sealing conductor 61 is defined by the width in a direction perpendicular to the direction in which the sealing conductor 61 extends.

- the semiconductor device 5 further includes an isolation structure 130 that is interposed between the semiconductor chip 41 and the seal conductor 61 and electrically isolates the seal conductor 61 from the semiconductor chip 41.

- the isolation structure 130 preferably includes an insulator.

- the isolation structure 130 is made of a field insulating film 131 formed on the first main surface 42 of the semiconductor chip 41.

- the field insulating film 131 includes at least one of an oxide film (silicon oxide film) and a nitride film (silicon nitride film).

- the field insulating film 131 is preferably made of a LOCOS (local oxidation of silicon) film, which is an example of an oxide film formed by oxidizing the first main surface 42 of the semiconductor chip 41.

- the thickness of the field insulating film 131 is arbitrary as long as it can insulate the semiconductor chip 41 and the seal conductor 61.

- the thickness of the field insulating film 131 may be 0.1 ⁇ m or more and 5 ⁇ m or less.

- the isolation structure 130 is formed on the first main surface 42 of the semiconductor chip 41, and extends in a band shape along the seal conductor 61 in a planar view.

- the isolation structure 130 is formed in a square ring shape (specifically, a rectangular ring shape) in a planar view.

- the isolation structure 130 has a connection portion 132 to which the lower end portion (seal via conductor 65) of the seal conductor 61 is connected.

- the connection portion 132 may form an anchor portion in which the lower end portion (seal via conductor 65) of the seal conductor 61 is embedded toward the semiconductor chip 41.

- the connection portion 132 may be formed flush with the main surface of the isolation structure 130.

- the separation structure 130 includes an inner end 130A on the device region 62 side, an outer end 130B on the outer region 63 side, and a main body 130C between the inner end 130A and the outer end 130B.

- the inner end 130A defines the region in which the second functional device 60 is formed (i.e., the device region 62) in a plan view.

- the inner end 130A may be formed integrally with an insulating film (not shown) formed on the first main surface 42 of the semiconductor chip 41.

- the outer end 130B is exposed from the chip sidewalls 44A to 44D of the semiconductor chip 41 and is continuous with the chip sidewalls 44A to 44D of the semiconductor chip 41. More specifically, the outer end 130B is formed flush with the chip sidewalls 44A to 44D of the semiconductor chip 41. The outer end 130B forms a flush ground surface between the chip sidewalls 44A to 44D of the semiconductor chip 41 and the insulating sidewalls 53A to 53D of the insulating layer 51. Of course, in other embodiments, the outer end 130B may be formed in the first main surface 42 at a distance from the chip sidewalls 44A to 44D.

- the main body 130C has a flat surface that extends approximately parallel to the first main surface 42 of the semiconductor chip 41.

- the main body 130C has a connection portion 132 to which the lower end portion (seal via conductor 65) of the seal conductor 61 is connected.

- the connection portion 132 is formed in a portion of the main body 130C that is spaced apart from the inner end portion 130A and the outer end portion 130B.

- the isolation structure 130 can take various forms in addition to the field insulating film 131.

- the semiconductor device 5 further includes an inorganic insulating layer 140 formed on the insulating principal surface 52 of the insulating layer 51 so as to cover the seal conductor 61.

- the inorganic insulating layer 140 may be referred to as a passivation layer.

- the inorganic insulating layer 140 protects the insulating layer 51 and the semiconductor chip 41 from above the insulating principal surface 52.

- the inorganic insulating layer 140 has a laminated structure including a first inorganic insulating layer 141 and a second inorganic insulating layer 142.

- the first inorganic insulating layer 141 may include silicon oxide.

- the first inorganic insulating layer 141 preferably includes USG (undoped silicate glass), which is silicon oxide without added impurities.

- the thickness of the first inorganic insulating layer 141 may be 50 nm or more and 5000 nm or less.

- the second inorganic insulating layer 142 may include silicon nitride.

- the thickness of the second inorganic insulating layer 142 may be 500 nm or more and 5000 nm or less.

- the breakdown voltage (V/cm) of the USG exceeds the breakdown voltage (V/cm) of silicon nitride. Therefore, when thickening the inorganic insulating layer 140, it is preferable to form the first inorganic insulating layer 141 thicker than the second inorganic insulating layer 142.

- the first inorganic insulating layer 141 may contain at least one of BPSG (boron doped phosphor silicate glass) and PSG (phosphorus silicate glass), which are examples of silicon oxide. However, in this case, since impurities (boron or phosphorus) are contained in the silicon oxide, it is particularly preferable to form the first inorganic insulating layer 141 made of USG in order to increase the dielectric strength on the high-potential coil 23.

- the inorganic insulating layer 140 may have a single-layer structure made of either the first inorganic insulating layer 141 or the second inorganic insulating layer 142.

- the inorganic insulating layer 140 covers the entire area of the sealing conductor 61, and has a plurality of low potential pad openings 143 and a plurality of high potential pad openings 144 formed in the area outside the sealing conductor 61.

- the plurality of low potential pad openings 143 expose the plurality of low potential terminals 11, respectively.