EP0376437A2 - Flüssigkristallanzeige mit aktiver Matrix - Google Patents

Flüssigkristallanzeige mit aktiver Matrix Download PDFInfo

- Publication number

- EP0376437A2 EP0376437A2 EP89308162A EP89308162A EP0376437A2 EP 0376437 A2 EP0376437 A2 EP 0376437A2 EP 89308162 A EP89308162 A EP 89308162A EP 89308162 A EP89308162 A EP 89308162A EP 0376437 A2 EP0376437 A2 EP 0376437A2

- Authority

- EP

- European Patent Office

- Prior art keywords

- electrode

- picture element

- insulating layer

- capacitor

- gate

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/136—Liquid crystal cells structurally associated with a semi-conducting layer or substrate, e.g. cells forming part of an integrated circuit

- G02F1/1362—Active matrix addressed cells

- G02F1/136213—Storage capacitors associated with the pixel electrode

Definitions

- This invention relates to an active matrix type liquid crystal display device in which thin film transistors are used as non-linear switching elements, and more particularly to an active matrix type liquid crystal display device in which additional capacitors are formed.

- TFTs thin film transistors

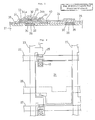

- FIG. 3 shows a substrate of a conventional active matrix type liquid crystal display device.

- TFTs and additional capacitors are formed on the substrate.

- a plurality of gate bus lines 2 are formed in parallel and horizontally in Fig. 3, and a plurality of source bus lines 3 are formed vertically in the figure on an insulating substrate 7 (Fig. 4).

- a TFT 5 is formed in the vicinity of each intersection of the gate bus lines 2 and source bus lines 3.

- Each TFT 5 drives a picture element electrode 4 which is disposed in each region surrounded by two adjacent gate bus lines 2 and source bus lines 3.

- Under the picture element electrode 4, a capacitor electrode 6 is formed.

- a liquid crystal material is sealed to construct a display device.

- Each picture element electrode 4 constitutes a picture element.

- Fig. 4 is a sectional view taken along line IV-IV of Fig. 3.

- the gate electrode 8 of the TFT 5 and the capacitor electrode 6 are formed on the surface of the insulating substrate 7.

- the gate electrode 8 is one part of the gate bus line 2.

- the gate electrode 8 and capacitor electrode 6 can be formed simultaneously, and made of the same material.

- An anodic oxidation film 9 is formed on each of the gate electrodes 8 and capacitor electrode 6.

- a gate insulating layer 10 is formed on the anodic oxidation films 9 and the remaining surface of the insulating substrate 7.

- the TFT 5 further comprises an i-amorphous silicon (a-Si) film 11, an insulating film 12, n+-a-Si films 13, a source electrode 14a, and a drain electrode 14b which are laminated on the gate insulating layer 10.

- the source electrode 14a and drain electrode 14b are made of the same material as that of the source bus lines 3, and formed simultaneously with the source bus lines 3.

- the picture element electrode 4 is formed on the gate insulating layer 10, and electrically connected to the drain electrode 14b.

- a dielectric layer consisting of the anodic oxidation film 9 and the gate insulating layer 10 is formed between the picture element electrode 4 and the additional capacitor electrode 6, so that the picture element electrode 4 and the capacitor electrode 6 constitute an additional capacitor which is connected in parallel to the capacitor caused by the liquid crystal.

- This additional capacitor stores charges when the TFT 5 is ON to drive the picture element electrode 4, and substantially retains the voltage applied to the electrode 4 until the next frame scanning period.

- the picture element electrode 4 is electrically insulated from the capacitor electrode 6 by the dielectric layer consisting of the anodic oxidation film 9 and the gate insulating layer 10. It is often that a pinhole is formed in the dielectric layer due to various reasons such as that a foreign body is mixed into the dielectric layer. In such a case, the picture element electrode 4 disposed on the dielectric layer falls into electrical continuity with the capacitor electrode 6 formed under the dielectric layer. This causes that, when the TFT 5 connected to the picture element electrode 4 is ON, a current leaks from the picture element electrode 4 to the capacitor electrode 6 to cause a display defect. In a conventional active matrix type liquid crystal display device, therefore, the existence of a pinhole in the two-layered structure between the picture element electrode 4 and the additional capacitor electrode 6 causes an inferior production yield.

- the active matrix type liquid crystal display of this invention which overcomes the above-discussed and numerous other disadvantages and deficiencies of the prior art, comprises a substrate on which a plurality of picture element electrodes which are arranged in a matrix, switching elements which are respectively disposed in the vicinity of each of said picture element electrodes, and capacitor electrodes each of which is opposed to at least one portion of each of said picture element electrodes to produce an additional capacitor are formed, wherein a dielectric lamination structure consisting of three insulating layers is formed between said picture element electrode and said capacitor electrode.

- the switching element is a thin film transistor

- the gate electrode of said thin film transistor and said capacitor electrode are disposed on an insulating substrate

- a gate insulating layer is formed on both said gate electrode and said capacitor electrode, said gate insulating layer being one of said three laminated insulating layers.

- the protective insulating layer is formed on both said thin film transistor and said gate insulating layer, said protective insulating being another one of said three laminated insulating layers.

- the anodic oxidation film is formed on said capacitor electrode, said anodic oxidation film being the further one of said three laminated insulating layers.

- the picture element electrode is disposed on said protective insulating layer.

- the picture element electrode is electrically connected to the drain electrode of said TFT, through a contact hole which is formed in said protective insulating layer.

- FIG. 1 A preferred embodiment of the invention is shown in Figs. 1 and 2.

- Figure 2 is a partial plan view of a substrate used in the embodiment

- Fig. 1 is a sectional view taken along line I-I of Fig. 2.

- a plurality of gate bus lines 22 are formed in parallel and horizontally in Fig. 2, and a plurality of source bus lines 23 are formed vertically in the figure.

- a TFT 25 is formed in the vicinity of each intersection of the gate bus lines 22 and source bus lines 23, a TFT 25 is formed.

- Each TFT 25 drives a picture element electrode 34 which is disposed in each region surrounded by two adjacent gate bus lines 22 and source bus lines 23.

- Under the picture element electrode 24, a capacitor electrode 26 is formed.

- a gate electrode 28 of the TFT 25 and a capacitor electrode 26 are formed on the surface of the insulating substrate 27, a gate electrode 28 of the TFT 25 and a capacitor electrode 26 are formed.

- the gate electrode 28 is one part of the gate bus line 22.

- the gate electrode 28 and capacitor electrode 26 can be formed simultaneously, and made of the same material.

- the above-mentioned structure of the preferred embodiment may be the same as that of the device of Fig. 3.

- An anodic oxidation film 29 is formed on each of the gate electrode 28 and capacitor electrode 26, a gate insulating layer 30 is formed on the anodic oxidation films 29 and the remaining surface of the insulating substrate 27.

- an i-a-Si film 31 and n+-a-Si films 33 are laminated on the gate insulating layer 30.

- the n+-a-Si films 33 are electrically separated by an siN x insulating film 32 formed on the i-a-Si film 31.

- a source electrode 34a and a drain electrode 34b are formed on the n+-a-Si films 33, respectively.

- the source electrode 34a and drain electrode 34b are made of the same material as that of the source bus lines 23, and formed simultaneously with the source bus lines 23.

- the structure including the films 31, 32 and 33 and electrodes 28, 34a and 34b constitute the TFT 25.

- One end portion of the drain electrode 34b extends over the gate insulating layer 30.

- a protective insulating layer 35 is formed to cover the TFT 25 and the gate insulating layer 30.

- the picture element electrode 24 is formed on the protective insulating layer 35, and electrically connected to the drain electrode 34b through a contact hole 40 which is formed in the protective insulating layer 35.

- a three-layered dielectric lamination structure consisting of the anodic oxidation film 29, the gate insulating layer 30 and the protective insulating layer 35 is formed between the picture element electrode 24 and the capacitor electrode 26, so that an additional capacitor is formed by these two electrodes 24 and 26 and the three-layered dielectric lamination structure.

- the additional capacitor comprises the three-layered dielectric lamination structure, the insulation between the picture element electrode 24 and the capacitor electrode 26 will not easily fail as compared with that of the prior art which has a two-layered dielectric structure as mentioned above. Therefore, the possibility of producing electrical continuity between the picture element electrode 24 and the capacitor electrode 26 which is caused by a pinhole can be greatly reduced.

- a thin layer of a metal such as Ta, Al, or Ti is deposited in the thickness of 2000-4000 ⁇ by the sputtering or electron beam deposition technique.

- This thin metal film is patterned to form simultaneously the gate electrode 28 and the capacitor electrode 26.

- the surface of the gate electrode 28 and the capacitor electrode 26 is subjected to anodic oxidation to make the anodic oxidation film 29 thereon.

- the thickness of the anodic oxidation film 29 ranges from 1000 ⁇ to 3000 ⁇ .

- SiN x is deposited by a plasma CVD technique to form the gate insulating layer 30 (thickness: 2000 - 5000 ⁇ ), As a result, a two-layered dielectric lamination consisting of the anodic oxidation film 29 and the gate insulating layer 30 is formed.

- a semiconductor film of a-Si and an insulating film of SiN x are successively deposited, and then patterned by the photolithography technique to form the a-Si film 31 and the SiN x insulating film 32.

- a semiconductor film of n+-a-Si is deposited, and then patterned by the photolithography technique to form the n+-a-Si films 33.

- a metal such as Ti, Mo or W is deposited by the sputtering or electron beam deposition technique, and patterned by the photolithography technique to form the source electrode 34a and the drain electrode 34b.

- the protective insulating layer 35 made of SiN x is deposited in the thickness of 2000 - 6000 ⁇ by the plasma CVD technique, and the contact hole 40 is opened in the layer 35 by the photolithography technique. Thereafter, a transparent conductive film which is mainly composed of indium oxide is deposited by the sputtering or electron beam deposition technique, and patterned to form the picture element electrode 24 which is electrically connected to the drain electrode 34b through the contact hole 40.

- the three-layered dielectric lamination structure which consists of the anodic oxidation film 29, the gate insulating layer 30 and the protective insulating layer 35 is disposed between the capacitor electrode 26 and the picture element electrode 24, thereby forming an additional capacitor.

- the protective insulating layer 35 may be made of another insulating material such as SiO2 in place of SiN x .

Landscapes

- Physics & Mathematics (AREA)

- Nonlinear Science (AREA)

- Engineering & Computer Science (AREA)

- Crystallography & Structural Chemistry (AREA)

- Mathematical Physics (AREA)

- Chemical & Material Sciences (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- General Physics & Mathematics (AREA)

- Optics & Photonics (AREA)

- Liquid Crystal (AREA)

- Thin Film Transistor (AREA)

- Liquid Crystal Display Device Control (AREA)

- Devices For Indicating Variable Information By Combining Individual Elements (AREA)

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP20078288A JPH0816756B2 (ja) | 1988-08-10 | 1988-08-10 | 透過型アクティブマトリクス液晶表示装置 |

| JP200782/88 | 1988-08-10 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| EP0376437A2 true EP0376437A2 (de) | 1990-07-04 |

| EP0376437A3 EP0376437A3 (en) | 1990-10-31 |

| EP0376437B1 EP0376437B1 (de) | 1994-12-21 |

Family

ID=16430101

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| EP89308162A Expired - Lifetime EP0376437B1 (de) | 1988-08-10 | 1989-08-10 | Flüssigkristallanzeige mit aktiver Matrix |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US5054887A (de) |

| EP (1) | EP0376437B1 (de) |

| JP (1) | JPH0816756B2 (de) |

| DE (1) | DE68920130T2 (de) |

Cited By (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| EP0466495A3 (en) * | 1990-07-12 | 1992-09-23 | Kabushiki Kaisha Toshiba | Liquid crystal display apparatus |

| EP0604006A3 (de) * | 1992-10-27 | 1994-11-23 | Nec Corp | Flüssigkristallzelle mit aktiver Matrix. |

| FR2737314A1 (fr) * | 1995-07-28 | 1997-01-31 | Thomson Lcd | Procede de fabrication d'une matrice active pour ecran plat, ecran a cristaux liquides comportant une matrice active obtenue selon ledit procede et procede d'adressage d'un tel ecran |

| US8138500B2 (en) | 2008-03-31 | 2012-03-20 | Semiconductor Energy Laboratory Co., Ltd. | Display device |

| US20220115416A1 (en) * | 2019-11-12 | 2022-04-14 | Chengdu Boe Optoelectronics Technology Co., Ltd. | Array substrate, display panel and display device |

Families Citing this family (56)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2620240B2 (ja) | 1987-06-10 | 1997-06-11 | 株式会社日立製作所 | 液晶表示装置 |

| US5231039A (en) * | 1988-02-25 | 1993-07-27 | Sharp Kabushiki Kaisha | Method of fabricating a liquid crystal display device |

| US5225364A (en) * | 1989-06-26 | 1993-07-06 | Oki Electric Industry Co., Ltd. | Method of fabricating a thin-film transistor matrix for an active matrix display panel |

| JP3009438B2 (ja) * | 1989-08-14 | 2000-02-14 | 株式会社日立製作所 | 液晶表示装置 |

| ATE135496T1 (de) * | 1990-03-27 | 1996-03-15 | Canon Kk | Dünnschicht-halbleiterbauelement |

| FR2662290B1 (fr) * | 1990-05-15 | 1992-07-24 | France Telecom | Procede de realisation d'un ecran d'affichage a matrice active et a condensateurs de stockage et ecran obtenu par ce procede. |

| JPH0475034A (ja) * | 1990-07-17 | 1992-03-10 | Sharp Corp | アクティブマトリクス表示装置及びその製造方法 |

| US5153142A (en) * | 1990-09-04 | 1992-10-06 | Industrial Technology Research Institute | Method for fabricating an indium tin oxide electrode for a thin film transistor |

| US5402254B1 (en) * | 1990-10-17 | 1998-09-22 | Hitachi Ltd | Liquid crystal display device with tfts in which pixel electrodes are formed in the same plane as the gate electrodes with anodized oxide films before the deposition of silicon |

| JP3024661B2 (ja) * | 1990-11-09 | 2000-03-21 | セイコーエプソン株式会社 | アクティブマトリクス基板及びその製造方法 |

| US5206749A (en) | 1990-12-31 | 1993-04-27 | Kopin Corporation | Liquid crystal display having essentially single crystal transistors pixels and driving circuits |

| US5666175A (en) * | 1990-12-31 | 1997-09-09 | Kopin Corporation | Optical systems for displays |

| US5528397A (en) | 1991-12-03 | 1996-06-18 | Kopin Corporation | Single crystal silicon transistors for display panels |

| US5362671A (en) * | 1990-12-31 | 1994-11-08 | Kopin Corporation | Method of fabricating single crystal silicon arrayed devices for display panels |

| EP0499979A3 (en) * | 1991-02-16 | 1993-06-09 | Semiconductor Energy Laboratory Co., Ltd. | Electro-optical device |

| JP2873632B2 (ja) | 1991-03-15 | 1999-03-24 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| US6713783B1 (en) | 1991-03-15 | 2004-03-30 | Semiconductor Energy Laboratory Co., Ltd. | Compensating electro-optical device including thin film transistors |

| JPH0572553A (ja) * | 1991-09-11 | 1993-03-26 | Hitachi Ltd | 液晶表示装置およびその製造方法 |

| US6979840B1 (en) * | 1991-09-25 | 2005-12-27 | Semiconductor Energy Laboratory Co., Ltd. | Thin film transistors having anodized metal film between the gate wiring and drain wiring |

| JP2907629B2 (ja) * | 1992-04-10 | 1999-06-21 | 松下電器産業株式会社 | 液晶表示パネル |

| JP3245959B2 (ja) * | 1992-06-05 | 2002-01-15 | 松下電器産業株式会社 | 液晶画像表示装置の製造方法 |

| JPH05341315A (ja) | 1992-06-08 | 1993-12-24 | Hitachi Ltd | 薄膜トランジスタ基板、液晶表示パネルおよび液晶表示装置 |

| US5707746A (en) * | 1992-09-25 | 1998-01-13 | Sharp Kabushiki Kaisha | Thin film transistor device with advanced characteristics by improved matching between a glass substrate and a silicon nitride layer |

| CA2150573A1 (en) * | 1992-12-01 | 1994-06-09 | David Waechter | Thin film transistor having a triple layer dielectric gate insulator, method of fabricating such a thin film transistor and an active matrix display having a plurality of such thin film transistors |

| JP3098345B2 (ja) * | 1992-12-28 | 2000-10-16 | 富士通株式会社 | 薄膜トランジスタマトリクス装置及びその製造方法 |

| DE4339721C1 (de) * | 1993-11-22 | 1995-02-02 | Lueder Ernst | Verfahren zur Herstellung einer Matrix aus Dünnschichttransistoren |

| US5483366A (en) * | 1994-07-20 | 1996-01-09 | David Sarnoff Research Center Inc | LCD with hige capacitance pixel having an ITO active region/poly SI pixel region electrical connection and having poly SI selection line extensions along pixel edges |

| JPH08172202A (ja) * | 1994-12-20 | 1996-07-02 | Sharp Corp | 薄膜トランジスタおよびその製造方法 |

| JP2900229B2 (ja) * | 1994-12-27 | 1999-06-02 | 株式会社半導体エネルギー研究所 | 半導体装置およびその作製方法および電気光学装置 |

| KR0145900B1 (ko) * | 1995-02-11 | 1998-09-15 | 김광호 | 박막 트랜지스터 액정디스플레이 소자 및 그 제조방법 |

| US5834327A (en) | 1995-03-18 | 1998-11-10 | Semiconductor Energy Laboratory Co., Ltd. | Method for producing display device |

| KR100303134B1 (ko) * | 1995-05-09 | 2002-11-23 | 엘지.필립스 엘시디 주식회사 | 액정표시소자및그제조방법. |

| KR100205388B1 (ko) * | 1995-09-12 | 1999-07-01 | 구자홍 | 액정표시장치 및 그 제조방법 |

| JPH09236826A (ja) * | 1995-09-28 | 1997-09-09 | Sharp Corp | 液晶表示素子およびその製造方法 |

| EP1338914A3 (de) * | 1995-11-21 | 2003-11-19 | Samsung Electronics Co., Ltd. | Verfahren zur Herstellung von Flüssigkristallanzeigevorrichtungen |

| KR100190041B1 (ko) * | 1995-12-28 | 1999-06-01 | 윤종용 | 액정표시장치의 제조방법 |

| JP3205501B2 (ja) * | 1996-03-12 | 2001-09-04 | シャープ株式会社 | アクティブマトリクス表示装置およびその修正方法 |

| US6383899B1 (en) | 1996-04-05 | 2002-05-07 | Sharp Laboratories Of America, Inc. | Method of forming polycrystalline semiconductor film from amorphous deposit by modulating crystallization with a combination of pre-annealing and ion implantation |

| JPH1010583A (ja) * | 1996-04-22 | 1998-01-16 | Sharp Corp | アクティブマトリクス基板の製造方法、およびそのアクティブマトリクス基板 |

| KR100209620B1 (ko) * | 1996-08-31 | 1999-07-15 | 구자홍 | 액정 표시 장치 및 그 제조방법 |

| KR100241287B1 (ko) * | 1996-09-10 | 2000-02-01 | 구본준 | 액정표시소자 제조방법 |

| JPH10229197A (ja) * | 1997-02-17 | 1998-08-25 | Sanyo Electric Co Ltd | 薄膜トランジスタ、薄膜トランジスタの製造方法 |

| JP3376379B2 (ja) * | 1997-02-20 | 2003-02-10 | 富士通ディスプレイテクノロジーズ株式会社 | 液晶表示パネル、液晶表示装置及びその製造方法 |

| JP3592535B2 (ja) | 1998-07-16 | 2004-11-24 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| US6124164A (en) * | 1998-09-17 | 2000-09-26 | Micron Technology, Inc. | Method of making integrated capacitor incorporating high K dielectric |

| JP2000275663A (ja) * | 1999-03-26 | 2000-10-06 | Hitachi Ltd | 液晶表示装置とその製造方法 |

| AU6365900A (en) * | 1999-07-21 | 2001-02-13 | E-Ink Corporation | Use of a storage capacitor to enhance the performance of an active matrix drivenelectronic display |

| KR100647775B1 (ko) * | 2004-12-01 | 2006-11-23 | 엘지.필립스 엘시디 주식회사 | 박막 트랜지스터 기판 및 제조 방법 |

| TWI257646B (en) * | 2005-09-05 | 2006-07-01 | Innolux Display Corp | Thin film transistor array substrate and method of manufacturing the same |

| CN101866085B (zh) | 2005-12-26 | 2012-07-25 | 夏普株式会社 | 有源矩阵基板及其缺陷修正方法、显示装置、电视接收机 |

| TWI304655B (en) * | 2006-04-07 | 2008-12-21 | Innolux Display Corp | Thin film transistor and method of manufacturing the same |

| CN100529866C (zh) * | 2006-04-19 | 2009-08-19 | 群康科技(深圳)有限公司 | 液晶显示器制造方法 |

| TWI339303B (en) * | 2006-12-15 | 2011-03-21 | Chimei Innolux Corp | Liquid crystal panel |

| WO2011070901A1 (en) * | 2009-12-11 | 2011-06-16 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and manufacturing method thereof |

| JP5735255B2 (ja) | 2010-10-28 | 2015-06-17 | 株式会社ハイレックスコーポレーション | 係留装置及びそれを用いたステアリング係留機構 |

| TWI422940B (zh) * | 2010-12-16 | 2014-01-11 | Innolux Corp | 陣列基板的形成方法 |

Family Cites Families (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US3671820A (en) * | 1970-04-27 | 1972-06-20 | Rudolph R Haering | High voltage thin-film transistor |

| JPS5922029A (ja) * | 1982-07-28 | 1984-02-04 | Matsushita Electric Ind Co Ltd | マトリクス表示パネルの製造方法 |

| JPS6045219A (ja) * | 1983-08-23 | 1985-03-11 | Toshiba Corp | アクテイブマトリクス型表示装置 |

| GB2169746B (en) * | 1984-11-13 | 1988-09-14 | Sharp Kk | Thin film transistor |

| US4571816A (en) * | 1984-12-11 | 1986-02-25 | Rca Corporation | Method of making a capacitor with standard self-aligned gate process |

| JPS62285464A (ja) * | 1986-06-03 | 1987-12-11 | Matsushita Electric Ind Co Ltd | 薄膜トランジスタアレイ基板及びその製造方法 |

| EP0288011A3 (de) * | 1987-04-20 | 1991-02-20 | Hitachi, Ltd. | Flüssigkristallanzeigeeinrichtung und Steuerungsverfahren dafür |

| JPH01291467A (ja) * | 1988-05-19 | 1989-11-24 | Toshiba Corp | 薄膜トランジスタ |

| JP3351026B2 (ja) * | 1993-06-04 | 2002-11-25 | 松下電器産業株式会社 | 電気湯沸かし器 |

-

1988

- 1988-08-10 JP JP20078288A patent/JPH0816756B2/ja not_active Expired - Lifetime

-

1989

- 1989-08-09 US US07/391,244 patent/US5054887A/en not_active Expired - Lifetime

- 1989-08-10 EP EP89308162A patent/EP0376437B1/de not_active Expired - Lifetime

- 1989-08-10 DE DE68920130T patent/DE68920130T2/de not_active Expired - Fee Related

Cited By (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| EP0466495A3 (en) * | 1990-07-12 | 1992-09-23 | Kabushiki Kaisha Toshiba | Liquid crystal display apparatus |

| US5187602A (en) * | 1990-07-12 | 1993-02-16 | Kabushiki Kaisha Toshiba | Liquid crystal display apparatus |

| EP0604006A3 (de) * | 1992-10-27 | 1994-11-23 | Nec Corp | Flüssigkristallzelle mit aktiver Matrix. |

| US5499123A (en) * | 1992-10-27 | 1996-03-12 | Nec Corporation | Active matrix liquid crystal display cell with light blocking capacitor electrode above insulating layer |

| FR2737314A1 (fr) * | 1995-07-28 | 1997-01-31 | Thomson Lcd | Procede de fabrication d'une matrice active pour ecran plat, ecran a cristaux liquides comportant une matrice active obtenue selon ledit procede et procede d'adressage d'un tel ecran |

| WO1997005656A1 (fr) * | 1995-07-28 | 1997-02-13 | Thomson-Lcd | Procede de fabrication d'une matrice active pour ecran plat, ecran a cristaux liquides comportant une matrice active obtenue selon ledit procede et procede d'adressage d'un tel ecran |

| US8138500B2 (en) | 2008-03-31 | 2012-03-20 | Semiconductor Energy Laboratory Co., Ltd. | Display device |

| US8519398B2 (en) | 2008-03-31 | 2013-08-27 | Semiconductor Energy Laboratory Co., Ltd. | Display device |

| US20220115416A1 (en) * | 2019-11-12 | 2022-04-14 | Chengdu Boe Optoelectronics Technology Co., Ltd. | Array substrate, display panel and display device |

| US12027537B2 (en) * | 2019-11-12 | 2024-07-02 | Chengdu Boe Optoelectronics Technology Co., Ltd. | Array substrate, display panel and display device |

Also Published As

| Publication number | Publication date |

|---|---|

| EP0376437B1 (de) | 1994-12-21 |

| DE68920130D1 (de) | 1995-02-02 |

| US5054887A (en) | 1991-10-08 |

| JPH0248639A (ja) | 1990-02-19 |

| JPH0816756B2 (ja) | 1996-02-21 |

| DE68920130T2 (de) | 1995-06-22 |

| EP0376437A3 (en) | 1990-10-31 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US5054887A (en) | Active matrix type liquid crystal display | |

| US4759610A (en) | Active matrix display with capacitive light shield | |

| EP0464579B1 (de) | Dünnfilm-Feldeffekt-Transistormatrix zur Verwendung in Flüssigkristallanzeigen mit aktiver Matrix | |

| US6075580A (en) | Active matrix type liquid crystal display apparatus with conductive light shield element | |

| US5162901A (en) | Active-matrix display device with added capacitance electrode wire and secondary wire connected thereto | |

| US5504348A (en) | Thin-film transistor array and liquid crystal display device using the thin-film transistor array | |

| JP3708637B2 (ja) | 液晶表示装置 | |

| US4935792A (en) | Thin film transistor array | |

| US5498573A (en) | Method of making multi-layer address lines for amorphous silicon liquid crystal display devices | |

| EP0301571B1 (de) | Dünnschichttransistoren-Matrix | |

| KR100260359B1 (ko) | 액정 표시 장치 및 그 제조방법 | |

| JPH07128685A (ja) | 液晶表示装置 | |

| US5734448A (en) | LCD having a capacitor with two lower capacitor electrodes and a reflective pixel electrode serving as an upper electrode | |

| US5155564A (en) | Thin-film transistor array | |

| JPH07113728B2 (ja) | アクティブマトリクス基板 | |

| JP3819590B2 (ja) | 液晶表示素子ならびに該素子を用いた液晶表示装置、および反射型液晶表示装置 | |

| JPH03196020A (ja) | 液晶表示装置 | |

| JPH0820641B2 (ja) | 液晶表示装置の製造方法 | |

| JPH10335671A (ja) | ドライバーモノリシック駆動素子 | |

| JPH0915623A (ja) | 液晶表示装置およびその製造方法 | |

| JPH04338728A (ja) | アクティブマトリクス基板 | |

| JP2687967B2 (ja) | 液晶表示装置 | |

| JPH0340511B2 (de) | ||

| JPH06326310A (ja) | アクティブマトリクス型表示装置 | |

| JP2538523B2 (ja) | 液晶マトリクスパネルの製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| PUAI | Public reference made under article 153(3) epc to a published international application that has entered the european phase |

Free format text: ORIGINAL CODE: 0009012 |

|

| AK | Designated contracting states |

Kind code of ref document: A2 Designated state(s): DE FR GB NL |

|

| PUAL | Search report despatched |

Free format text: ORIGINAL CODE: 0009013 |

|

| AK | Designated contracting states |

Kind code of ref document: A3 Designated state(s): DE FR GB NL |

|

| 17P | Request for examination filed |

Effective date: 19901228 |

|

| 17Q | First examination report despatched |

Effective date: 19930303 |

|

| GRAA | (expected) grant |

Free format text: ORIGINAL CODE: 0009210 |

|

| AK | Designated contracting states |

Kind code of ref document: B1 Designated state(s): DE FR GB NL |

|

| REF | Corresponds to: |

Ref document number: 68920130 Country of ref document: DE Date of ref document: 19950202 |

|

| ET | Fr: translation filed | ||

| PLBE | No opposition filed within time limit |

Free format text: ORIGINAL CODE: 0009261 |

|

| STAA | Information on the status of an ep patent application or granted ep patent |

Free format text: STATUS: NO OPPOSITION FILED WITHIN TIME LIMIT |

|

| 26N | No opposition filed | ||

| PGFP | Annual fee paid to national office [announced via postgrant information from national office to epo] |

Ref country code: DE Payment date: 20010806 Year of fee payment: 13 |

|

| PGFP | Annual fee paid to national office [announced via postgrant information from national office to epo] |

Ref country code: GB Payment date: 20010808 Year of fee payment: 13 |

|

| PGFP | Annual fee paid to national office [announced via postgrant information from national office to epo] |

Ref country code: FR Payment date: 20010810 Year of fee payment: 13 |

|

| PGFP | Annual fee paid to national office [announced via postgrant information from national office to epo] |

Ref country code: NL Payment date: 20010830 Year of fee payment: 13 |

|

| REG | Reference to a national code |

Ref country code: GB Ref legal event code: IF02 |

|

| PG25 | Lapsed in a contracting state [announced via postgrant information from national office to epo] |

Ref country code: GB Free format text: LAPSE BECAUSE OF NON-PAYMENT OF DUE FEES Effective date: 20020810 |

|

| PG25 | Lapsed in a contracting state [announced via postgrant information from national office to epo] |

Ref country code: NL Free format text: LAPSE BECAUSE OF NON-PAYMENT OF DUE FEES Effective date: 20030301 Ref country code: DE Free format text: LAPSE BECAUSE OF NON-PAYMENT OF DUE FEES Effective date: 20030301 |

|

| GBPC | Gb: european patent ceased through non-payment of renewal fee |

Effective date: 20020810 |

|

| PG25 | Lapsed in a contracting state [announced via postgrant information from national office to epo] |

Ref country code: FR Free format text: LAPSE BECAUSE OF NON-PAYMENT OF DUE FEES Effective date: 20030430 |

|

| NLV4 | Nl: lapsed or anulled due to non-payment of the annual fee |

Effective date: 20030301 |

|

| REG | Reference to a national code |

Ref country code: FR Ref legal event code: ST |